# Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение высшего образования ПЕРМСКИЙ НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

На правах рукописи

Васенин Иван Андреевич

## ЭЛЕМЕНТЫ ПЛИС С ИСПОЛЬЗОВАНИЕМ КОМБИНИРОВАННОГО КОДИРОВАНИЯ

2.3.2. Вычислительные системы и их элементы

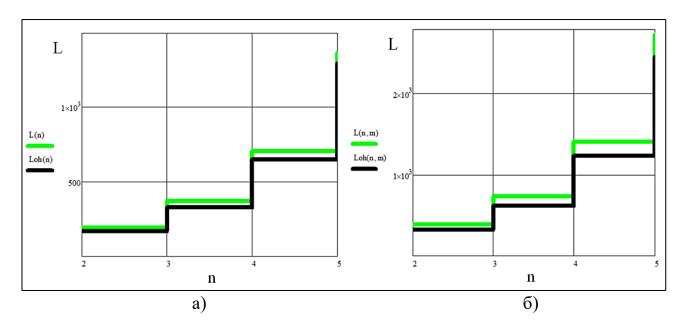

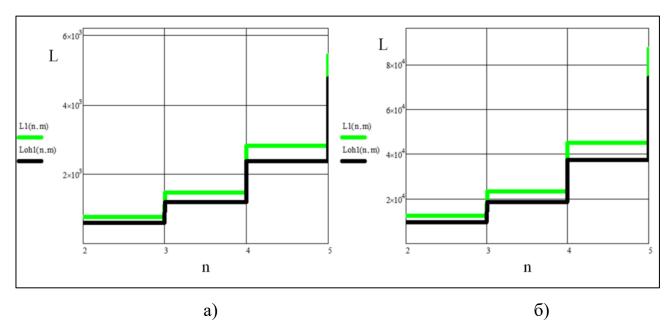

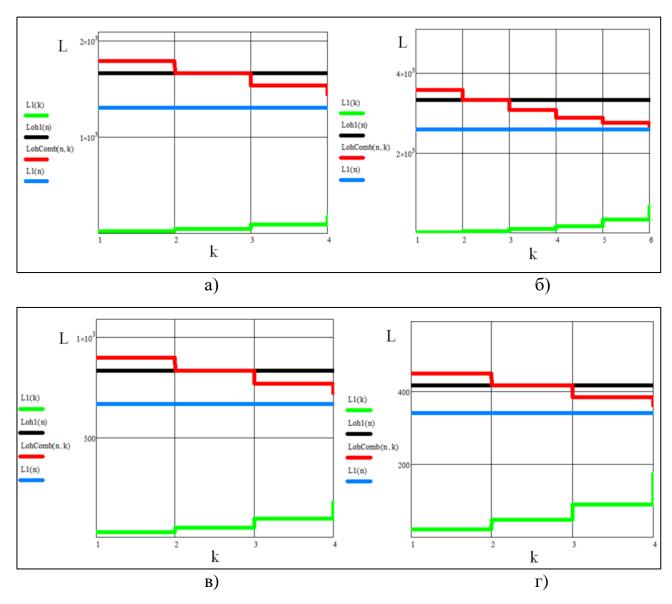

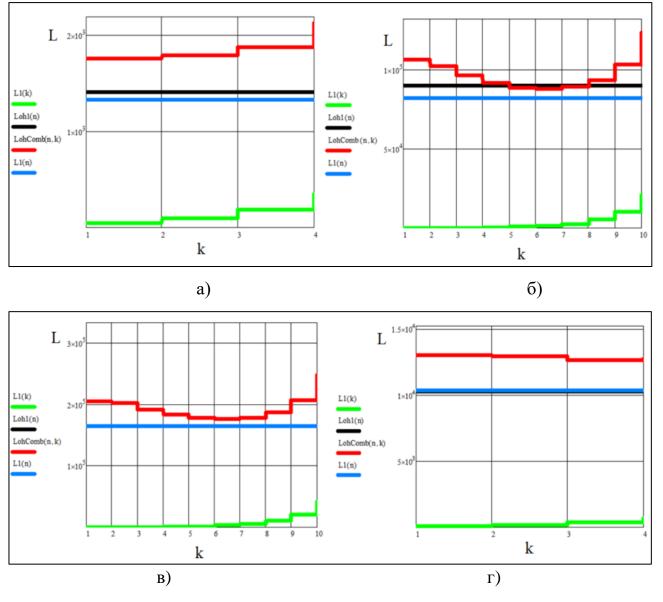

ДИССЕРТАЦИЯ

на соискание ученой степени кандидата технических наук

Научный руководитель: доктор технических наук, профессор, Тюрин С. Ф.

## СОДЕРЖАНИЕ

| ВВЕДЕНИЕ7                                                                           |

|-------------------------------------------------------------------------------------|

| ГЛАВА 1. АКТУАЛЬНОСТЬ И АНАЛИЗ ОБЪЕКТА И ПРЕДМЕТА                                   |

| ИССЛЕДОВАНИЯ. ПОСТАНОВКА ЗАДАЧИ ИССЛЕДОВАНИЯ14                                      |

| 1.1 Обзор и анализ объекта исследования – элементов ПЛИС. Противоречие              |

| в практике                                                                          |

| 1.1.1 Анализ современных ПЛИС                                                       |

| 1.1.2 Анализ логического элемента FPGA и элемента – коммутатора                     |

| межсоединений16                                                                     |

| 1.2 Анализ предмета исследования – научно-методического аппарата синтеза            |

| – элементов ПЛИС. Противоречие в науке                                              |

| 1.2.1 Анализ публикаций по научно-методическому аппарату синтеза                    |

| элементов ПЛИС                                                                      |

| 1.2.2 Исследование направления создания элементов с комбинированным                 |

| кодированием переменных или настройки25                                             |

| 1.3 Математическая постановка задачи и частных задач исследования 35                |

| 1.4 Выводы по главе 1                                                               |

| ГЛАВА 2. РАЗРАБОТКА МАТЕМАТИЧЕСКОЙ МОДЕЛИ, МЕТОДА И                                 |

| АЛГОРИТМА СИНТЕЗА ЭЛЕМЕНТОВ ПЛИС ТИПА FPGA C                                        |

| ИСПОЛЬЗОВАНИЕМ КОМБИНИРОВАННОГО КОДИРОВАНИЯ39                                       |

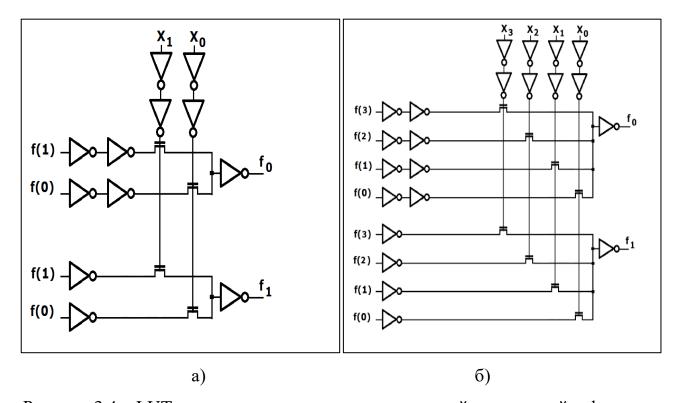

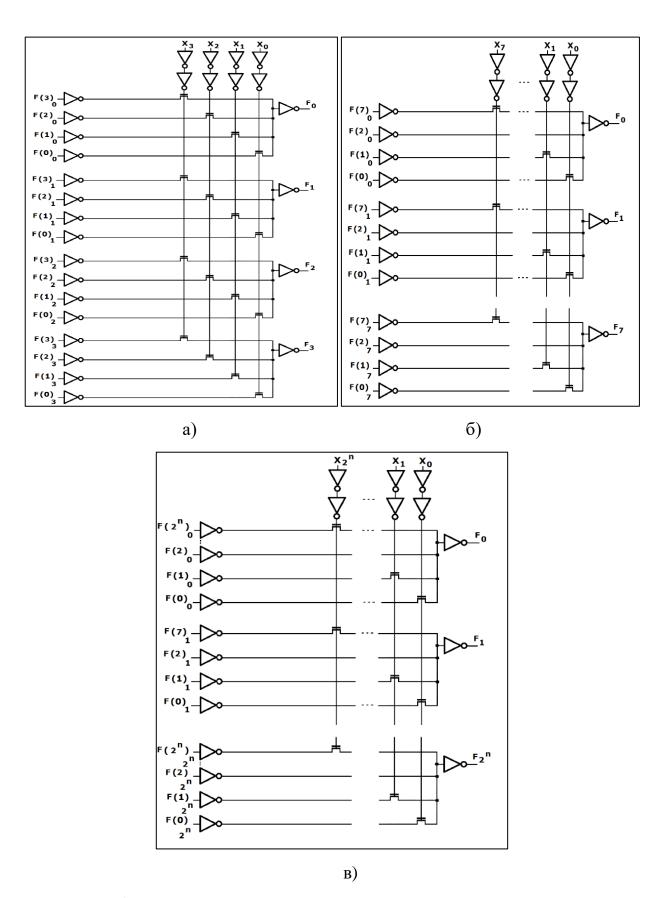

| 2.1 Модель элемента LUT <sub>роз</sub> с бинарным (позиционным) кодированием        |

| входных переменных или настройки                                                    |

| 2.2 Модель элемента LUT <sub>оh</sub> , использующего унитарное кодирование входных |

| переменных или настройки                                                            |

| 2.3 Разработка модели предлагаемого комбинированного элемента48                     |

| 2.4 Разработка метода синтеза элементов ПЛИС типа FPGA с                            |

| использованием комбинированного кодирования53                                       |

| 2                                                                                   |

| 2.4.1 Синтез унитарных блоков                                                                 |

|-----------------------------------------------------------------------------------------------|

| 2.4.2 Синтез $j$ позиционных блоков                                                           |

| 2.4.3 Соединение позиционных и унитарных блоков                                               |

| 2.5 Алгоритм и программа синтеза элемента с комбинированным                                   |

| кодированием                                                                                  |

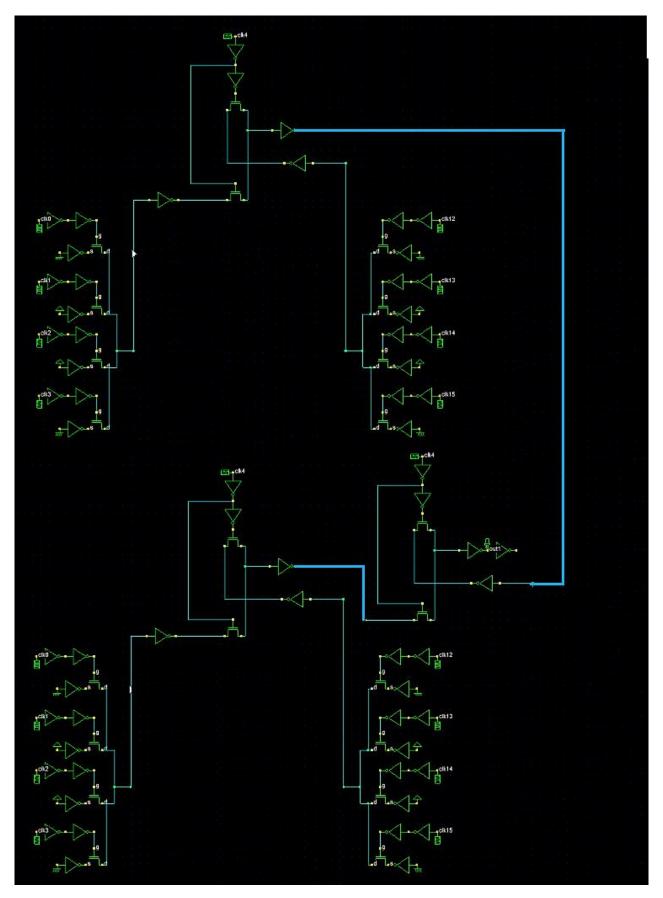

| 2.6 Разработка универсального элемента с конфигурируемым кодированием                         |

| переменной                                                                                    |

|                                                                                               |

| ГЛАВА 3. РАЗРАБОТКА СХЕМ ЭЛЕКТРИЧЕСКИХ ФУНКЦИОНАЛЬНЫХ ПРЕДЛАГАЕМЫХ ЭЛЕМЕНТОВ С ИСПОЛЬЗОВАНИЕМ |

| КОМБИНИРОВАННОГО КОДИРОВАНИЯ68                                                                |

|                                                                                               |

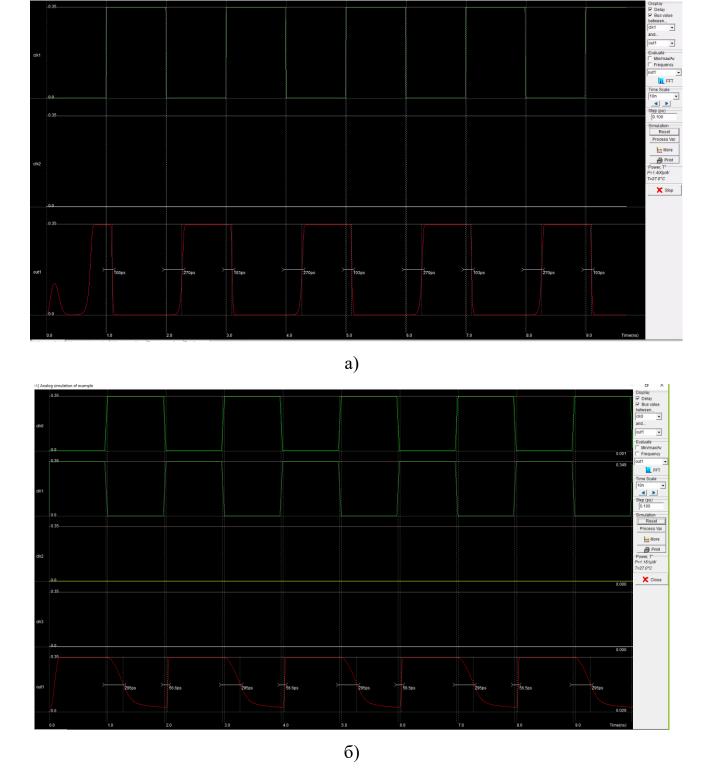

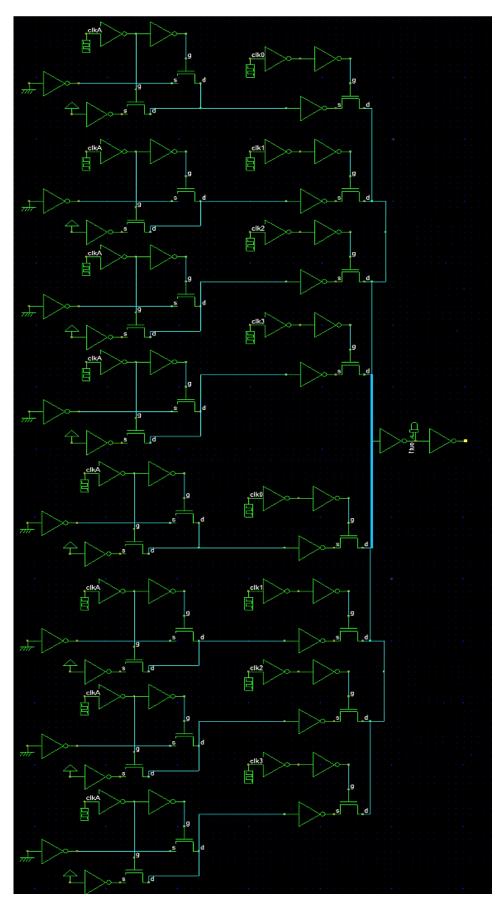

| 3.1 Разработка схем электрических функциональных различных                                    |

| предлагаемых вариантов логических элементов LUT с использованием                              |

| унитарного кодирования68                                                                      |

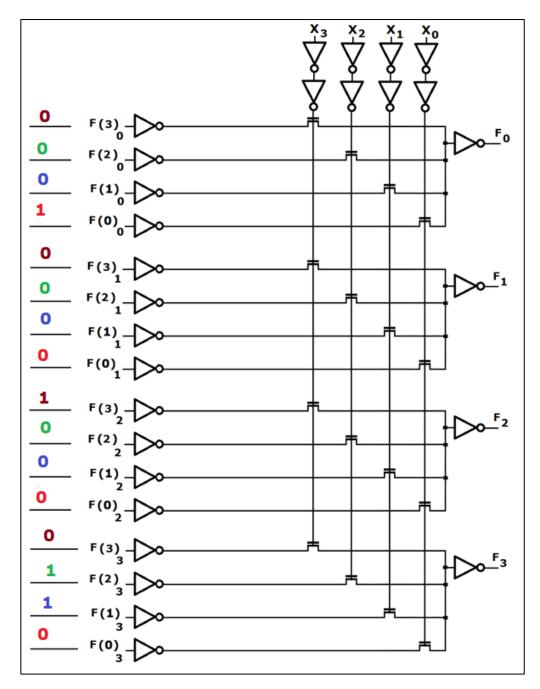

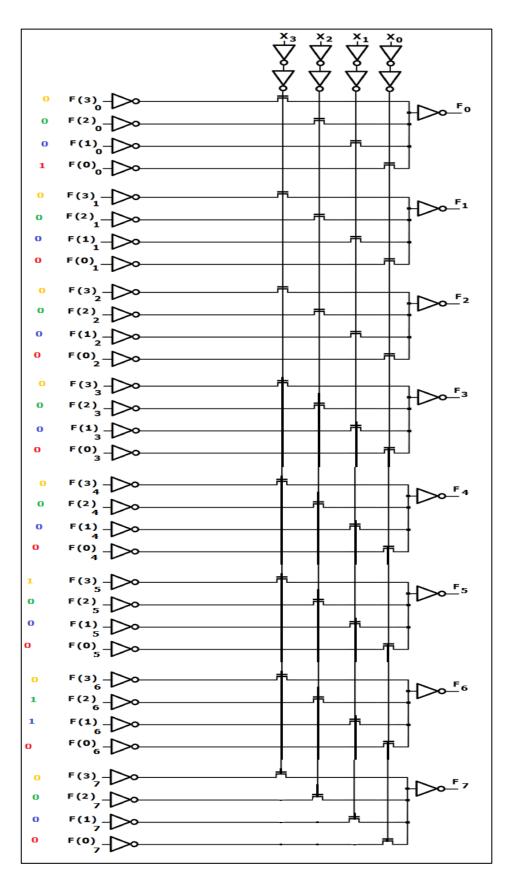

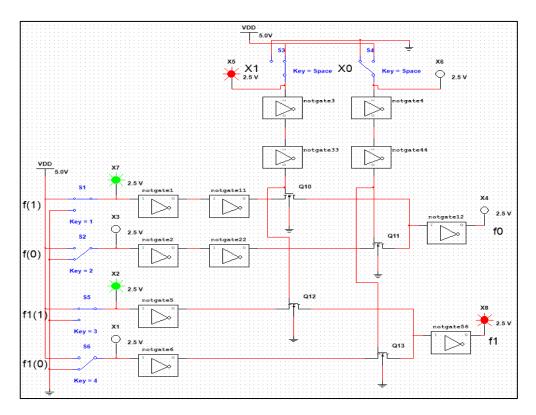

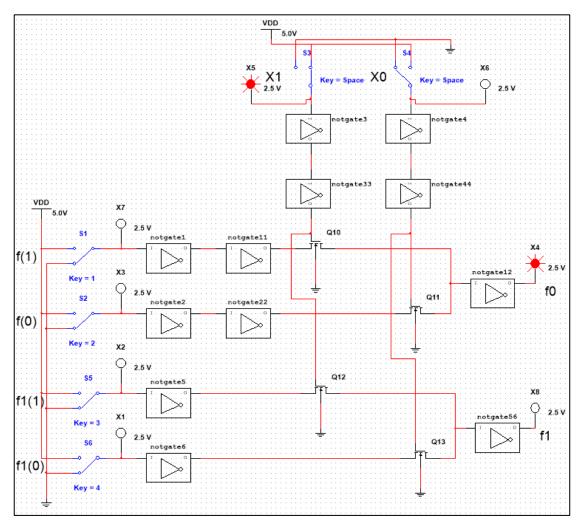

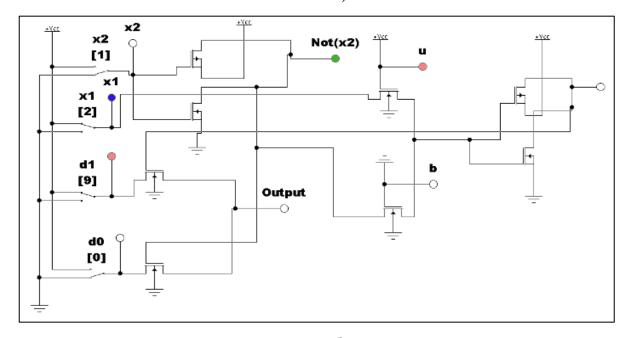

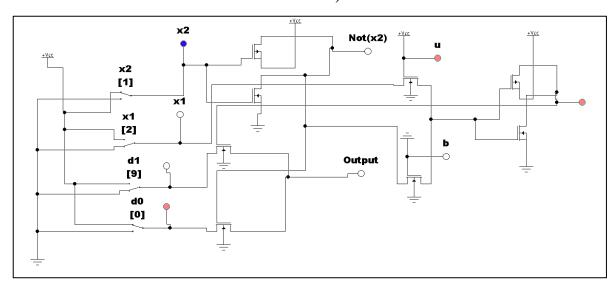

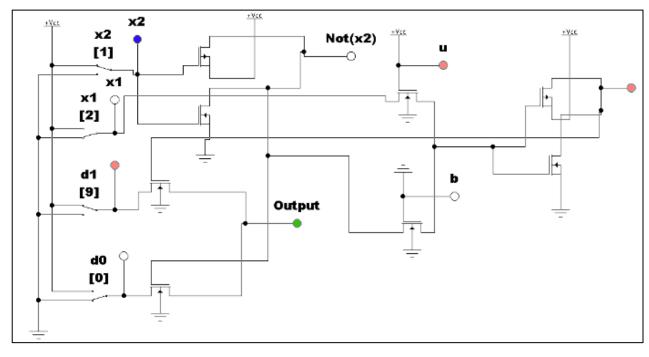

| 3.2 Примеры настройки предлагаемых логических элементов LUT <sub>uc</sub> на две              |

| переменные при реализации системы двух функций72                                              |

| 3.3 Пример электрических функциональных схем кодопреобразователей в                           |

| унитарный код из позиционного и наоборот; построение сумматора                                |

| унитарных кодов76                                                                             |

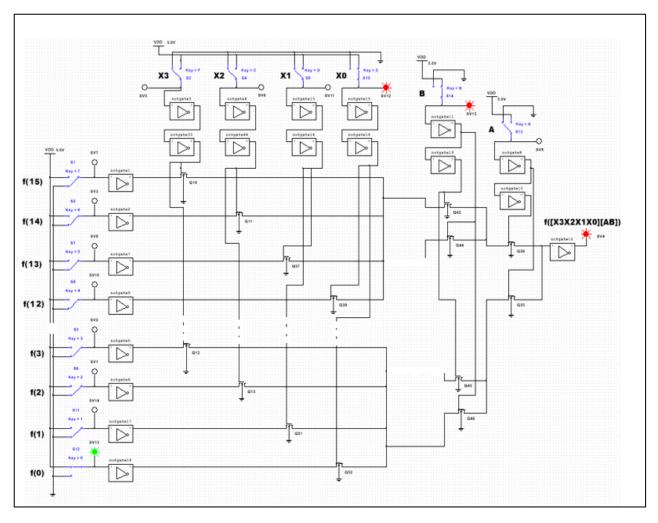

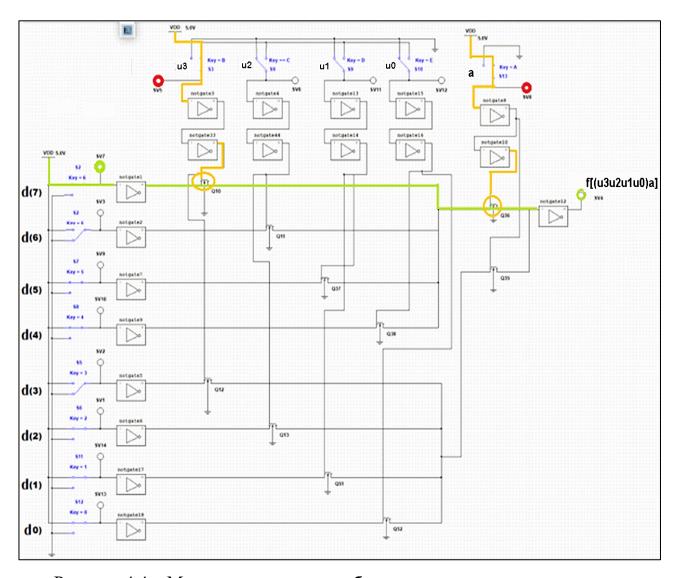

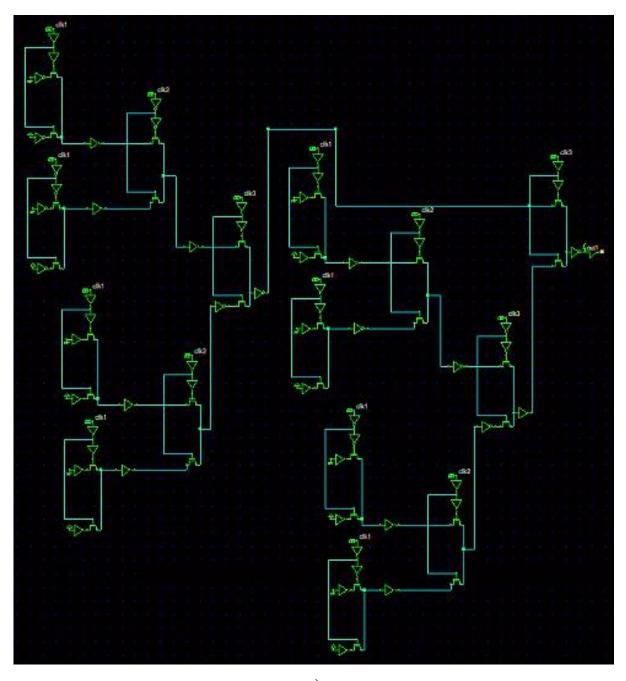

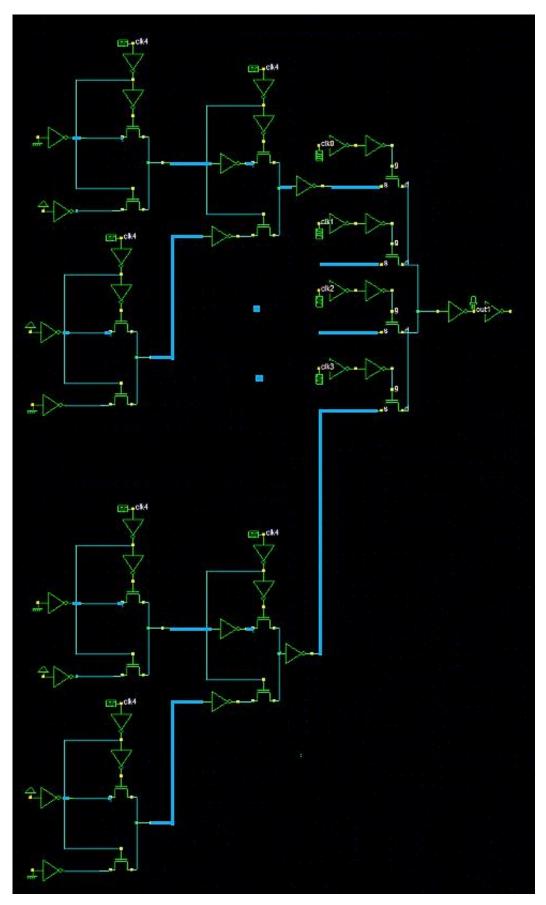

| 3.4 Пример реализации логических функций автоматов в ПЛИС типа FPGA с                         |

| использованием комбинированного кодирования79                                                 |

| 3.5 Синтез функциональных электрических схем по предлагаемому методу 87                       |

| 3.6 Разработка схемы электрической функциональной универсального                              |

| элемента с конфигурируемым кодированием переменной91                                          |

| 3.7 Выводы по главе 397                                                                       |

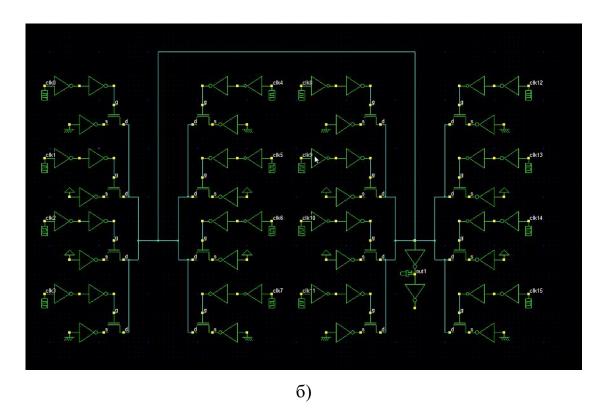

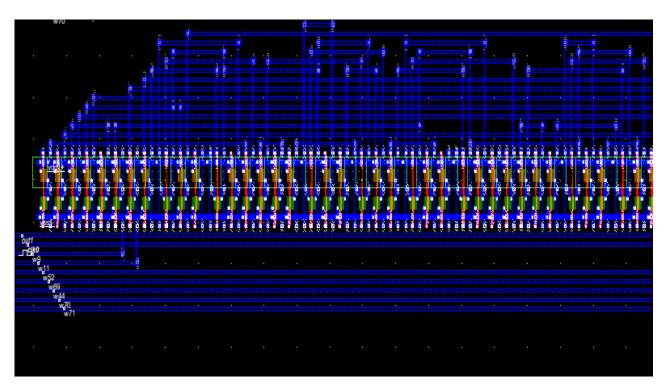

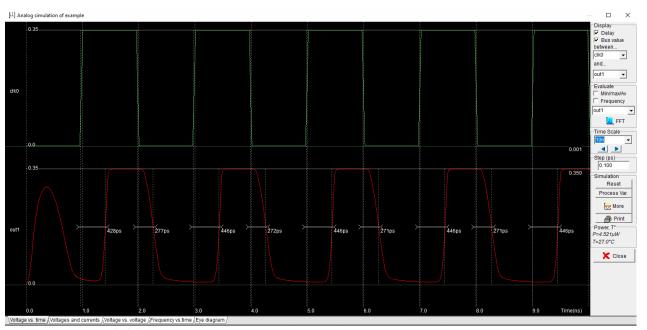

| ГЛАВА 4. ИССЛЕДОВАНИЕ ЭЛЕКТРИЧЕСКИХ ПРИНЦИПИАЛЬНЫХ                                            |

| СХЕМ ПРЕДЛОЖЕННЫХ ЭЛЕМЕНТОВ В СИСТЕМАХ                                                        |

| СХЕМОТЕХНИЧЕСКОГО И ТОПОЛОГИЧЕСКОГО МОДЕЛИРОВАНИЯ 98                                          |

| 4.1 Моделирование электрических принципиальных схем предложенных     |

|----------------------------------------------------------------------|

| элементов в системе схемотехнического моделирования Multisim фирмы   |

| National Instruments98                                               |

| 4.2 Моделирование универсального элемента с конфигурируемым          |

| кодированием переменной в системе схемотехнического моделирования    |

| Multisim фирмы National Instruments103                               |

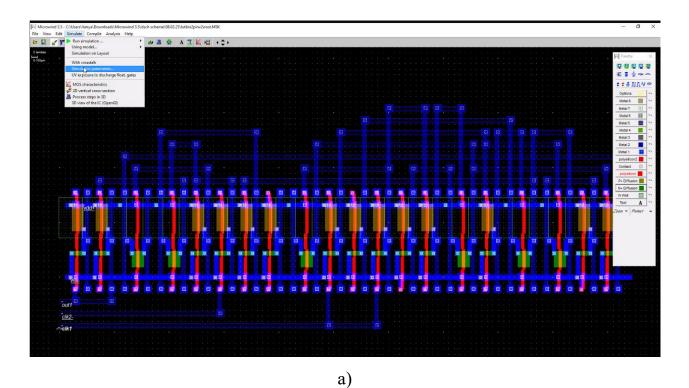

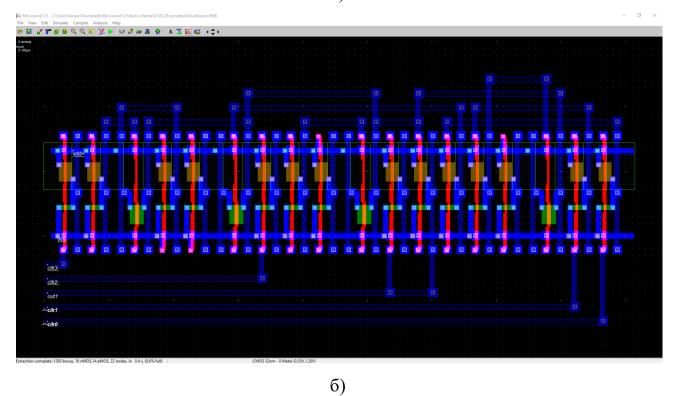

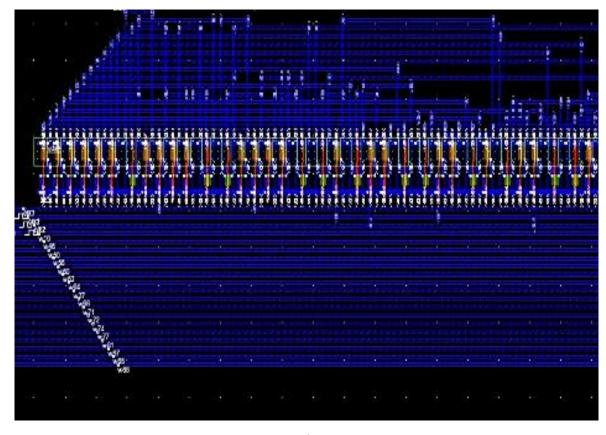

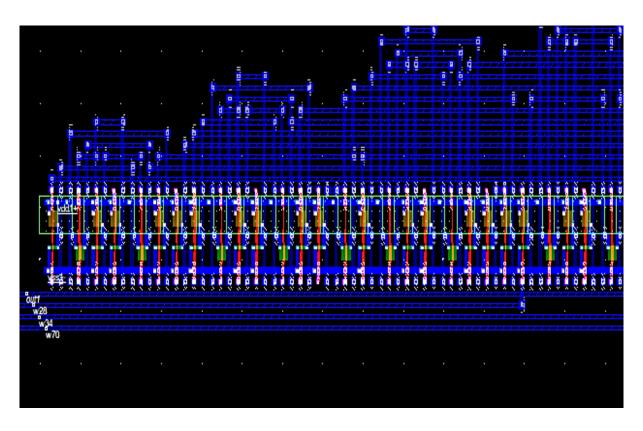

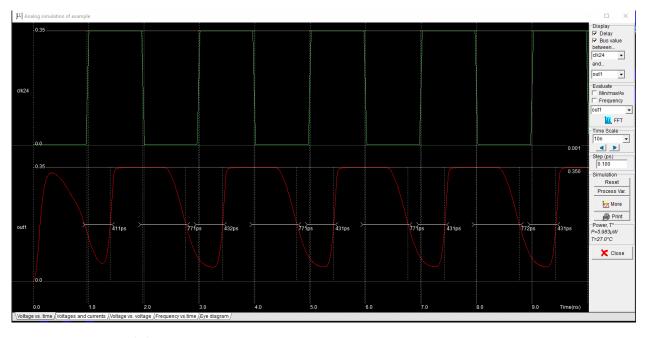

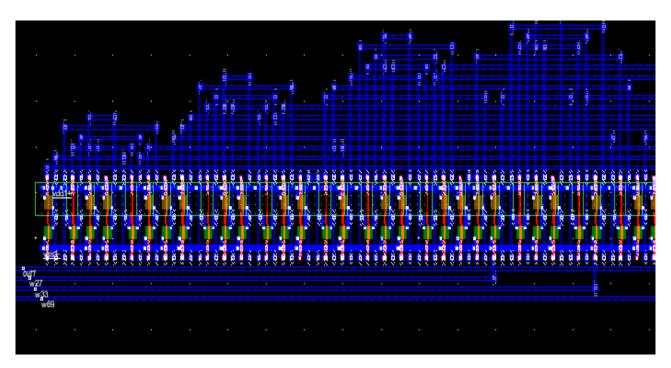

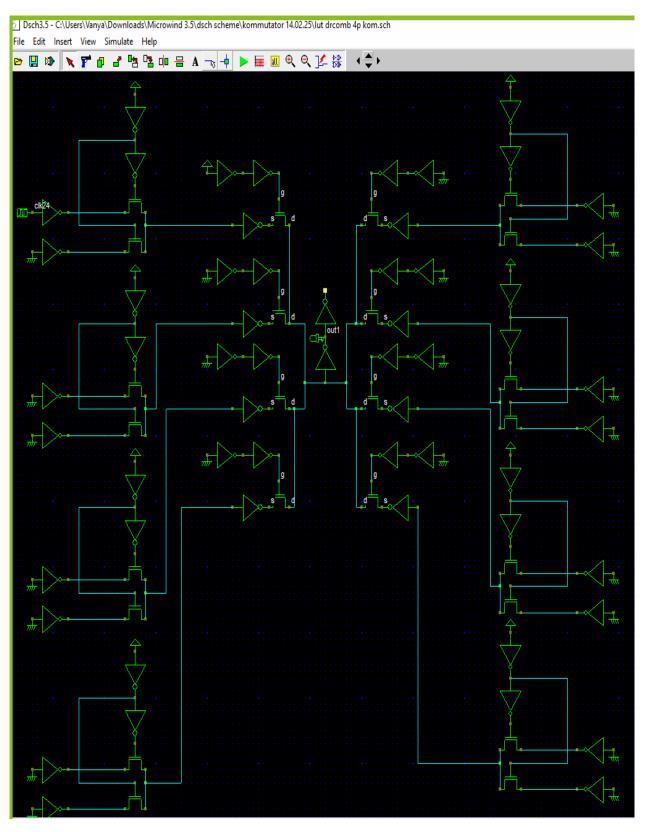

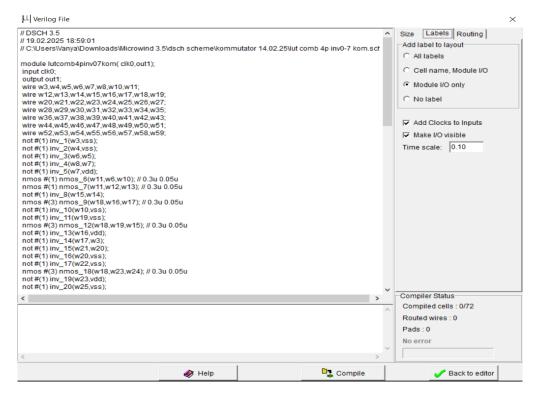

| 4.3 Моделирование в системе топологического моделирования Microwind  |

| элементов для вычисления заданной логической функции106              |

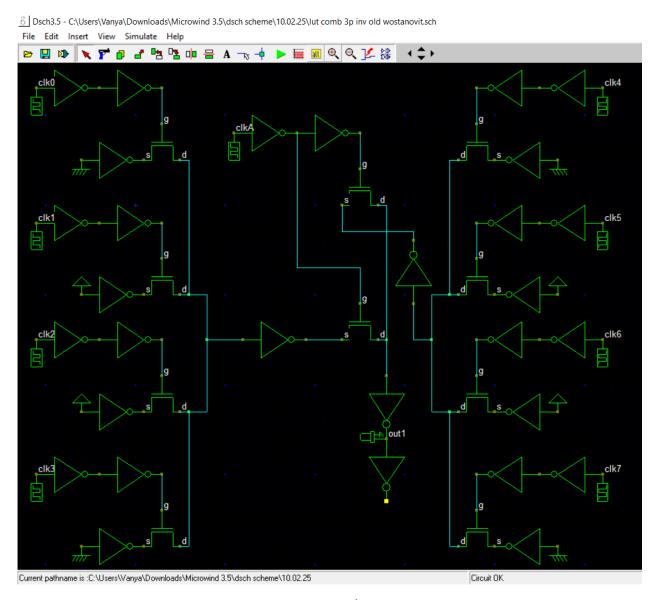

| 4.3.1 Моделирование в Microwind известного элемента для вычисления   |

| логической функции на одну переменную                                |

| 4.3.2 Моделирование в Microwind известного элемента для вычисления   |

| логической функции на две переменные                                 |

|                                                                      |

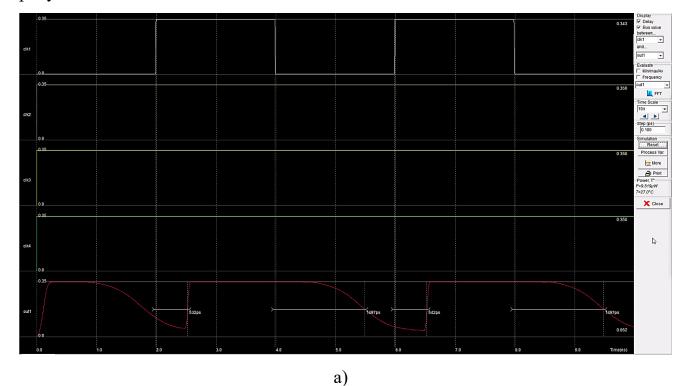

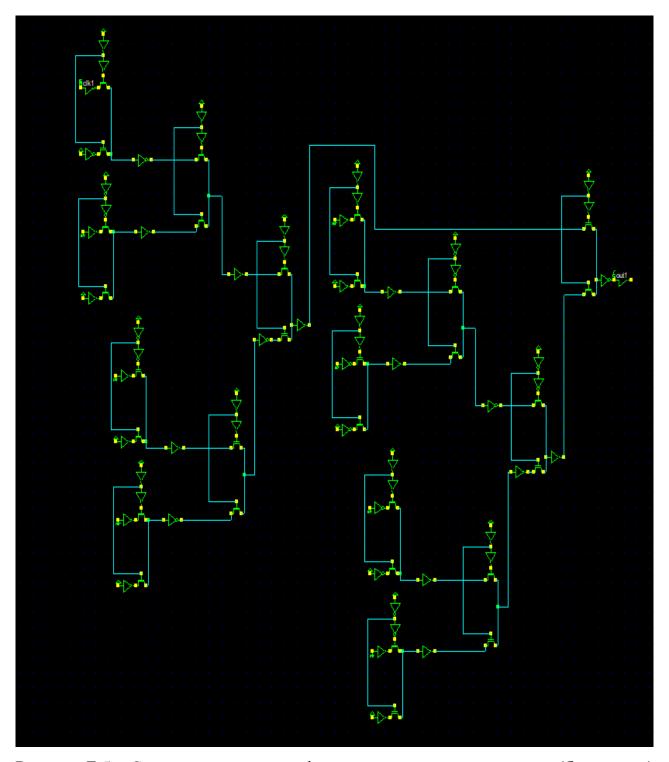

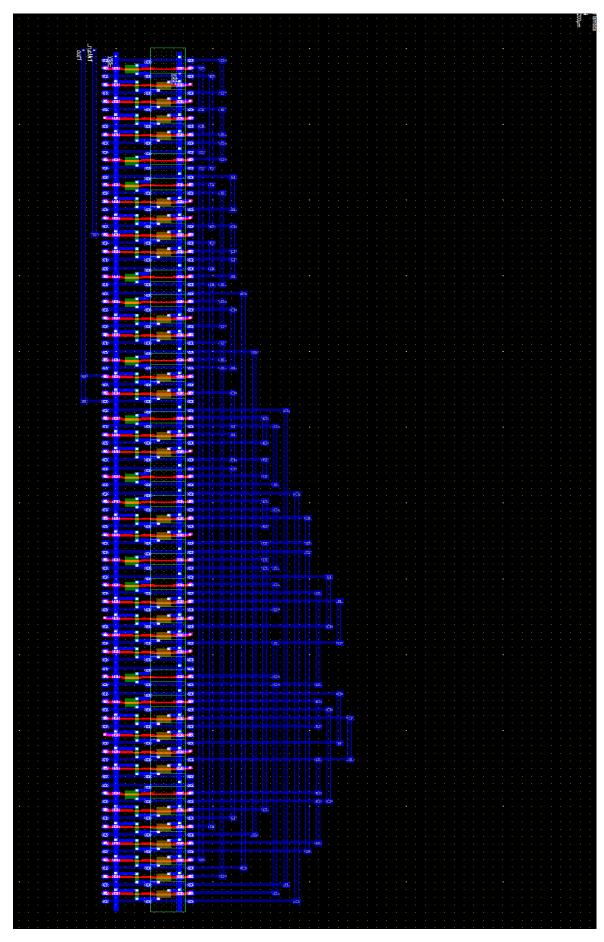

| 4.3.4 Моделирование в Microwind элемента для вычисления логической   |

| функции на четыре переменные                                         |

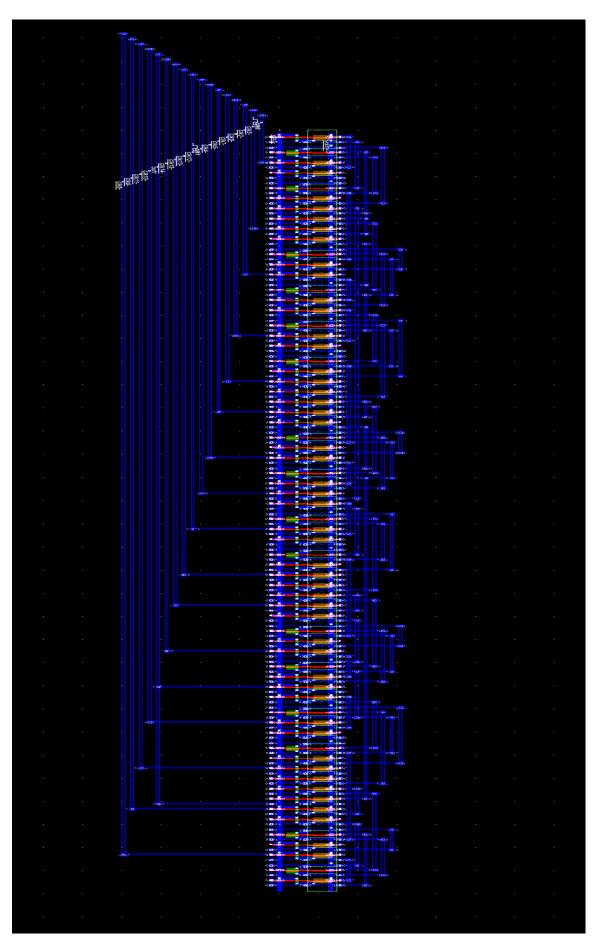

| 4.3.5 Моделирование в Microwind предложенного комбинированного       |

| элемента для вычисления логической функции на три переменные 123     |

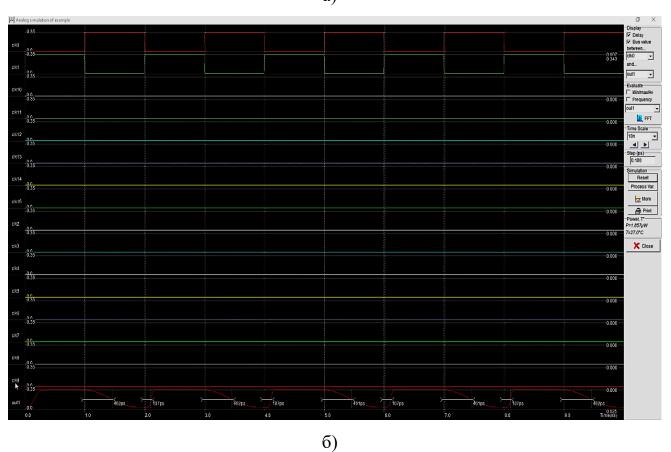

| 4.3.6 Моделирование в Microwind предложенного комбинированного       |

| элемента для вычисления логической функции на четыре переменные 127  |

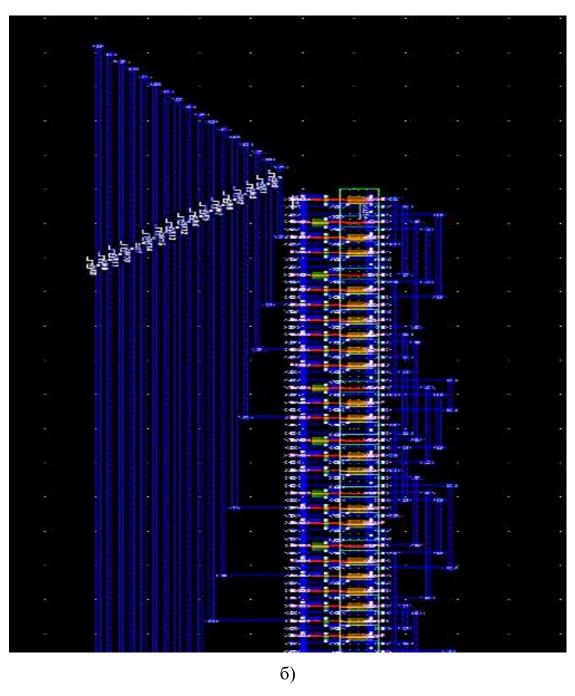

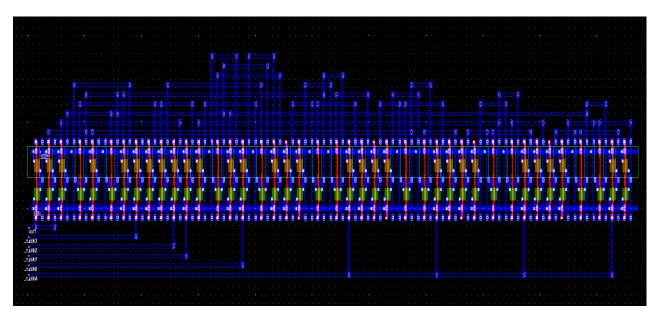

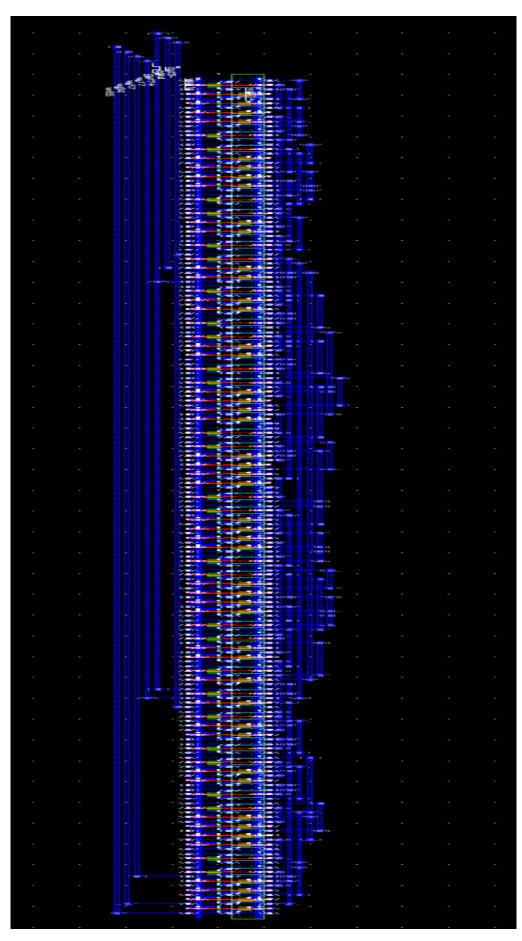

| 4.4 Моделирование в системе топологического моделирования Microwind  |

| элементов для коммутации сигналов137                                 |

| 4.4.1 Моделирование в Microwind элементов для коммутации сигналов на |

| одну переменную                                                      |

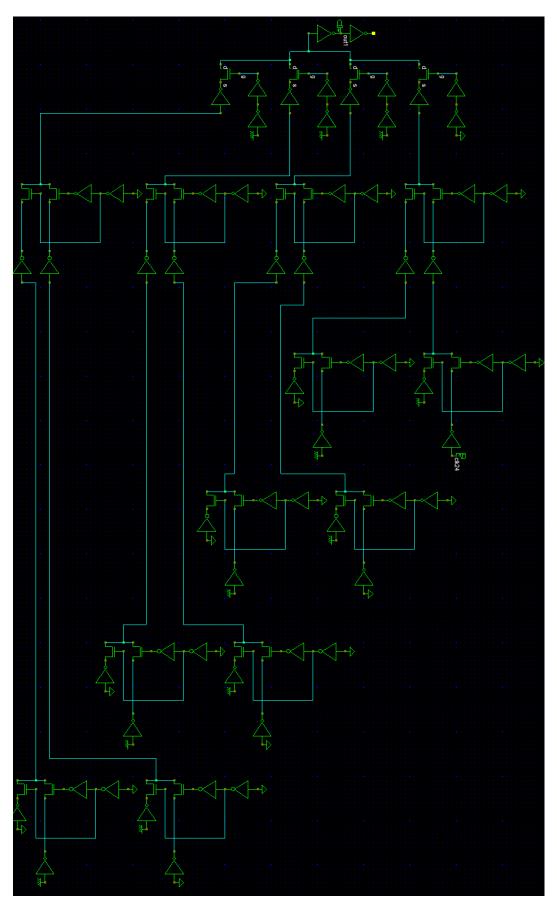

| 4.4.2 Моделирование в Microwind элементов для коммутации сигналов на |

| две переменные                                                       |

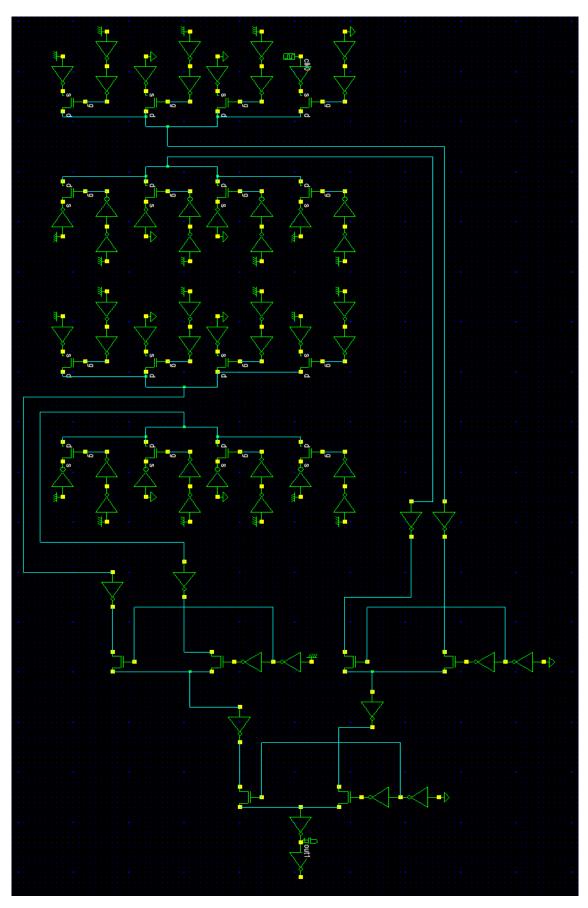

| 4.4.3 Моделирование в Microwind элементов для коммутации сигналов на |

| три переменные                                                       |

| 4.4.4 Моделирование в Microwind элементов для коммутации сигналов на                           |

|------------------------------------------------------------------------------------------------|

| четыре переменные                                                                              |

| 4.5 Выводы по главе 4                                                                          |

| ГЛАВА 5. ОЦЕНКА ЭФФЕКТИВНОСТИ РЕАЛИЗАЦИИ ЭЛЕМЕНТА,                                             |

| ИСПОЛЬЗУЮЩЕГО КОМБИНИРОВАННОЕ КОДИРОВАНИЕ149                                                   |

| 5.1 Сравнительные оценки сложности реализации предлагаемого элемента в количестве транзисторов |

| 5.2 Сравнение двух вариантов реализации комбинированного элемента в                            |

| зависимости от расположения $n_1, n_2$                                                         |

| 5.3 Оценка увеличения числа связей и конфигурационной памяти 165                               |

| 5.4 Сравнение показателей с учетом результатов топологического                                 |

| моделирования в системе Microwind                                                              |

| ЗАКЛЮЧЕНИЕ177                                                                                  |

| Список сокращений179                                                                           |

| Библиографический список181                                                                    |

| ПРИЛОЖЕНИЕ А Программа синтеза схем с использованием двух видов                                |

| кодирования для получения комбинированных схем с помощью универсальных                         |

| блоков                                                                                         |

| ПРИЛОЖЕНИЕ Б Моделирование в системе MicroWind202                                              |

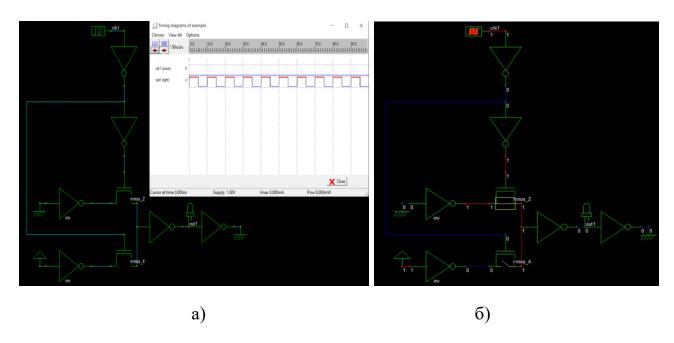

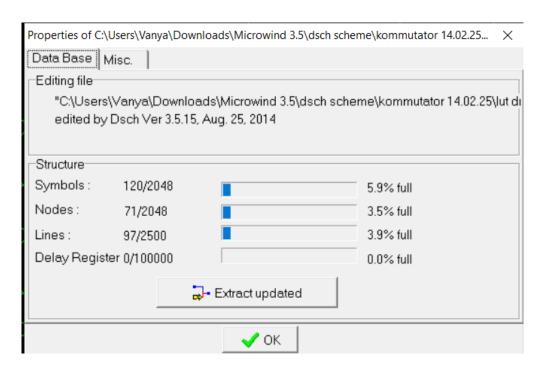

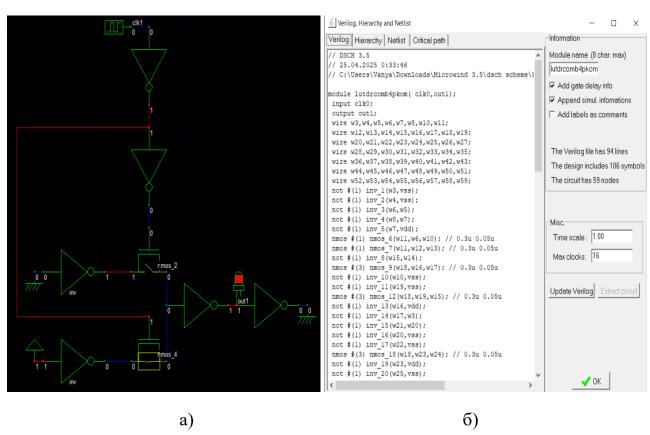

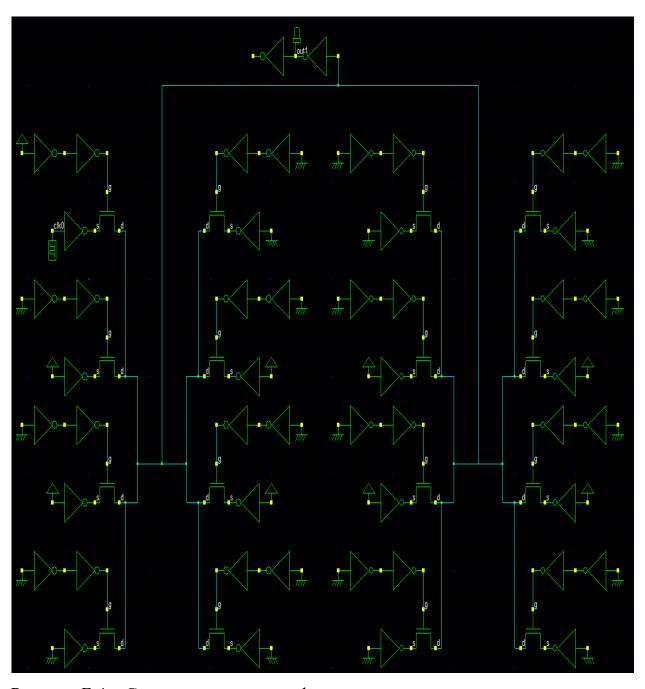

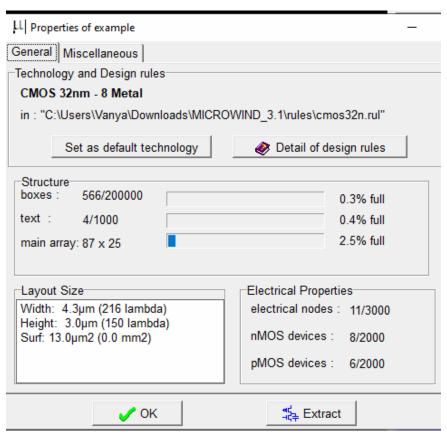

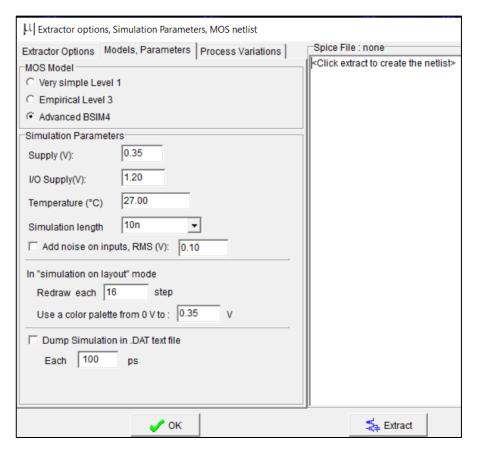

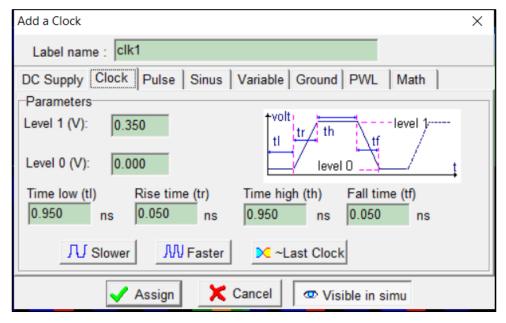

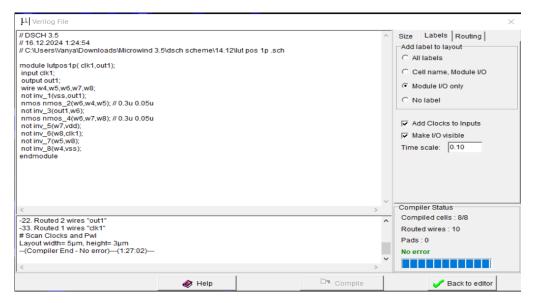

| 1. Моделирование схем электрических функциональных в системе DSCH 202                          |

| 2. Настройки для моделирования схем в MicroWind                                                |

| 3. Получение топологий схем                                                                    |

| ПРИЛОЖЕНИЕ В Акты о внедрении                                                                  |

| 1. Акт о внедрении результатов диссертационного исследования в учебный                         |

| процесс кафедры «Автоматика и Телемеханика»                                                    |

| 2. | Акт    | o   | внедрении    | результато     | в дис | ссертацион | НОГО  | исследования | В         | 000  |

|----|--------|-----|--------------|----------------|-------|------------|-------|--------------|-----------|------|

| «Д | [инам  | ика | роста» (г. Г | <b>Термь</b> ) | ••••• |            | ••••• | •••••        | • • • • • | 219  |

| 3. | Акт (  | о в | недрении р   | езультатов     | диссе | ртационно  | го ис | следования в | ΦИ        | ц иу |

| PΑ | ΑН (г. | Mo  | осква)       |                | ••••• |            |       |              | ••••      | 220  |

#### **ВВЕДЕНИЕ**

Актуальность темы исследования. Программируемые логические интегральные схемы (ПЛИС или программируемые пользователем вентильные матрицы – ППВМ, Field-Programmable Gate Array – FPGA или сложные программируемые логические устройства CPLD – Complex Programmable Logic Device) широко используются во многих областях применения. За последние четыре года объем производства ПЛИС увеличился более чем на 50%. На период 2025-2029 гг. ожидается среднегодовой темп роста глобального рынка высокопроизводительных ПЛИС более 11%. Актуальность практического применения подтверждается также ростом использования ПЛИС в областях критического применения медицина, авионика, космическая аппаратура управления АЭС, ГЭС и ТЭС, вооружение и военная техника, и др. В настоящее время ПЛИС (FPGA) передовых производителей содержат уже десятки миллионов логических элементов (коммутаторов межсоединений в глобальных и локальных матрицах связей на несколько порядков больше) и десятки миллиардов транзисторов. В ПЛИС используются логические элементы, называемые «таблицами просмотра» или «таблицами истинности» LUT (Look Up Table), в которых используется бинарное (позиционное) кодирование наборов переменных, они же могут реализовывать коммутаторы межсоединений, тогда бинарным кодом кодируется требуемая связь. Коммутаторы межсоединений могут строится и как унитарные мультиплексоры из передающих транзисторов, использующие унитарное кодирование связей (активен только один бит), что экспоненциально увеличивает объем памяти настройки. Но в отличие от LUT на *n* переменных, в которых путь сигнала содержит не менее чем n транзисторов, в таких коммутаторах этот путь включает, как правило, всего один транзистор. ПЛИС, как универсальное устройство, проигрывает микросхемам (ASIC – application-specific integrated circuit) в быстродействии, выигрывая в стоимости. Количество переменных, реализуемых логических функций в одном адаптивном элементе, может составлять до восьми переменных.

При увеличении числа переменных в одном элементе резко снижается быстродействие. Таким образом, актуальным является проведение исследований по снижению временной задержки элементов ПЛИС при ограничении объема памяти настройки или числа связей переменных.

Степень разработанности темы исследования. Вопросы синтеза и анализа логических элементов ПЛИС [92] ранее были предложены и исследованы в работах отечественных авторов: А.В. Строгонова [2–3, 14–16], С.А. Цыбина, А.Н. Денисова [18], Г.П. Аксеновой, Д.Е. Иванова [96], Ю.А. Скобцова [21], А.А. Баркалова [47]. Зарубежные ученые в области ПЛИС: В.И. Хаханов [22], А.В. Дрозд [23, 96], В.С. Харченко [24], Е. Зорян [25], Н. Мехта, Раджитх К. Шрикант, Мандар Д. Чафекар, Цзяо Вей, Ли Чжун [9], Мартин Шмитц, Лаурент Фандо, Джон Оустерхаут, Питер Юнг и др [30-32, 91. 93]. Новые логические элементы ПЛИС предложены и исследованы в работах научной группы кафедры АТ ПНИПУ: С.Ф. Тюрина [33, 34, 42, 79, 87, 88, 89, 90], А.В. Грекова [35, 87], О.А. Громова [36, 87], А.Ю. Городилова [37, 89], А.Н. Каменских [38], Р.В. Вихорева [38–42, 44], А.Ю. Скорняковой [43, 44], С.И. Советова [45–46, 79] и др. Известные варианты комбинирования унитарного кодирования путем разбиения на группы (А.В. Строгонов) не используют возможность комбинирования с позиционным кодом. Кроме того в известных работах не используются варианты унитарного кода для вычисления логических функций с использованием разложения Шеннона. Противоречие в науке заключается в следующем: созданы предпосылки комбинирования двух подходов в реализации логических функций и коммутации связей, но они еще не объединены единым методом. Поэтому целесообразно исследовать различные варианты комбинирования позиционного и унитарного кода для реализации элементов, как для вычисления логических функций, так и для коммутации связей.

**Объектом исследования** являются ПЛИС с элементами LUT, использующими позиционное (бинарное) кодирование и с элементами коммутирования межсоединений, использующими унитарное кодирование.

**Предметом исследования** является научно-методический аппарат синтеза элементов ПЛИС, использующих комбинированное кодирование и обладающих повышенным быстродействием.

**Цель** диссертационного исследования заключается в решении научной задачи разработки модели и метода синтеза элементов ПЛИС, использующих комбинированное кодирование.

Для достижения поставленной цели в диссертационной работе поставлены и решены следующие задачи исследования:

- 1. Аналитический обзор, анализ, исследование и сравнение существующих моделей и методов синтеза базовых элементов ПЛИС для вычисления логических функций и коммутации сигналов в матрицах межсоединений.

- 2. Разработка математической модели элемента с комбинированным и универсальным кодированием (Паспорт специальности: п.2).

- 3. Разработка метода синтеза элементов с комбинированным и универсальным кодированием (Паспорт специальности: п.2).

- 4. Разработка алгоритма синтеза элемента с заданным вариантом кодирования (Паспорт специальности: п.2).

- 5. Разработка схем электрических функциональных и принципиальных предлагаемых элементов.

- 6. Схемотехническое моделирование разработанных элементов с комбинированным кодированием.

- 7. Топологическое моделирование разработанных элементов с комбинированным кодированием.

- 8. Получение оценок сложности и эффективности различных вариантов комбинированного кодирования, позволяющих осуществлять выбор оптимального варианта (вариантов).

- 9. Апробация разработанной модели, метода, алгоритма и оценок сложности, внедрение в ФИЦ ИУ РАН.

#### Положения, выносимые на защиту и обладающие научной новизной:

- 1. Разработана новая математическая модель элемента, отличающаяся тем, что описывает комбинированные варианты, использующие как позиционное, так и унитарное кодирование в одном устройстве, а также универсальный элемент с настраиваемым типом кодирования (п. 2 «Разработка принципиально новых методов анализа и синтеза вычислительных систем и их элементов с целью улучшения технических характеристик, включая новые процессорные элементы, сложно-функциональные блоки, системы и сети на кристалле, квантовые компьютеры» паспорта специальности 2.3.2).

- 2. Создан элементов c комбинированным метод синтеза универсальным кодированием, отличающийся тем, что позволяет создавать новые устройства с лучшими характеристиками по быстродействию при допустимом увеличении сложности (п. 2 «Разработка принципиально новых методов анализа и синтеза вычислительных систем и их элементов с целью характеристик, улучшения технических включая новые процессорные элементы, сложно-функциональные блоки, системы и сети на кристалле, квантовые компьютеры» паспорта специальности 2.3.2).

- 3. Получены математические выражения **оценок сложности** новых элементов с комбинированным кодированием, позволяющие выбирать требуемый вариант комбинирования (п. 6 «Разработка научных подходов и методов, архитектурных и структурных решений, обеспечивающих эффективную техническую реализацию аппаратно-программных систем и комплексов за счет оптимизации применяемой электронной компонентной

базы, элементов вычислительных систем и встраиваемого программного обеспечения» паспорта специальности 2.3.2).

4. Разработан алгоритм комбинированным синтеза элемента c кодированием, отличающийся тем, что обеспечивает по заданным параметрам требуемые соединения, используя предложенный элемент с конфигурируемым кодированием (п. 6 «Разработка научных подходов и методов, архитектурных и структурных решений, обеспечивающих эффективную техническую реализацию аппаратно-программных систем и комплексов за счет оптимизации применяемой электронной компонентной базы, элементов вычислительных систем и встраиваемого программного обеспечения» паспорта специальности 2.3.2).

**Теоретическая значимость** результатов диссертационной работы состоит в развитии научно-методического аппарата синтеза элементов ПЛИС путем разработки модели, метода, алгоритма и оценок сложности элемента с комбинированным кодированием переменных.

Практическая значимость результатов диссертационной работы состоит в разработке нового, запатентованного элемента ПЛИС с комбинированным кодированием переменных, обладающего лучшими характеристиками, чем существующие [79, 100]. Разработаны схемы электрические функциональные и принципиальные, а также топологии новых элементов и программа их синтеза. Временная задержка снижается более, чем на 15%, а также в ряде случаев снижаются и аппаратурные затраты более, чем на 20% в зависимости от разрядности унитарной и позиционной части.

Результаты работы внедрены в учебный процесс кафедры «Автоматика и телемеханика» ФГАОУ ВО «Пермский национальный исследовательский политехнический университета» в рамках практических занятий профильных дисциплин «Дискретная математика и математическая логика», «Цифровая схемотехника» бакалавриата направлений подготовки 11.03.02 ДЛЯ 15.03.06 «Инфокоммуникационные технологии системы связи». И

«Мехатроника и робототехника», 27.03.04 «Управление в технических системах». Также результаты внедрены в ООО «Динамика роста» (г. Пермь), которое приобрело лицензию у Пермского Национального Исследовательского (ПНИПУ) Политехнического Университета на право использования изобретения «Программируемое логическое устройство» (патент РФ № 2 811 404, приоритет от 02.08.2023 г., дата государственной регистрации 11.01. 2024 г). Кроме того, результаты исследования внедрены в научно-исследовательской работе отдела 52 Федерального исследовательского центра «Информатика и управление» Российской академии наук (ФИЦ ИУ РАН) «Архитектура и схемотехника инновационных вычислительных систем» ПО теме «Информационные, управляющие государственного задания И телекоммуникационные системы 2024-2028».

**Методология и методы исследования.** В диссертационной работе используются методы, модели, алгоритма и программное обеспечение, позволяющие произвести схемотехническое и топологическое моделирования для проведения анализа и синтеза схем, а также расчеты показателей сложности. Применяемые и используемые методы, средства и инструменты имеют научное обоснование. Основу этих обоснований составляют положения дискретной математики, математической логики, комбинаторики, принципы МОП-схемотехники, теории булевых функций и автоматов.

Достоверность и обоснованность результатов, полученных в ходе исследования, не противоречат теоретическим положениям и выводам, ранее опубликованным результатам отечественных И зарубежных ученых. Подтверждение результатов было получено в двух различных системах моделирования (Multisim, Microwind), апробированием и внедрением методов, моделей и алгоритма подключения, предложенных в диссертации. Расчеты проводились с помощью системы компьютерной алгебры Mathcad. Основные теоретические и практические результаты работы докладывались на научнотехнических конференциях: «Международная конференция молодых

исследователей в области электротехники и электроники 2023 ElConRus», «ElCon» 2025, «Инновационные технологии: теория, инструменты, практика» (InnoTech-2022, 2023, 2024), «Научно-техническая конференция 2023 IEEE 24th International Conference of Young Professionals in Electron Devices and Materials (EDM) (республика Алтай, НГТУ)», Всероссийская научно-техническая конференция «Автоматизированные системы управления и информационные технологии» (АСУИТ-2024, 2023, г. Пермь), Школа молодых учёных в рамках Российского форума «Микроэлектроника 2024».

**Публикации.** Основные результаты диссертационной работы опубликованы в 11 печатных работах, из них 4 публикации в ведущих рецензируемых научных изданиях, 2 публикации в изданиях, индексированных в международной базе цитирования Scopus, 2 патента на изобретения.

Объем и структура работы. Диссертация состоит из введения, пяти глав, заключения, списка литературы из 103 наименований и трех приложений. Полный объем диссертации составляет 220 страниц, из которых 194 страниц занимает основной текст диссертации, включающий 110 рисунков и 10 таблиц.

# ГЛАВА 1. АКТУАЛЬНОСТЬ И АНАЛИЗ ОБЪЕКТА И ПРЕДМЕТА ИССЛЕДОВАНИЯ. ПОСТАНОВКА ЗАДАЧИ ИССЛЕДОВАНИЯ

## 1.1 Обзор и анализ объекта исследования – элементов ПЛИС. Противоречие в практике

#### 1.1.1 Анализ современных ПЛИС

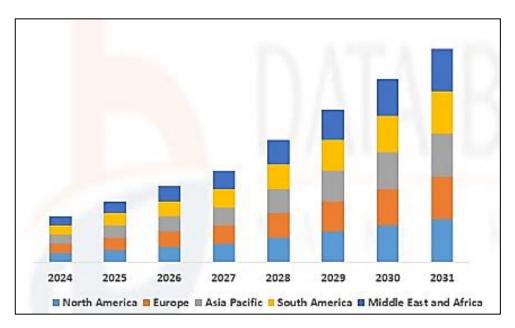

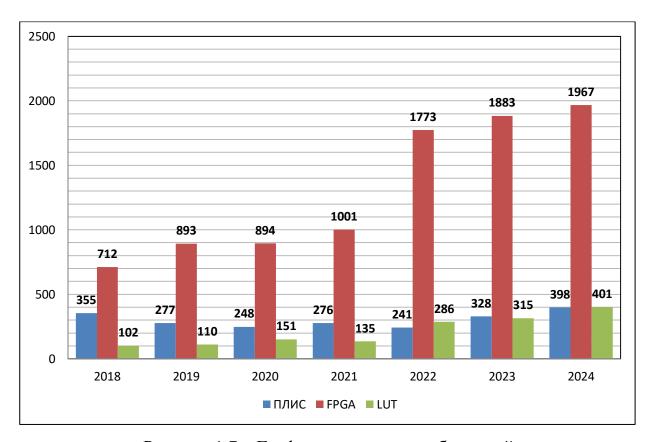

История создания и развития ПЛИС включает около 40 лет, хотя сама программируемая логика (универсальные логические модули), начиная с программируемой памяти, программируемых логических матриц (ПЛМ, PLA, ПМЛ, PAL) — насчитывает около 60 лет [4–8]. Доступ к последней информации по ПЛИС в настоящее время сопряжен с определенными известными трудностями. Рынок современных ПЛИС, представлен, например, в источнике [17]. В плане импортозамещения электронной компонентной базы в современных реалиях крайне актуальны исследования по совершенствованию отечественных ПЛИС [14]. Примером могут быть впечатляющие темпы совершенствования китайских производителей ПЛИС [15, 16]. Прогноз глобального рынка ПЛИС до 2031 г. по данным [17] показан на рисунке 1.1.

Рисунок 1.1 – Прогноз глобального рынка ПЛИС (Global Low-End Field-Programmable Gate Array (FPGA) Market – Industry Trends and Forecast to 2031)

Показатель CAGR (Compound Annual Growth Rate) – совокупный среднегодовой темп роста на этот период оценивается более 11%, размер рынка на прогнозируемый период – более 14 млрд. долларов. В настоящее время на ПЛИС электронной техники делят рынке на три сегмента производительности: высококачественные ПЛИС (высокопроизводительные, High End FPGA), ПЛИС среднего класса (Mid-End FPGA,ПЛИС средней производительности), ПЛИС для бытовых устройств, начального уровня (низкопроизводительные ПЛИС, Low-End FPGA). Высокопроизводительные ПЛИС используются, например, в центрах обработки данных.

По особенностям хранения конфигурационных настроек выделяются три основных варианта.

Первый использует оперативную память конфигураций (ОЗУ, SRAM), при этом конфигурация (настройка функций и связей) теряется при выключении источника питания [86], а при его включении необходимо определенное время для загрузки конфигурации последовательным кодом, например, из внешнего компьютера или внешней энергонезависимой (non-volatile) памяти. Большинство ПЛИС используют ОЗУ (SRAM).

Второй вариант предполагает использование постоянной перепрограммируемой памяти (ППЗУ, EEPROM), например вида Flash, что требует совмещения нескольких технологий и, соответственно, дороже. Кроме того, число перепрограммирований ограничено (например, около 10 000 раз), в отличие от технологии (ОЗУ, SRAM), зато ПЛИС сразу готова к работе после включения электропитания.

Вариант Antifuse («Антипредохранитель», fuse — «предохранитель») характеризуется однократным и относительно медленным программированием, подобно так называемым полузаказным базовым матричным кристаллам (БМК). Если при программировании fuse «плавкая вставка» пережигается либо не пережигается, то Antifuse либо «наплавляется», либо не наплавляется [48].

Этот вариант тоже требует совмещение разных технологий, но зато такие ПЛИС меньше подвержены радиационным воздействиям и обладают большим быстродействием.

Другие особенности современных ПЛИС отражены, например, в публикациях [49–53]. Количество логических элементов, которые объединяются в целые «фабрики логики», достигает десятков миллионов в High End FPGA, а общее количество транзисторов — десятки миллиардов. Количество переменных в одном элементе в ранних ПЛИС было всего 3-4. В настоящее время используются так называемые адаптивные логические модули, в которых можно создать элемент на 5,6 и 7 переменных. В ряде случаев конфигурируется элемент на 8 входов, но реализуются лишь некоторые функции.

## 1.1.2 Анализ логического элемента FPGA и элемента – коммутатора межсоелинений

Реализация логических функций в ПЛИС типа FPGA основана на использовании мультиплексора в режиме коммутации констант настройки [1-3], представляющих собой значения из таблицы истинности соответствующей функции. Такое устройство обычно называют LUT (Look Up Table). LUT представляет собой бинарное дерево передающих транзисторов [2, 3], но может содержать и 2n ветвей по n транзисторов [29]. Классические логические элементы LUT реализуют (вычисляют) логические функции одной, двух, трёх и четырёх переменных. Это связано c ограничениями на количество последовательно соединенных транзисторов (не более четырех) [54]. Имеются более сложные элементы, называемые адаптивными логическими модулями (АЛМ), которые реализуют любые функции до семи аргументов и некоторые функции восьми аргументов путем конфигурируемого соединения классических LUT [49 –51, 85]. Несмотря на впечатляющие достижения в области ПЛИС, они остаются универсальными устройствами со всеми

соответствующими преимуществами и недостатками, которые требуют особого внимания в области так называемых критических приложений [10–13].

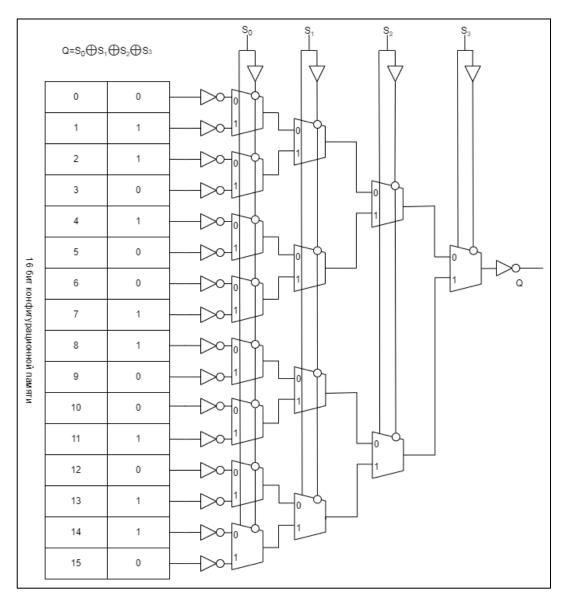

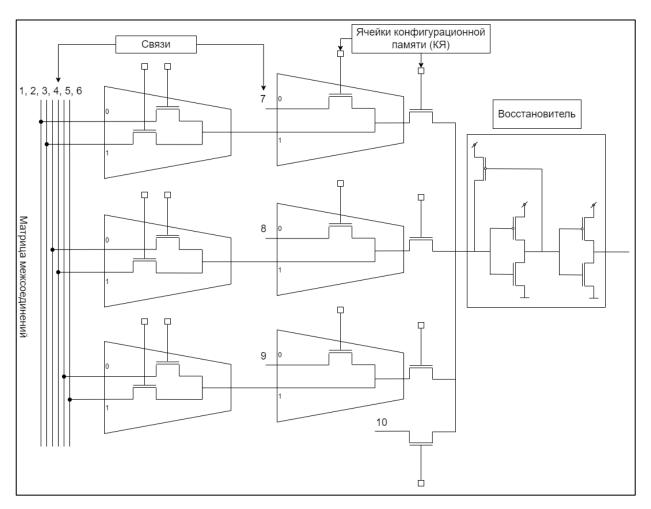

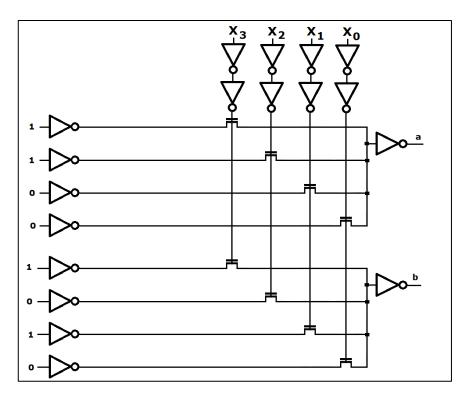

Логический элемент LUT [2, 49] на четыре переменные показан на рисунке 1.2.

Рисунок 1.2 – Логический элемент LUT на четыре переменные S.0, S.1, S.2, S.3; биты конфигурационной памяти – d.0-d.15

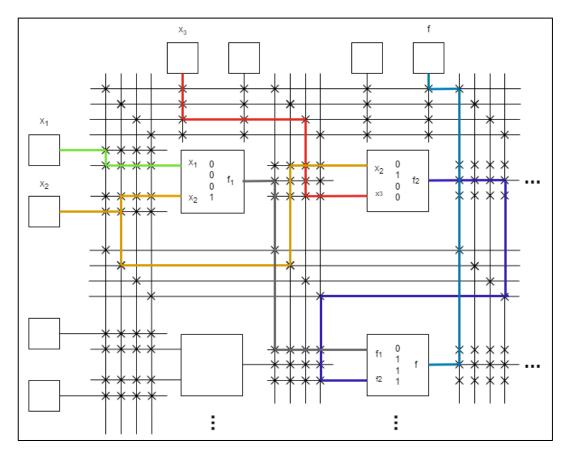

Логические элементы соединяются между собой и с контактами ПЛИС с помощью коммутаторов в матрицах межсоединений. На рисунке 1.3 показан пример реализации логической функции трёх внешних переменных  $f=x_1x_2 \vee x_2x_3$ , использующей три LUT на две переменные.

Рисунок 1.3 – Реализация логической функции трёх внешних переменных

Коммутаторы сигналов показаны синими крестиками на требуемом пересечении линий связи в матрицах межсоединений (черные — неактивные пересечения). Первый LUT реализует конъюнкцию двух переменных  $x_1x_2$  (таблица истинности 0001). В развернутой форме это выглядит так — таблица 1.1:

Таблица 1.1 – Пример таблицы истинности – конъюнкция

| Старшая переменная $x_1$ | Младшая переменная $x_2$ | $\Phi$ ункция $f_1$ |  |

|--------------------------|--------------------------|---------------------|--|

| 0                        | 0                        | 0                   |  |

| 0                        | 1                        | 0                   |  |

| 1                        | 0                        | 0                   |  |

| 1                        | 1                        | 1                   |  |

Второй LUT реализует функцию запрета второй переменной  $x_2x_3$  (таблица истинности 0100). Третий LUT реализует функцию дизьюнкции результатов вычислений первых двух LUT (таблица истинности 0111). Выход третьего LUT подключен к контакту f ПЛИС.

Анализ показывает, что производители для минимизации площади кристалла выбирают оптимальную разрядность LUT от 3 до 4 переменных. Для достижения максимального быстродействия целесообразен LUT от 4 до 6 переменных. В ПЛИС с АЛМ может быть конфигурирован LUT до 7 переменных. LUT на 8 переменных реализует не все возможные логические функции.

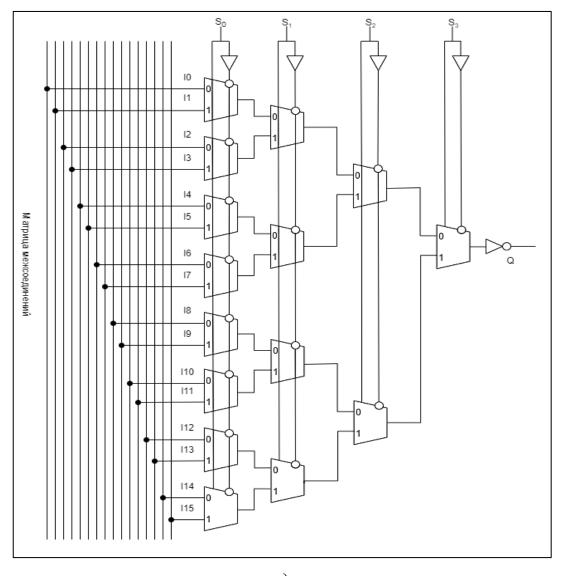

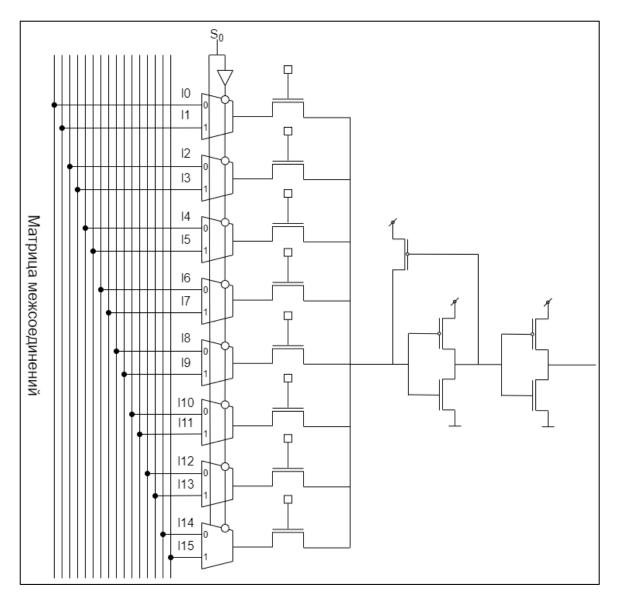

Строго говоря, LUT — это такой мультиплексор с настройкой (рисунок 1.2), при отсутствии настройки, это не будет являться LUT. Для простоты мы будем использовать обозначение LUT и для коммутаторов, то есть в случае подключения вместо настройки — связей, а сама настройка теперь — по входам переменных (рисунок 1.4):

Рисунок 1.4 – а) Коммутатор сигналов с локальных межсоединений на вход конфигурируемого логического блока с использованием мультиплексоров (S0—S3 — конфигурационные биты памяти); б) мультиплексор на *n*-МОПТ ключах; в) мультиплексор на КМОП-ключах

B)

В этом случае путь сигнала проходит через n транзисторов. Настройка бинарным позиционным кодом выбирает одну из  $2^n$  связей.

В случае как на рисунке 1.4 — четыре транзистора, что является критичным в силу ограничений Мида-Конвей [54, 94] на число последовательно соединенных транзисторов (это обусловлено падением напряжения на транзисторах на величину порогового напряжения). Обычно

допускают три подряд соединенных транзистора, после которых устанавливается восстановитель уровня сигнала (буфер).

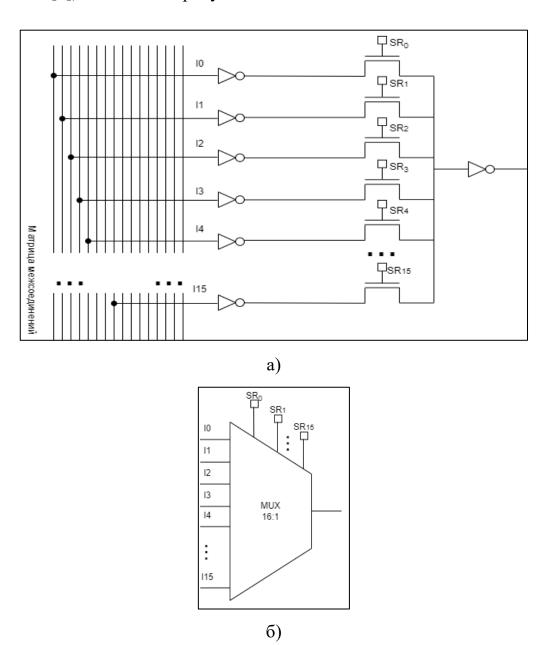

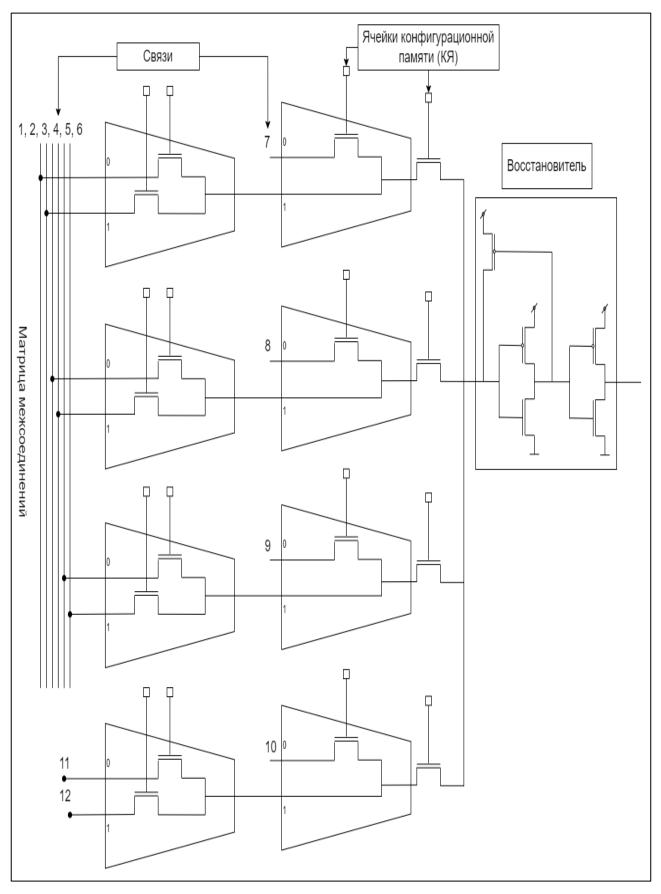

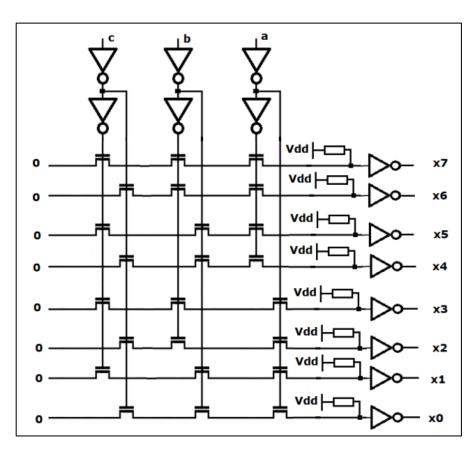

Использование унитарного кода для коммутации сигналов (например, в сети многоканальный соединений MultiTrack с использованием технологии Direct Drive [2]) показано на рисунке 1.5.

Рисунок 1.5 — Коммутатор сигналов 16 в 1 (мультиплексор 16-1) с матрицы межсоединений на вход конфигурируемого логического блока (КЛБ) с одним транзистором в цепочке: а) с использованием *n*-МОПТ ключей (передающих n-МОП транзисторов); б) условное обозначение; SR — ячейки конфигурационной памяти, объём памяти — 16 бит

В этом случае путь сигнала проходит через один транзистор. Всего транзисторов с учетом инверторов 50.

Известный комбинированный вариант кодирования («унитарный+ унитарный») приведен в работе [2] и показан на рисунке 1.6.

Рисунок 1.6 – Существующий комбинированный вариант коммутатора

Унитарный код используется также в САПР Quartus для ПЛИС фирм Intel (Altera). Кодирование конечного автомата, построенного по графу переходов (State Machine File), по умолчанию (Auto) принимается унитарным (One-Hot) [55].

### 1.2 Анализ предмета исследования — научно-методического аппарата синтеза — элементов ПЛИС. Противоречие в науке

# 1.2.1 Анализ публикаций по научно-методическому аппарату синтеза элементов ПЛИС

На ресурсе IEEE ieeexplore (https://ieeexplore.ieee.org) за 1989-2025 гг. поиск по запросу "FPGA" отображает более 47000 материалов научных конференций, более 6500 статей в журналах, 106 книг, 10 стандартов.

За период 2020-2025 — более 10500 материалов научных конференций, более 3000 статей в журналах, 53 книги, 2 стандарта (рисунок 1.7).

Поиск по запросу "LUT FPGA" за период 2020-2025 — около 600 материалов научных конференций, более 180 статей в журналах, 3 книги.

Рисунок 1.7 – График роста числа публикаций

На ресурсе Researchgate (https://www.researchgate.net) по запросу «FPGA» отображается более 1000 публикаций. По запросу «LUT FPGA» за 2024 г.

отображается более 480 публикаций. Запрос «LUT FPGA encoding» за 2025 год выдает 68 публикаций на 11.01.25.

На сайте https://www.elibrary.ru по запросу «FPGA» выдается более 18000 публикаций, из них более 10000 за 2020-2025 гг. По запросу «LUT FPGA» выдаются более 400 публикаций. Запрос «LUT FPGA encoding» формирует 20 публикаций.

Известный международный издательский ресурс https://link.springer.com по запросу «FPGA» выдает более 12500 статей и примерно столько же материалов конференций, более 300 статей за последние три месяца, три книги, более 100 материалов конференций.

Ресурс https://scholar.google.com по запросу «FPGA» выдает более миллиона результатов, за период с 2021 года — более 50000, с 2025 — более 1200. По запросу «LUT FPGA» с 2025 года — 178 результатов.

Одна из ключевых проблем публикаций последних лет — сокращение разрыва между гибкой и заказной логикой, поскольку по мере усложнения логических элементов остро встает проблема повышения быстродействия, частично решаемая, например, путем специальных способов проектирования (HyperFlex, Hyper-Registers, Hyper-Retiming и др.), в том числе, снижающих задержки в цепях обратных связей через матрицы коммутаций [2].

В частности, используется разложение Шеннона (Shannon decomposition or Boolean factorization) [49, 56] для создания, например, двух вариантов логической функции для двух значений состояния триггера, которое коммутирует выходы логических элементов, реализующих эти два варианта функций.

При этом используется «рядом стоящий» LUT на одну переменную, а переменная состояния не проходит матрицы коммутации, за счет чего достигается повышение быстродействия, хотя и увеличиваются затраты в количестве логических элементов. По сути, используется заранее вычисленные значения логических функций для двух разных значений состояний.

Дальнейшее развитие этого подхода приводит к необходимости использования унитарного кода (в англоязычной литературе unitary code, one-hot, one-cold) для более чем одного триггера и более, чем два варианта логических функций от входных переменных.

Однако, это приводит к увеличению аппаратных затрат, что вызывает необходимость нахождения «золотой» середины между унитарным и позиционным бинарным кодом.

В то же время, несмотря на то, что имеется достаточно много публикаций в области ПЛИС и созданы все предпосылки для объединения этих двух подходов, советующих публикаций обнаружено не было.

# 1.2.2 Исследование направления создания элементов с комбинированным кодированием переменных или настройки

Метод, использующий комбинированный код, приведенный в публикации [2] (рисунок 1.6) не использует соединения унитарного и позиционного кодов. Кодирование такого дерева — не стандартное, активны два бита: один — выбор ветви дерева, второй выбор листа дерева (рисунок 1.5). Показана коммутация сигнала 15, при коде [(0)(0000)] [(1)(0100)] [(0)(0000)] [(0)(0000)]. Первый элемент кода в квадратных скобках — код ветви (1), второй — код листа (0100). То есть имеется двухуровневое кодирование.

Однако, на рисунке 1.8 всего 10 связей, а на рисунке 1.5 – 16. Если предположить, что ветвь к связи №10 аналогична остальным, то получим 12 связей.

Далее в публикации такой вариант сравнивается с унитарным (рисунок 1.4). Но тогда и связей должно быть 16. Это можно сделать, например, так, как показано на рисунке 1.9.

Рисунок 1.8 – Существующий комбинированный вариант коммутатора, доработанный до 12 связей

Рисунок 1.9 – Комбинированный вариант коммутатора на 16 связей (Мультиплексор 16-1 с двумя транзисторам в цепочке); объём памяти – 20 бит (и 20 передающих транзисторов соответственно) против 16-ти

Здесь сигнал проходит через два транзистора, но все равно используется восстановитель уровня сигнала. Хотя, по сути, восстановитель в виде инвертора есть и на рисунке 1.5. По сравнению с рисунком 1.5 (50 транзисторов) число транзисторов уменьшено до 25 (20+5 в восстановителе), но увеличен объем памяти = 20 против 16 на рисунке 1.4.

Однако с учетом конфигурационной памяти получаем для рисунка.1.5 (унитарное кодирование) 50+16·6=146 транзисторов. Для рисунка 2.2: 25+20·6 =145 транзисторов. Таким образом, получаем по всем показателям хуже унитарного кодирования (рисунок.1.5). Сведем результаты анализа в таблицу 1.2:

Таблица 1.2 – Сравнение трех вариантов кодирования коммутатора межсоединений

| No   |            | Количество   | Объем  | Общее        | Задержка в   | Примоно        |

|------|------------|--------------|--------|--------------|--------------|----------------|

| Вари | Название   | передающих   | Памяти | количество   | количестве   | Примеча<br>ние |

| анта |            | транзисторов | (бит)  | транзисторов | транзисторов | нис            |

| 1    | LUT-       | 30           | 4      | 62           | 4            | Рисунок        |

| 1    | коммутатор | 30           | 7      | 02           |              | 1.4            |

| 2    | Унитарный  | 16           | 16     | 146          | 1            | Рисунок        |

| 2    | коммутатор | 10           | 10     | 140          | 1            | 1.5            |

| 3    | Комбиниров | 20           | 20     | 145          | 2            | Рисунок        |

|      | анный      | 20           | 20     | 143          | 2            | 1.8            |

Видим, что варианты 1 и 2 несравнимы: LUT – коммутатор выигрывает по числу транзисторов, но проигрывает унитарному коммутатору по задержке. вариант 3 по всем параметрам (один транзистор выигрыша – не в счет) хуже второго.

Если же учесть инверторы по входам связей, как на рисунке 1.5, то комбинированный вариант 3 (рисунок 1.9) будет еще сложнее. Возможно, площадь кристалла комбинированного варианта меньше унитарного.

В унитарном варианте (рисунок 1.5) сразу выбирается лист дерева (000001000000000). То есть имеется одноуровневое кодирование.

Кроме того, унитарное кодирование используется только в коммутаторах межсоединений и не рассматривается для реализации логических функций.

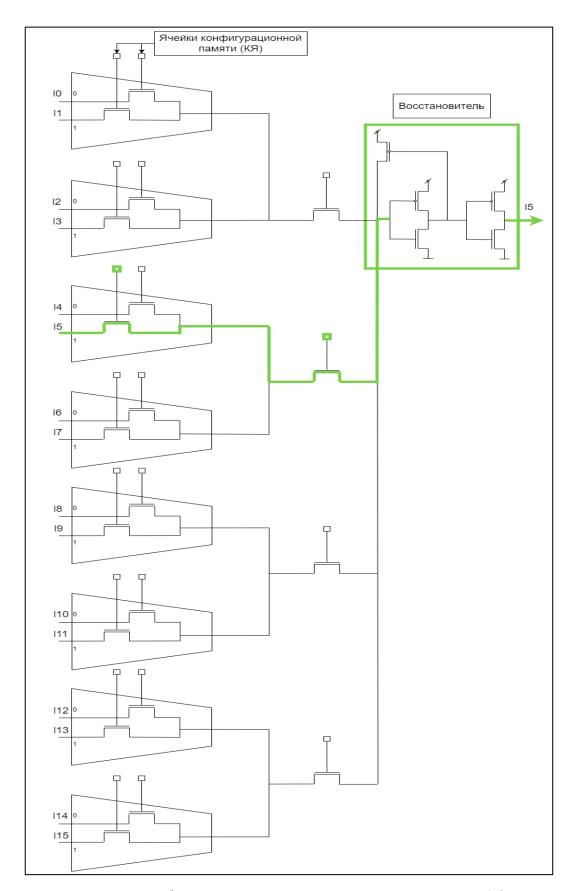

Другое дело, если комбинируются мультиплексоры на одну переменную и передающие транзисторы, на которые подается унитарный код (рисунок 1.10).

Рисунок 1.10 — Другой возможный комбинированный вариант коммутатора на 16 связей (Мультиплексор 2-1 и унитарный байт); объём памяти — 9 бит, 31 транзистор с учетом инвертора и восстановителей

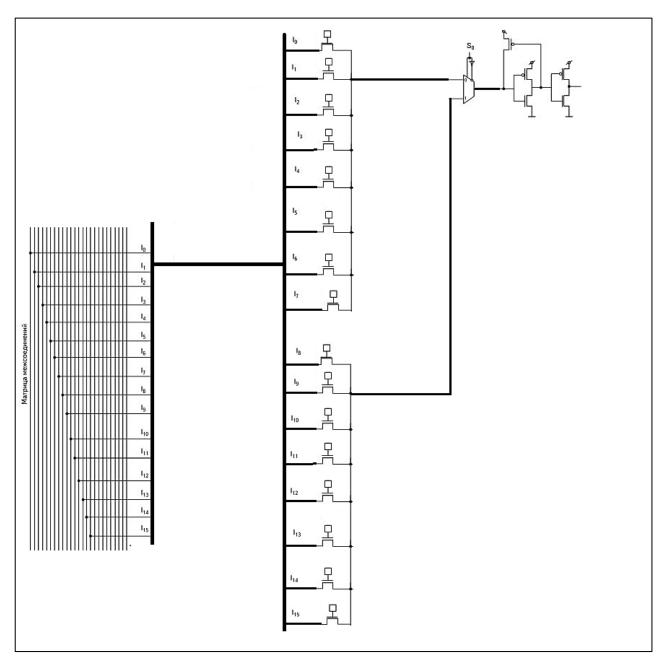

Но такой вариант соединения позиционного кода (на рисунке -1.10 один бит S0) и унитарного не рассматривается, так же, как вариант, изображенный на рисунке 1.11.

Рисунок 1.11 – Второй возможный комбинированный вариант коммутатора на 16 связей (Мультиплексор 2-1 и два унитарных коммутатора); объём памяти – 9 бит, но 25 транзисторов с учетом инвертора и восстановителей

Таким образом, по результатам анализа источников это направление исследования является новым [57].

В настоящее время имеются сведения об исследованиях применения в области применения в FPGA и других кодов, например, кода Хэмминга [58], БЧХ кода [59–61], Рида-Соломона [62, 63] и др. Однако речь идет о повышении надежности памяти или передачи информации. Код Грея и его модификации

(«соседние коды», отличающиеся только в одном разряде) [64, 65] применяются, например, для устранения состязаний (гонок) входных сигналов, для снижения ошибок преобразователей «вал-код» и пр. Код Грея использует простой алгоритм обеспечения «соседства» наборов: 000, 001, 011, 010, 110, 111, 101, 100,000. В то же время «не соседний» Natural Binary Codes (Sequential Code) использует обычный порядок наборов: 000, 001, 010, 011, 100, 101, 110, 111, 000. В этом случае, в отличие от кода Грея могут изменяться сразу все разряды, когда, например, 111 меняется на 000.

Код Джонсона [66] используется для упрощения схем счетчиков, он тоже «соседний»: 000, 001, 011, 111, 110, 100, 000. Код Айкена [67], как вариант двоично-десятичного (ВСD, код 2421) используется для сложения и вычитания. Относительно LUT код Грея ничем принципиально не отличается от обычного Natural Binary Code, просто наборы меняются в другом порядке, но все равно это все возможные коды булеана (множества всех подмножеств) универсального множества из *п* элементов, что необходимо для выбора только одной цепочки в дереве передающих транзисторов — рисунок 1.3. Это нельзя сказать о кодах Джонсона и Айкена.

Но такой принцип справедлив для унитарного кода (unitary code, one-hot, если одна единица 0001, либо one-cold, если один ноль 0111), который представляет собой, например, код на выходе дешифратора, то есть фиксирует истинность одной из 2*n* конституент некоторой логической функции [55], используется также для кодирования состояний автомата или графа переходов автомата, когда активно (равно единице или нулю) только одно состояние, одна из вершин графа, что снижает сложность логического преобразователя. Однако при этом усложняется блок памяти. Обычный позиционный двоичный код при кодировании памяти автомата в САПР QUARTUS называется «Minimal Bits». Используются также экзотические системы счисления на основе двоичного код Фибоначчи [68], что также повышает помехоустойчивость. Коды для

шифрования информации от злоумышленников в данной работе не рассматриваются.

Таким образом, в исследуемой области, как правило, применяются двоичный позиционный и унитарный коды.

Модификаций этих кодов для элементов логики и коммутаций ПЛИС в доступных источниках найдено не было. Имеются публикации о снижении временной задержки в коммутаторах (мультиплексорах маршрутизации – routing multiplexers) на основе новых физических принципах, например, на резистивной оперативной памяти Resistive Random Access Memory (RRAM) [69].

Достигнут новый уровень быстродействия или энергоэффективности элементов ПЛИС со снижением токов утечки (Leakage current), которые резко возрастают при снижении технологических норм, основе новых типов и технологий транзисторов, использующих химические вещества, не раскрываемые производителями [70-73].

Это так называемые «плавниковые» FinFET (fin field-effect transistor), то есть не планарные, а имеющие "3D" затвор, «tri-gate» транзисторы, имеющие три "3D" затвора (triple-gate transistor), с круговым затвором «Gate-all-around FETs» (GAAFETs), которые могут работать при техпроцессах менее 7 nm, «ленточные» RibbonFET транзисторы, ferroelectric FET (CFeFET) [73] и др.

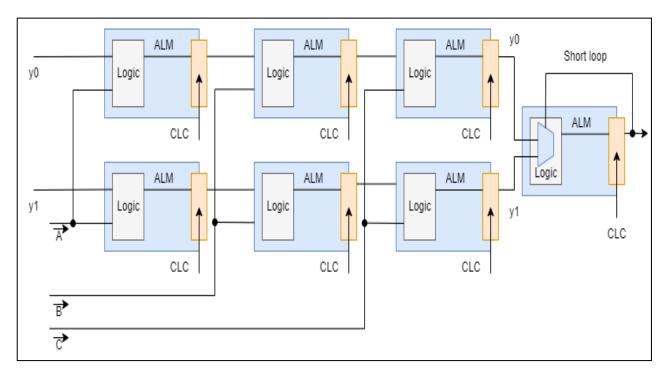

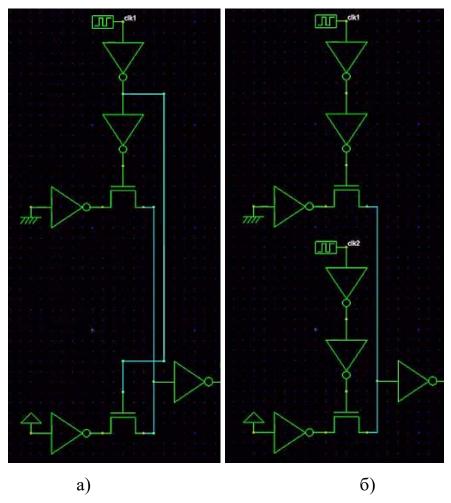

Но это направление (своего рода «физико-химическое») выходит за рамки данного исследования и научной специальности, как и использование, например, тернарной логики [74–76], снижение энергопотребления коммутаторов за счет отключения не используемых участков ПЛИС [27, 28] и пр. «Короткий» унитарный код, помимо указанного выше использования в коммутаторах, используется в «гипер-оптимизации» [49, 77], обеспечивающей короткую обратную связь, где задержка определяется только задержкой последнего АЛМ, а все возможные результаты уже просчитаны заранее, рисунке 1.12.

Рисунок 1.12 — Унитарный код ( $y1\ y0$ ) по значению переменной y

Пусть имеется некоторая условная функция переходов, выражение (1.1):

$$y(t+1) = d(t) = [a_1 a_2 a_3 y(t) \vee \overline{a_1} \overline{a_2} \overline{a_3} y(t)] \vee b_1 b_2 b_3 \vee c_1 c_2 c_3.$$

(1.1)

Разложение Шеннона позволяет получить две функции, выражение (1.2):

$$y0: a_1a_2a_3 \vee b_1b_2b_3 \vee c_1c_2c_3; y1: a_1a_2a_3 \vee b_1b_2b_3 \vee c_1c_2c_3.$$

(1.2)

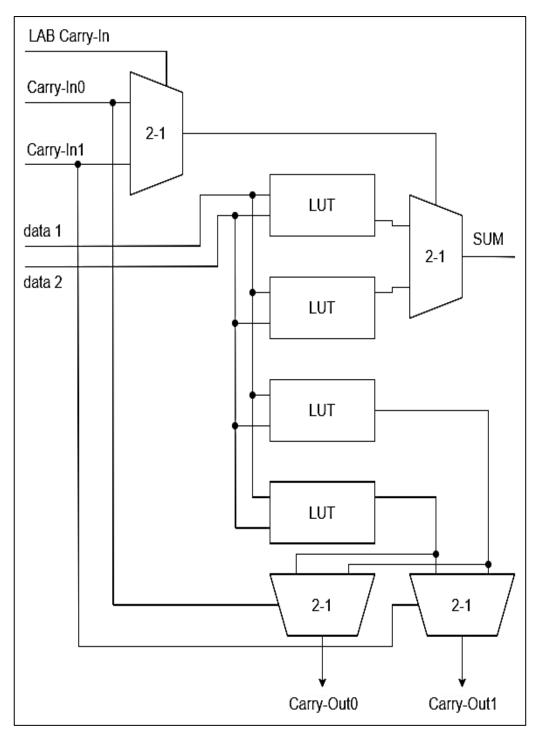

Дальнейшее развитие этого подхода может привести к разложению Шеннона по большему числу переменных, хотя аппаратные затраты возрастают, но они считаются не существенными по сравнению с выигрышем в задержке. Следует отметить, что такой подход применялся еще в прежних поколениях ПЛИС FPGA [51] для реализации арифметического режима, рисунок – 1.13.

Поэтому имеет смысл в качестве дальнейшего развития этого подхода исследовать различные варианты возможного предложенного выше комбинированного кодирования для вычисления логический функций (с целью снижения временной задержки) и для коммутаторов межсоединений (с целью

снижения объема конфигурационной памяти), а также определить наиболее предпочтительные варианты.

Рисунок 1.13 – Пример унитарного кода по переменной Carry-In

Для этого необходима разработка соответствующего научнометодического аппарата комбинирования унитарного и позиционного кода в элементах ПЛИС.

#### 1.3 Математическая постановка задачи и частных задач исследования

С учетом направлений, задач и целей исследования, установленных выше, математическая постановка задачи выглядит следующим образом.

#### Дано:

1) Элемент с позиционным кодированием: либо для вычисления логической функции z от n переменных x с таблицей истинности  $d_0...d_{2n-1}$ , выражение (1.3):

$$z(d_0...d_{2^n-1}x_n...x_1) = \bigvee_{j=0}^{2^n-1} \left( \bigotimes_{i=1}^n x_i^{\sigma(i,j)} d_j \right), \tag{1.3}$$

где B(1)  $\sigma(i,j)$  — показатель инверсирования соответствующей СДНФ, равный 1-B[i(j)], где B[i(j)] — бинарное представление i-го разряда числа j;  $d_j \in \{0,1\}$  — конфигурационный бит, значение функции в соответствующей строке таблицы истинности функции.

Либо для коммутации  $2^n$  сигналов (связей)  $q_j$ , выражение (1.4):

$$z(d_n \dots d_1, q) = \bigvee_{j=0}^{2^n - 1} \left( \bigotimes_{i=1}^n d_i^{\sigma(i,j)} q_j \right), \tag{1.4}$$

где  $d_i \in \{0,1\}$  – настройка одного из  $2^n$  сигналов (связей)  $q_j$  .

При этом временная задержка сигнала значения логической функции z или коммутируемого сигнала  $q_j$  составляет  $T_{pos} \geq n\tau$ ,  $\tau$  — задержка на одном п-МОП транзисторе. Неравенство связано с ограничениями на количество последовательно соединенных передающих транзисторов n типа. Сложность такой реализации оценивается в количестве транзисторов  $L_{pos}$  и соответствующей площадью кристалла  $S_{pos}$ .

Кроме того, показателем качества является потребляемая мощность  $W_{pos}$ . Объём памяти конфигурации для вычисления логической функции составляет  $2^n$  и n для коммутации сигналов. Число линий связи U для вычисления логической функции равно n. Для коммутаторов этот символ (U) означает количество ячеек конфигурационной памятью.

2) Элемент с унитарным кодированием (one hot): либо для вычисления логической функции z от n переменных x с таблицей истинности  $d_0...d_{2^n-1}$ , выражение (1.5):

$$z(d_{2^{n}-1}...d_{0}x_{2^{n}-1}...x_{0}) = \bigvee_{i=0}^{2^{n}-1} (x_{i} \cdot d_{i}), \forall x(x_{i} \& x_{j} = 0, i \neq j); \exists !x_{i} = 1, \qquad (1.5)$$

либо для коммутации  $2^n$  сигналов (связей)  $q_j$ , выражение (1.6):

$$z(d_{2^{n}-1}....d_{0},q) = \bigvee_{i=0}^{2^{n}-1} (d_{i} \cdot q_{i}), \forall d(d_{i} \& d_{j} = 0, i \neq j).$$

(1.6)

При этом временная задержка сигнала значения логической функции z или коммутируемого сигнала  $q_j$  составляет  $T_{oh} = l \cdot \tau$ . Сложность такой реализации оценивается в количестве транзисторов  $L_{oh}$  и соответствующей площадью кристалла  $S_{oh}$ . Кроме того, показателем качества является потребляемая мощность  $W_{oh}$ . Объём памяти конфигурации для вычисления логической функции одинаков с первым элементом и составляет  $2^n$  и n для коммутации n сигналов. Число линий связи  $U_{oh}$ . для вычисления логической функции равно  $2^n$  (для коммутатора это объём конфигурационной памяти). Унитарное кодирование для реализации логических функций использует разложение Шеннона [49, 77] некоторой функции f по переменной x, причем имеются и другие некоторые переменные -y, z, w, выражение (1.7):

$$f\left[(x,\overline{x}),\tilde{y},\tilde{z}...\tilde{w}\right] = x \wedge f\left[(1,0),\tilde{y},\tilde{z}...\tilde{w}\right] \vee \overline{x} \wedge f\left[(0,1),\tilde{y},\tilde{z}...\tilde{w}\right];$$

$$f\left[(x,\overline{x}),\tilde{y},\tilde{z}...\tilde{w}\right] = \left\{x \vee f\left[(0,1),\tilde{y},\tilde{z}...\tilde{w}\right]\right\} \left\{\overline{x} \vee f\left[(1,0),\tilde{y},\tilde{z}...\tilde{w}\right]\right\}.$$

(1.7)

В частности, возможен вариант с унитарным кодирование памяти конечного автомата, тем более что он имеется в САПР ПЛИС, например в [63].

3) Коммутатор с двумя группами унитарного кодирования (1.8):

$$z\Big[ (x_{0}.d_{0}) (y_{0.0}d_{0.0}...y_{0.\psi}d_{0.\psi}) \Big] ... \Big[ (x_{\zeta}d_{\zeta}) (y_{0.\zeta}d_{0.\zeta}...y_{\zeta.\psi}d_{\zeta.\psi}) \Big] =$$

$$= \Big[ \bigvee_{i=0}^{\zeta} (x_{i} \cdot d_{i}) \Big], \forall x (x_{i} \& x_{j} = 0, i \neq j); \forall y (y_{i} \& y_{j} = 0, i \neq j)$$

$$\exists ! x_{i} = 1; \exists ! y_{i,j} = 1, U_{oh,\zeta} = \zeta \cdot \psi,$$

(1.8)

где  $y_{i,j}$  – вторая группа унитарного кода для соответствующего x.

**Требуется получить**: Элемент Comb, в котором комбинируются и/или модифицируются (в дальнейшем как правило используется упрощённый термин «комбинируются») выражения (1.1) – (1.5) с целью минимизации временной задержки при заданных ограничениях (restriction) для вычисления логической функции либо для минимизации объёма конфигурационной памяти и аппаратные затраты на коммутацию межсоединений (выражение 1.9):

Временная задержка :

$$T_{comb} \to \min;$$

$U_{comb} \to \min;$   $U_{comb} \to \min;$   $U_{comb} \to \min;$   $U_{ucno}$  транзисторов :  $L_{comb} \le L_{restrict};$   $U_{comb} \le T_{restrict};$   $U_{comb} \le T_{restrict};$   $U_{non} \le T_{restrict};$   $U_{non} \le T_{restrict};$   $U_{non} \le T_{non} \le T_{non}$

Кроме того, необходимо разработать вариант универсального элемента с выбором способа кодирования. Таким образом, задача заключается в разработке научно-методического аппарата синтеза такого нового элемента, в котором комбинируется позиционное и унитарное кодирование переменных (связей) и оценке эффективности по сравнению с существующими.

Декомпозиция (1.9) позволяет получить следующие частные задачи:

- 1. Разработка математической модели элемента с комбинированным и универсальным кодированием.

- 2. Разработка метода реализации элемента с комбинированным и универсальным кодированием.

- 3. Разработка схем электрических функциональных и принципиальных предлагаемых элементов.

- 4. Схемотехническое моделирование разработанных элементов с комбинированным и универсальным кодированием.

- 5. Топологическое моделирование разработанных элементов с комбинированным и универсальным кодированием.

- 6. Получение оценок сложности и эффективности различных вариантов комбинированного кодирования;

- 7. Апробация и внедрение.

#### 1.4 Выводы по главе 1

- 1. Актуальность практической задачи подтверждается увеличением объема использования ПЛИС в областях, требующих повышенного быстродействия, в которых ранее применялись только заказные микросхемы.

- 2. Актуальность научной задачи подтверждается ростом числа публикаций в области методов синтеза логических элементов ПЛИС.

- 3. Существующие логические элементы ПЛИС, количество переменных которых достигает восьми, могут быть улучшены путем принятия мер по снижению временной задержки, такая потребность имеется, особенно в критических приложениях, в том числе в военной технике.

- 4. Современный научно-методический аппарат синтеза логических элементов ПЛИС и коммутаторов межсоединений не в полной мере использует возможные варианты комбинирования известных подходов, в том числе группирования унитарных кодов, комбинирования позиционного и унитарного кодирования.

- 5. Для разработки новых вариантов кодирования необходимо создание соответствующих модели, метода и алгоритма синтеза комбинированного элемента, в том числе и для вычисления логических функций.

# ГЛАВА 2. РАЗРАБОТКА МАТЕМАТИЧЕСКОЙ МОДЕЛИ, МЕТОДА И АЛГОРИТМА СИНТЕЗА ЭЛЕМЕНТОВ ПЛИС ТИПА FPGA С ИСПОЛЬЗОВАНИЕМ КОМБИНИРОВАННОГО КОДИРОВАНИЯ

### 2.1 Модель элемента LUT<sub>роз</sub> с бинарным (позиционным) кодированием входных переменных или настройки

Реализация логических функций в ПЛИС типа FPGA в LUT [1, 2] основана на вычислении значения одной функции z от n аргументов  $x_i$ , заданной в совершенной дизъюнктивной нормальной форме (СДНФ) выражение (1.1) — линейное представление логической функции, которое может быть реализовано, например, стандартными логическими элементами в некотором технологическом базисе. Более компактное представление основано на использовании деревьев из передающих (ключевых) n-МОП транзисторов.

В таком случае (1.1) реализуется либо параллельным соединением 2n цепочек из n передающих транзисторов (2.1) (одноуровневым 2n деревом, с 2n ветвями по n транзисторов, корень дерева, реализующий операцию монтажного ИЛИ (wired OR), d – настройка на заданную функцию, выражение (2.1):

$$z(d_{0}...d_{2^{n}-1}x_{n}...x_{1}) = \frac{d_{2^{n}-1}x_{1}...x_{n}}{d_{2^{n}-2}x_{1}...x_{n}}$$

$$\underbrace{d_{1}x_{1}...x_{n}}_{d_{0}x_{1}...x_{n}}$$

$$(2.1)$$

либо, с целью уменьшения количества транзисторов, n-уровневым бинарным деревом транзисторов, выражение (2.2):

$$z(d_{0}...d_{2^{n}-1}x_{n}...x_{1}) = \underbrace{\begin{array}{c} \frac{d_{0}x_{1}}{d_{1}x_{1}} \\ \vdots \\ \frac{x_{n-1}}{x_{n}} \frac{x_{n}}{x_{n}} \\ \vdots \\ \frac{d_{2^{n}-2}x_{1}}{x_{n}} \frac{x_{n-1}}{x_{n-1}} \end{array}}_{(2.2)$$

Старшей переменной в (2.2) n — соответствуют два транзистора  $\frac{\overline{x_n}}{\underline{x_n}}$

$$\frac{d_0 \overline{x_1}}{\underline{d_1 x_1}}$$

младшей -2n транзисторов (2n/2 для x и 2n/2 для HE x):

$\frac{d_{2^{n}-2}\bar{x}_{1}}{d_{2^{n}-1}x_{1}}$

В связи с ограничениями Мида-Конвей [26, 54] на число последовательно соединенных передающих p-МОП транзисторов (<=4, как правило, используют <=3, что связано со снижением высокого логического уровня после каждого транзистора на величину порогового напряжения) используют, как базовые, деревья для n=1,2,3, выражение (2.3):

$$z(d_{0}d_{1}x_{1}) = \frac{d_{0}\overline{x}_{1}}{\underline{d_{1}x_{1}}} \left\{ (\vee \bullet); z(d_{0}...d_{3}x_{2}x_{1}) = \underbrace{\frac{d_{0}\overline{x}_{1}}{\underline{d_{1}x_{1}}}}_{\underline{x_{2}}} \right\}_{\underline{x_{2}}} (\vee \bullet); z(d_{0}...d_{3}x_{2}x_{1}) = \underbrace{\frac{d_{0}\overline{x}_{1}}{\underline{d_{2}x_{1}}}}_{\underline{x_{2}}} \underbrace{\frac{d_{1}x_{1}}{\underline{x_{2}}}}_{\underline{x_{2}}} \underbrace{\frac{d_{2}x_{1}}{\underline{x_{2}}}}_{\underline{d_{2}x_{1}}} \underbrace{\frac{d_{2}$$

LUT на одну переменную используется и для объединения, например, LUT на две и три переменные, а также и как инвертор, и как повторитель, в случае необходимости трассировки через него некоторой связи.

Из этих деревьев строят деревья для реализации функций для n=4, а в современных ПЛИС и для n=5,6,7,8... в так называемых адаптивных логических модулях (АЛМ) [5, 6, 8, 49, 51, 52].

В этом случае в промежуточных деревьях вместо настройки  $d_j$  могут указываться связи  $c_j$ . Кроме того, с целью восстановления уровня сигнала используют так называемые восстановители v (в простейших случаях это инверторы или пары инверторов, NOT Gates) по входам настройки или коммутации и по выходам функции, например, LUT на четыре переменные будет представлять собой выражение (2.4):

$$\frac{\overline{d}_{0}v_{4,0}\overline{x}_{1}}{\overline{d}_{1}v_{4,1}x_{1}} \frac{\overline{x}_{2}}{x_{2}} \frac{\overline{d}_{3}v_{4,3}x_{1}}{x_{2}} \frac{\overline{x}_{2}}{x_{3}} \frac{\overline{d}_{3}v_{4,3}x_{1}}{x_{2}} \frac{\overline{x}_{3}}{x_{2}} \frac{\overline{d}_{3}v_{4,5}x_{1}}{x_{2}} \frac{\overline{d}_{3}v_{4,5}x_{1}}{x_{2}} \frac{\overline{d}_{3}v_{4,5}x_{1}}{\overline{d}_{1}v_{4,7}x_{1}} \frac{\overline{d}_{3}v_{4,8}\overline{x}_{1}}{\overline{d}_{1}v_{4,11}x_{1}} \frac{\overline{d}_{3}v_{4,12}\overline{x}_{1}}{x_{2}} \frac{\overline{d}_{3}v_{4,12}\overline{x}_{1}} \frac{\overline{d}_{3}v_{4,12}\overline{x}_{1}}{x_{2}} \frac{\overline{d}_{3}v_{4,13}x_{1}}{\overline{d}_{1}sv_{4,13}x_{1}} \frac{x_{2}}{x_{2}} \frac{\overline{d}_{3}v_{4,13}x_{1}}{\overline{d}_{1}sv_{4,15}x_{1}} \right\} (\vee \bullet)v_{3}$$

$$(2.4)$$

В (2.4) v — это функции повторения, восстановители, поскольку их нечетное число в цепочках (три), поэтому настройка функции инверсная, настройка LUT на одну переменную не используется. Такое устройство называется просто мультиплексором 2-1. Например, в [49, 51] описана так называемая декомпозиция полного двоичного сумматора, использующего двухвходовые LUT и мультиплексоры 2-1, в этом случае получаем для одной из функций, выражение (2.5):

$$\frac{d_0 \overline{x_1}}{d_1 x_1} \xrightarrow{\underline{x_2}} \left\{ (\checkmark \bullet) \right\}$$

$$\frac{d_2 \overline{x_1}}{d_3 x_1} \xrightarrow{\underline{x_2}} \left\{ (\checkmark \bullet) \right\}$$

$$\frac{d_2 \overline{x_1}}{d_3 x_1} \xrightarrow{\underline{x_2}} \left\{ (\checkmark \bullet) \right\}$$

$$\frac{d_4 \overline{x_1}}{d_5 x_1} \xrightarrow{\underline{x_2}} \left\{ (\checkmark \bullet) \right\}$$

$$\frac{d_6 \overline{x_1}}{d_7 x_1} \xrightarrow{\underline{x_2}} \left\{ (\checkmark \bullet) \right\}$$

(2.5)

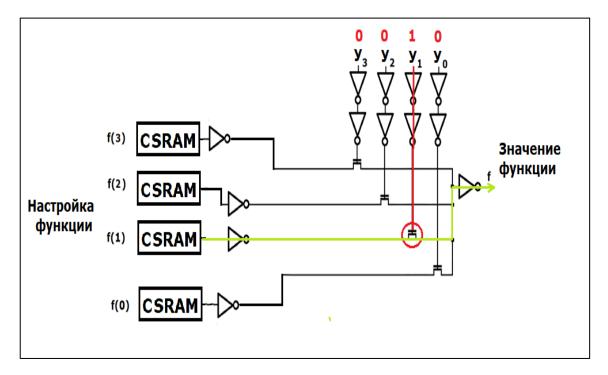

В (2.5) и далее для упрощения выражений в ряде случаев не указаны функции восстановителей, но они подразумеваются. В элементе LUT входным сигналом является набор двоичных переменных, например, для (2.5) при значении переменных 000 функция  $z(x_3x_2x_1)=d_0$  при значении переменных 111 функция  $z(x_3x_2x_1)=d_7$ .

# 2.2 Модель элемента $LUT_{oh}$ , использующего унитарное кодирование входных переменных или настройки

Унитарное кодирование используется для реализации коммутаторов межсоединений (рисунок 1.4). При использовании унитарного кодирования входных переменных для вычисления логических функций получаем выражение (2.6). В этом случае дерево (2.2) будет иметь только одну переменную в ветви:

$$z(d_{2^{n}-1}...d_{0}x_{2^{n}-1}...x_{0}) = \frac{\frac{d_{2^{n}-1}x_{2^{n}-1}}{d_{2^{n}-2}x_{2^{n}-2}}}{\frac{d_{1}x_{1}}{d_{0}x_{0}}}$$

(2.6)

где  $x_{2^{n}-1} \dots x_{0}$  — например, «прямой» унитарный код (всегда одна единица в наборе, one-hot), что уменьшает путь сигнала в количестве транзисторов (временную задержку) от конфигурационной памяти, хранящей константы, на выход в n раз, но и увеличивает длину набора переменных  $x_{2^{n}-1} \dots x_{0}$  в  $\frac{2^{n}}{n}$  раз по сравнению с набором  $x_{n} \dots x_{0}$ .

Так, для реализации функции трех аргументов в унитарном коде, получим выражение (2.7):

$$z(d_{7}...d_{0}x_{7}...x_{1}x_{0}) = \frac{\underline{d_{6}x_{6}}}{...} \begin{cases} (\checkmark \bullet). \\ \underline{d_{1}x_{1}} \\ \underline{d_{0}x_{0}} \end{cases}$$

(2.7)

Например, для (2.7) при значении унитарного кода переменных 00000001 функция  $z(00000001)=d_0$ , при значении переменных 10000000 функция  $z(10000000)=d_7$ . Здесь (2.7) выходная функция z не закодирована унитарным кодом.

В настоящее время унитарный код используется в коммутаторах связей [2,78], в таком случае в выражениях (2.7)  $d_i$  — соответствующая связь в матрице глобальной или локальной коммутации. Настройка же, наоборот, осуществляется по входам переменных унитарным кодом.

Для коммутации связей с целью уменьшения конфигурационной памяти также может использоваться и позиционный код (2.2) с тем же уточнением.

Выражение (2.7) описывает вычисление одной функции в позиционном коде. Для получения унитарного кода функции  $z(d_{2^{n}-1} \dots d_{0}x_{2^{n}-1} \dots x_{0})$  можно, конечно, просто выполнить отрицание и получить  $\bar{z}(d_{2^{n}-1} \dots d_{0}x_{2^{n}-1} \dots x_{0})$ , но дополнительное выражение (2.8)

$$z_{0}(d_{0.2^{n}-1}x_{0.2^{n}-1}) = \frac{d_{0.2^{n}-1}x_{0.2^{n}-1}}{d_{0.2^{n}-2}x_{0.2^{n}-2}}$$

$$z_{0}(d_{0.2^{n}-1}...d_{0.0}x_{2^{n}-1}...x_{0}) = \frac{d_{0.1}x_{0.1}}{d_{0.0}x_{0.0}}$$

$$z_{1}(\overline{d}_{1.2^{n}-1}...\overline{d}_{1.0}x_{2^{n}-1}...x_{0}) = \frac{d_{1.2^{n}-1}x_{1.2^{n}-1}}{d_{1.2^{n}-2}x_{1.2^{n}-2}}$$

$$z_{1}(\overline{d}_{1.2^{n}-1}...\overline{d}_{1.0}x_{2^{n}-1}...x_{0}) = \frac{d_{1.1}x_{1.1}}{d_{1.0}x_{1.0}}$$

$$(2.8)$$

позволяет осуществлять контроль достоверности вычислений значения функции, например, путем сложения по модулю 2 двух её значений, что важно при диагностике ПЛИС, например, с использованием подходов, описанных в [18, 19, 20, 37]. Переменные дублируются, поэтому указаны индексы.

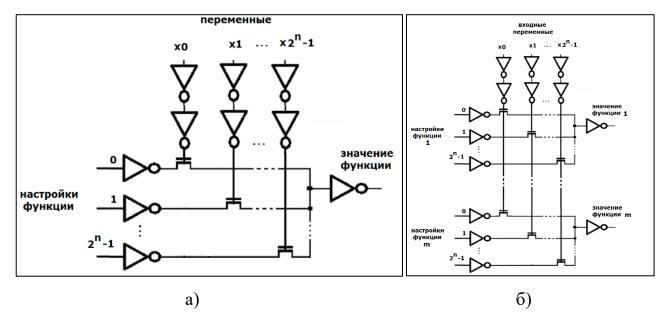

Аналогично можно вычислить систему m различных функций, допустим f от одних и тех же переменных  $x_{2^{n}-1}...x_{0}$  в позиционном коде, используя m копий входных переменных – выражение (2.9).

Уточним выражение (2.9) для случая представления системы m функций F в унитарном коде следующим образом, получим выражение (2.10).

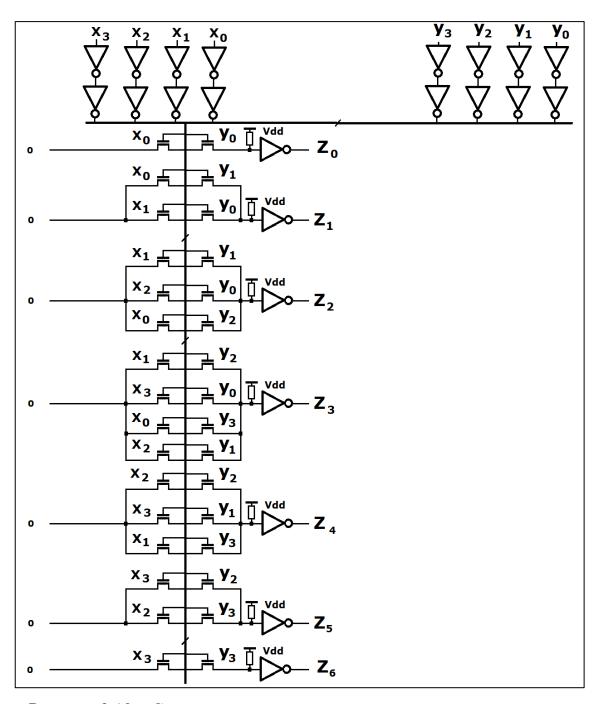

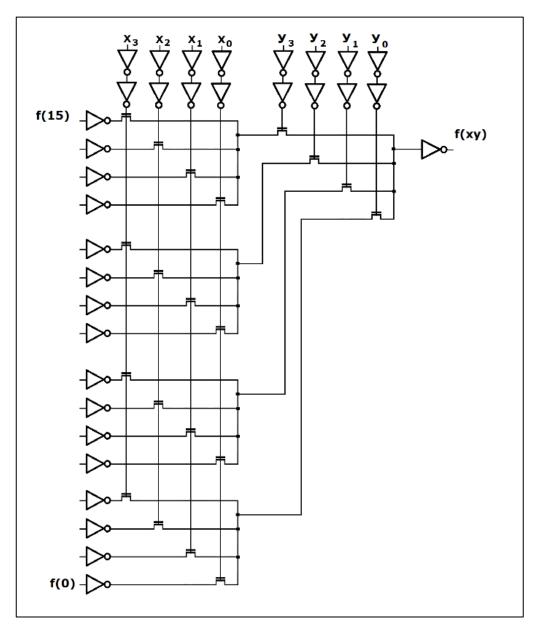

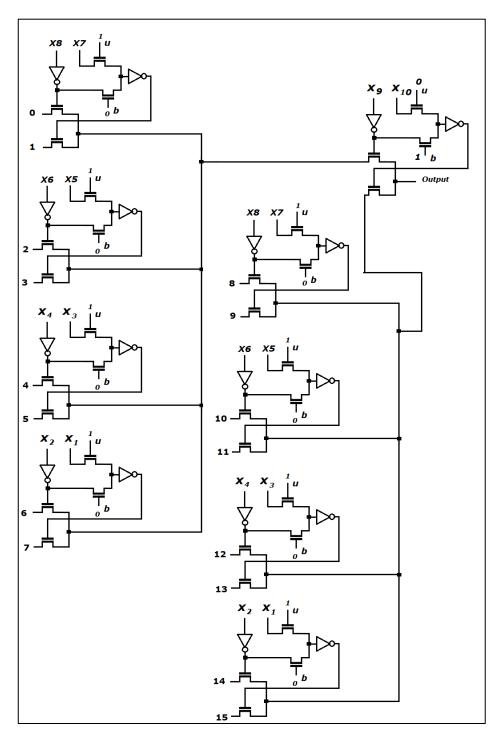

Для снижения длины унитарного кода (объема конфигурационной памяти) возможна двух координатная коммутация [2, 21, 49], что предлагается применить и для вычисления системы m функций F и h функций G в унитарном коде по двум позиционным входным векторам x, y, размерности соответственно, например q и r – выражение (2.11).

$$f_{1}(d_{f_{1},2^{n}-1}...d_{f_{1},0}x_{2^{n}-1}...x_{0}) = \frac{d_{f_{1},2^{n}-2}x_{1,2^{n}-2}}{d_{f_{1},1}x_{1,1}} \\ \frac{d_{f_{1},1}x_{1,1}}{d_{f_{2},0}x_{1,0}} \\ = \frac{d_{f_{m},1}x_{1,1}}{d_{f_{m},0}x_{1,0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},0}x_{2^{n}-1}...x_{0}) = \frac{d_{f_{m},2^{n}-2}x_{m,2^{n}-2}}{d_{f_{m},0}x_{m,0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},0}x_{2^{n}-1}...x_{0}) = \frac{d_{f_{0},2^{n}-1}x_{1,2^{n}-1}}{d_{f_{0},0}x_{1,0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},0}x_{2^{n}-1}...x_{0}) = \frac{d_{f_{0},2^{n}-1}x_{1,2^{n}-1}}{d_{f_{0},0}x_{1,0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},0}x_{2^{n}-1}...x_{0}) = \frac{d_{f_{0},2^{n}-1}x_{1,2^{n}-1}}{d_{f_{0},0}x_{1,0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},0}x_{2^{n}-1}...x_{0}) = \frac{d_{f_{m},2^{n}-1}x_{2^{n}-1}}}{d_{f_{m},0}x_{1,0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},0}x_{2^{n}-1}...x_{0}) = \frac{d_{f_{m},2^{n}-1}x_{2^{n}-1}}}{d_{f_{m},0}x_{2^{n}-1}...x_{0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},0}x_{2^{n}-1}...x_{0}) = \frac{d_{f_{m},2^{n}-1}x_{2^{n}-1}}}{d_{f_{m},0}x_{2^{n}-1}...x_{0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},0}x_{2^{n}-1}...x_{0}) = \frac{d_{f_{m},2^{n}-1}x_{2^{n}-1}}{d_{f_{m},0}x_{2^{n}-1}...x_{0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},2^{n}-1}...x_{0}) = \frac{d_{f_{m},2^{n}-1}x_{2^{n}-1}}}{d_{f_{m},0}x_{2^{n}-1}...x_{0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},2^{n}-1}...x_{0}) = \frac{d_{f_{m},2^{n}-1}x_{2^{n}-1}}{d_{f_{m},2^{n}-1}...x_{0}} \\ f_{m}(d_{f_{m},2^{n}-1}...d_{f_{m},2^{n}-1}...x_{0}) = \frac{d_{f_{m},2^{n}-1}x_{2^{n}-1}}{d_{f_{m},2^{n}-1}...x_{0}} \\ f_{m}(d_{f_{m},2^{n}-1}...x_{0}) = \frac{d_{f_{m},2^{n}-1}x_{2^{n}-1}$$

$$F_{2^{m}-1}(d_{f_{m}\cdot2^{n}-1}...d_{f_{m}\cdot0}x_{2^{n}-1}...x_{0}) = \underbrace{\frac{d_{F_{2^{m}-1}\cdot2^{n}-2}x_{m\cdot2^{n}-2}}{d_{F_{2^{m}-1}\cdot2^{n}-2}x_{m\cdot2^{n}-2}}}_{\dots \underbrace{\frac{d_{F_{2^{m}-1}\cdot1}x_{m\cdot1}}{d_{F_{2^{m}-1}\cdot0}x_{m\cdot0}}}_{d_{F_{2^{m}-1}\cdot0}x_{m\cdot0}}}$$

(2.10)

Аналогично можно предложить и трех координатное унитарное кодирование, в общем же случае d координат имеется путь из d p-МОП транзисторов, то есть временная задержка увеличивается, но длина кода (и, соответственно, объем конфигурационной памяти) уменьшается с  $2^n$  до  $d \cdot o$ , где o — размерность одной координаты,  $n = \lceil \log(d \cdot o, 2) \rceil$ , где  $\lceil \rceil$  ближайшее большее натуральное число,  $\log(d \cdot o, 2)$  — двоичный логарифм.

При многокоординатном позиционном кодировании длина кода не уменьшается, выигрыша во временной задержке также не происходит.

$$F_{0}(d_{F_{0},r\cdot q}...d_{F_{0,1}}y_{2^{r}-1}...y_{0}x_{2^{q}-1}...x_{0}) = \underbrace{\frac{d_{F_{0,r\cdot q}.}y_{0,2^{r}-1}x_{0,2^{q}-1}}{d_{F_{0,r\cdot q}-1}...y_{0,2^{r}-2}x_{0,2^{q}-1}}}_{\underbrace{\frac{d_{F_{0,r\cdot q}-1}...x_{0}}}_{d_{F_{0}.1}y_{0,0}x_{0,0}}}] (\vee \bullet);$$

$$F_{2^{m}-1}(d_{F_{2^{m}-1},r\cdot q}...d_{F_{2^{m}-1,1}}y_{2^{r}-1}...y_{0}x_{2^{q}-1}...x_{0}) = \underbrace{\frac{d_{F_{2^{m}-1,r\cdot q}},y_{0.2^{r}-1}x_{0.2^{q}-1}}{d_{F_{2^{m}-1,r\cdot q}}y_{0.2^{r}-2}x_{0.2^{q}-1}}}_{\dots} \left\{ \underbrace{\frac{d_{F_{2^{m}-1,r\cdot q-1}}y_{0.2^{r}-2}x_{0.2^{q}-1}}_{\dots}}_{d_{F_{2^{m}-1},0}y_{0.0}x_{0.0}} \right\} (\vee \bullet);$$

$$G_{0}(d_{G_{0},r\cdot q}....d_{G_{0,1}}y_{2^{r}-1}...y_{0}x_{2^{q}-1}...x_{0}) = \underbrace{\frac{d_{G_{0,r\cdot q}.}y_{0.2^{r}-1}x_{0.2^{q}-1}}{d_{G_{0,1}}y_{0.2^{r}-2}x_{0.2^{q}-1}}}_{\underbrace{d_{G_{0,1}}y_{0.1}x_{0.0}}_{\underbrace{d_{G_{0,0}}y_{0.0}x_{0.0}}}}\right\}(\vee \bullet);$$

$$G_{2^{h}-1}(d_{G_{0},r\cdot q}...d_{G_{0,1}}y_{2^{r}-1}...y_{0}x_{2^{q}-1}...x_{0}) = \underbrace{\frac{d_{G_{2^{h}-1,r\cdot q}}.y_{0,2^{r}-2}x_{0,2^{q}-1}}{d_{G_{2^{h}-1,r\cdot q}-1}.y_{0,2^{r}-2}x_{0,2^{q}-1}}}_{d_{G_{2^{h}-1,1}}y_{0,1}x_{0,0}}$$

$$\underbrace{\frac{d_{G_{2^{h}-1,r\cdot q}-1}.y_{0,2^{r}-2}x_{0,2^{q}-1}}_{d_{G_{2^{h}-1,1}}y_{0,1}x_{0,0}}}_{d_{G_{2^{h}-1,0}}y_{0,0}x_{0,0}}}$$

$$(2.11)$$

Получаем  $q \cdot r$  бит вместо  $2^{q+r}$  бит, однако это несколько увеличивает задержку за счет использования двух переменных х, у.

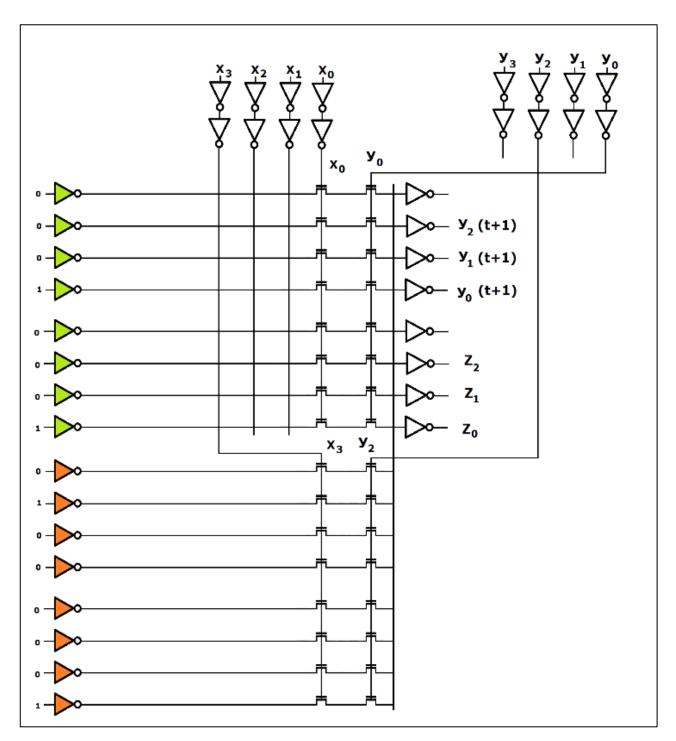

Предлагается комплексирование выражений по унитарной переменной, допустим, y, которая будет подключать k разрядный LUT с настроечными векторами D для реализации некоторой функции z – выражение (2.12):

$$z(\overrightarrow{D}_{2^{n}-1}...\overrightarrow{D}_{0}y_{2^{n}-1}...y_{0}x_{1}...x_{k}) = \underbrace{\frac{\overrightarrow{D}_{2^{n}-1}x_{1}...x_{k}y_{2^{n}-1}}{D_{2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}}}_{\underbrace{D_{1}x_{1}...x_{k}y_{1}}}_{\underbrace{D_{0}x_{1}...x_{k}y_{0}}}$$

(2.12)

Предложенное выражение (2.12) используется для получения системы функций Z в унитарном — выражение (2.13):

$$\vec{Z}_{\xi}(\vec{D}_{\xi,2^{n}-1}....\vec{D}_{\xi,0}y_{2^{n}-1}...y_{0}x_{1}...x_{k}) = \underbrace{\frac{\vec{D}_{\xi,2^{n}-1}x_{1}...x_{k}y_{2^{n}-1}}{\vec{D}_{\xi,2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}}}_{\underbrace{\vec{D}_{\xi,1}x_{1}...x_{k}y_{1}}}_{\underbrace{\vec{D}_{\xi,0}x_{1}...x_{k}y_{0}}} \right\} (\lor \bullet), \xi = 0...2^{m}, \tag{2.13}$$

либо в позиционном коде – выражение (2.14):

$$\vec{Z}_{\zeta}(\vec{D}_{\zeta,2^{n}-1}....\vec{D}_{\zeta,0}y_{2^{n}-1}...y_{0}x_{1}...x_{k}) = \frac{\vec{D}_{\zeta,2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}}{\vec{D}_{\zeta,2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}} \\

\underbrace{\vec{D}_{\zeta,2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}}_{....} \\

\underbrace{\vec{D}_{\zeta,1}x_{1}...x_{k}y_{1}}_{\vec{D}_{\zeta,0}x_{1}...x_{k}y_{0}}$$

$$(2.14)$$

либо и в том, и другом для разных функций, например, Z (позиционный) и Y (унитарный) — выражение (2.15):

$$\overrightarrow{D}_{\xi,2^{n}-1}x_{1}...x_{k}y_{2^{n}-1}$$

$$\overrightarrow{D}_{\xi,2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}$$

$$\overrightarrow{D}_{\xi,2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}$$

$$\underbrace{D_{\xi,2^{n}-2}x_{1}...x_{k}y_{1}}_{D_{\xi,0}x_{1}...x_{k}y_{0}}$$

$$\underbrace{D_{\xi,2^{n}-1}x_{1}...x_{k}y_{1}}_{D_{\xi,0}x_{1}...x_{k}y_{0}}$$

$$\overrightarrow{D}_{\xi,2^{n}-1}x_{1}...x_{k}y_{1}$$

$$\underbrace{D_{\xi,2^{n}-1}x_{1}...x_{k}y_{2^{n}-1}}_{D_{\xi,2^{n}-1}x_{1}...x_{k}y_{2^{n}-2}}$$

$$\underbrace{D_{\xi,2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}}_{D_{\xi,2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}}$$

$$\underbrace{D_{\xi,2^{n}-2}x_{1}...x_{k}y_{2^{n}-2}}_{D_{\xi,0}x_{1}...x_{k}y_{0}}$$

$$\underbrace{D_{\xi,1}x_{1}...x_{k}y_{1}}_{D_{\xi,0}x_{1}...x_{k}y_{0}}$$

$$\underbrace{D_{\xi,1}x_{1}...x_{k}y_{1}}_{D_{\xi,0}x_{1}...x_{k}y_{0}}$$

$$(2.15)$$

Таким образом, получены выражения (2.6–2.15) для вычисления логической функции с использованием только унитарного кода, причем функция или системы функций также представляются в унитарном коде. Это позволяет уменьшить временную задержку за счет увеличения длины кода.

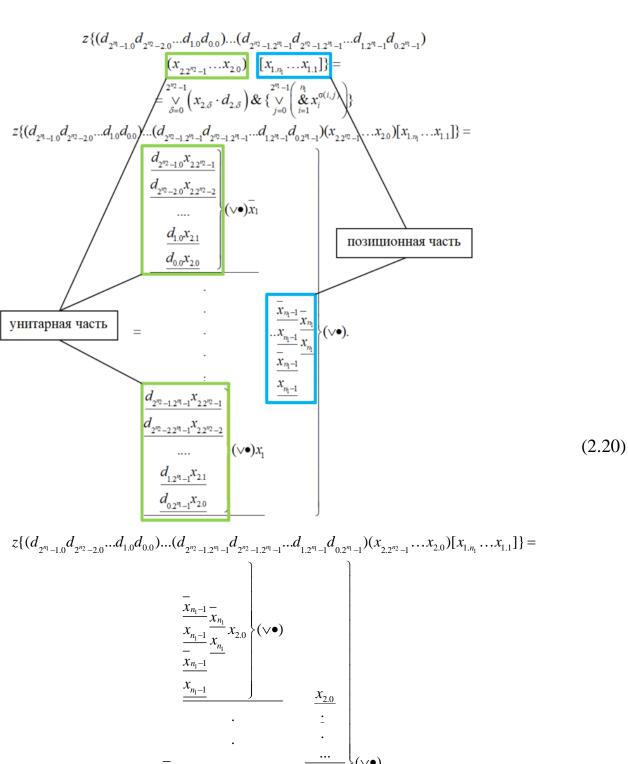

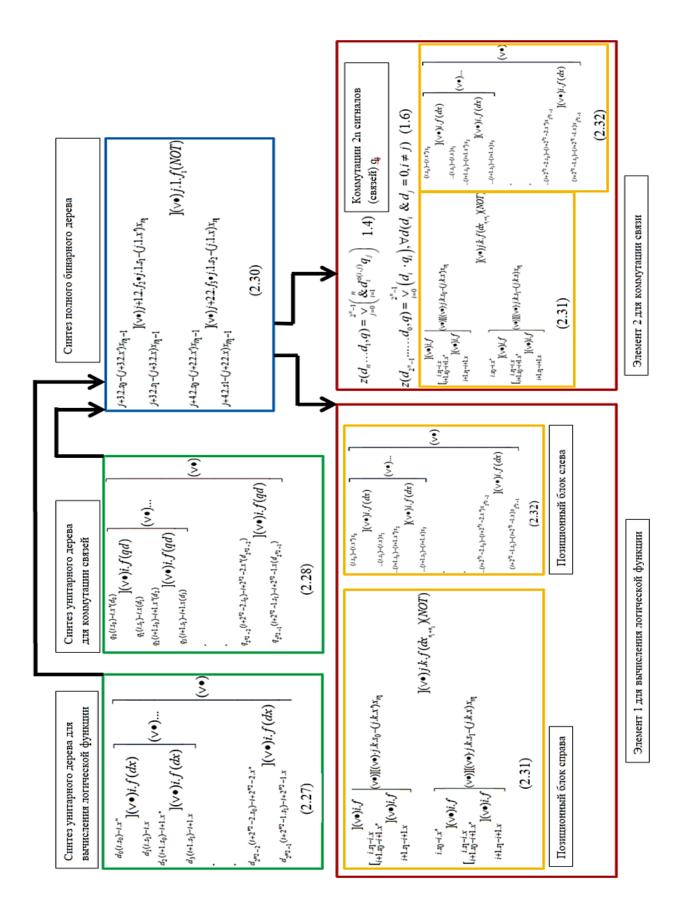

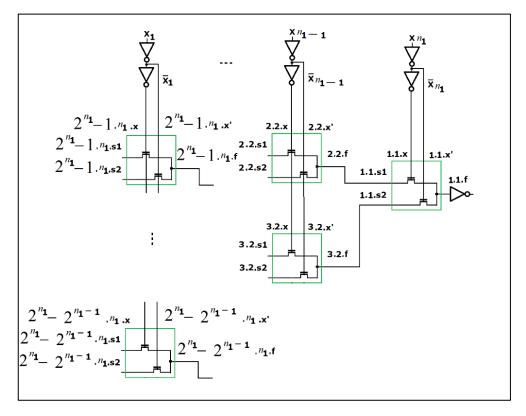

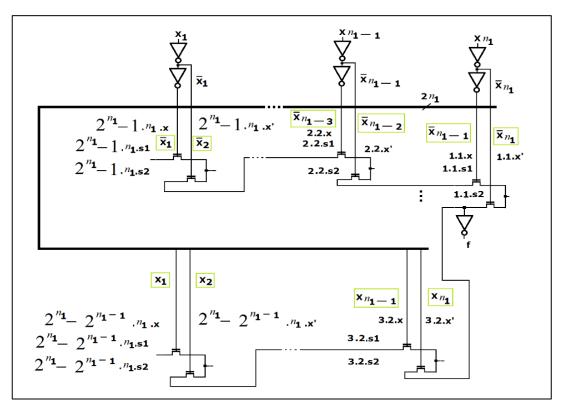

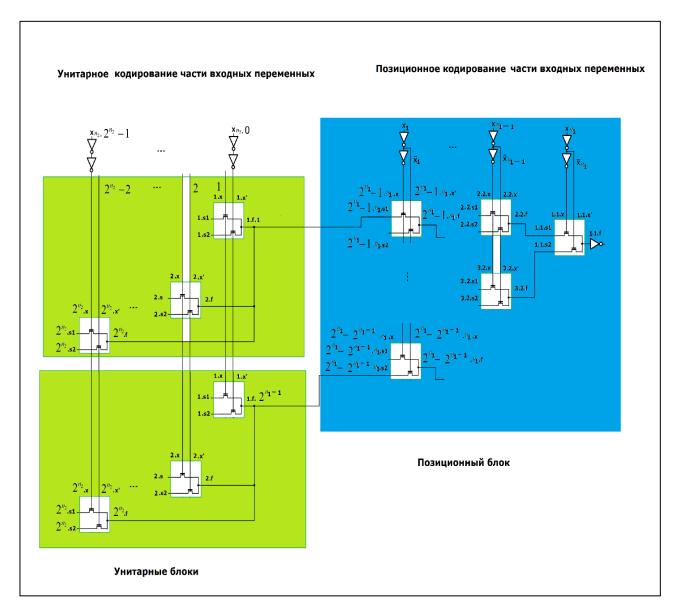

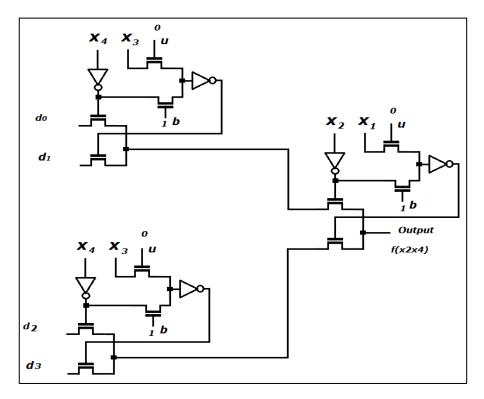

#### 2.3 Разработка модели предлагаемого комбинированного элемента

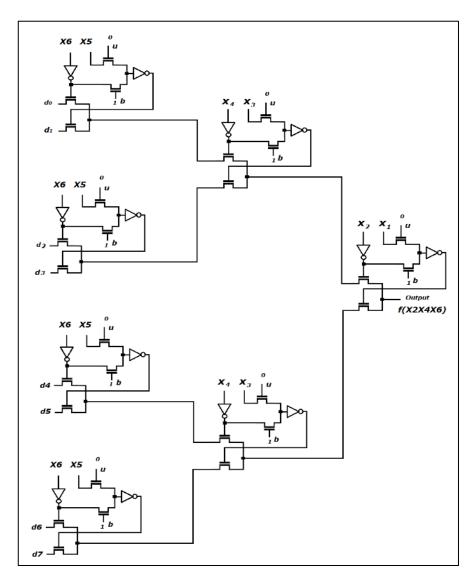

Обычный (бинарный или позиционный) LUT (1,1), (1.2), (2.2), (2.3) также использует унитарные коды, но отдельно по каждой переменной. Расширяя такое представление, мы получили унитарный LUT по всем переменным (2.6)...(2.15). Но, можно «сделать и шаг назад», рассматривая LUT с унитарными кодами по группам переменных, например, получим две группы по две переменные. Получаем выражение (2.16).

Тогда (2.16) мы уменьшаем задержку в два раза, но вместо четырех разрядов переменных имеем восемь. Подсчитаем сложность такого LUT для вычисления любой функции четырех переменных. Очевидно, что сложность настройки будет такая же, как и в обычном (позиционном) LUT:  $16\cdot(6+2)=128$  транзисторов.

$$z(\{d_{0}...d_{15}\}[x_{2.3}x_{2.2}x_{2.1}x_{2.0}][x_{1.3}x_{1.2}x_{1.1}x_{1.0}]) = \underbrace{\frac{x_{1.0}}{x_{1.1}}}_{\cdot} \underbrace{\frac{x_{1.0}}{x_{1.2}}}_{\cdot} \underbrace{\frac{x_{1.0}}{x_{1.3}}}_{\cdot} \underbrace{\frac{x_{1.2}}{x_{1.2}}}_{\cdot} \underbrace{\frac{x_{1.2}}{x_{1.$$

Транзисторов в дереве имеем 4·4+4=20. В обычном (бинарном или позиционном) LUT их 30. Восстановителей входных переменных будет 4·4=16. Получаем 36=20+16. Сложность 2-LUT равна 6+2+8=16 (6 транзисторов в дереве + 5 инверторов=10). Итого 52 против 48 транзисторов в обычном LUT. Линий связи надо в два раза больше – восемь, вместо четырёх. Но выигрыш в задержке может того стоить.

Предлагаемый подход позволяет снизить задержку вычисления функций большого числа переменных. Например, можно использовать унитарный код по группам трёх переменных и вычислять логическую функцию девяти переменных на унитарном дереве с тремя уровнями, получаем выражение (2.17).

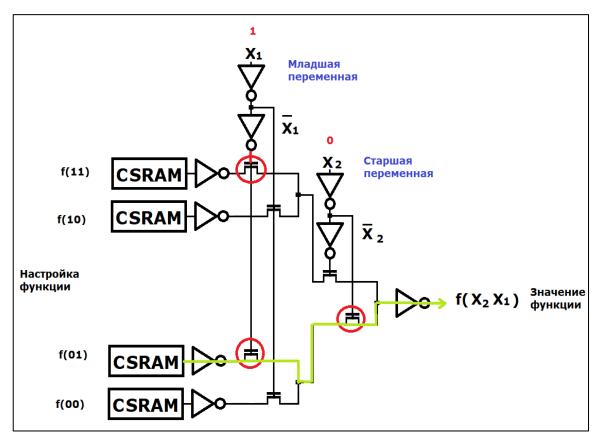

Комбинирование унитарного и обычного LUT рассмотрим на примере двух переменных *ba* позиционного кода — выражение 2.18. Выражение (2.18) может быть в разных подвариантах в зависимости от того, что слева, что справа: сначала унитарный, потом бинарный (позиционный) или наоборот.

$$z(\{d_{0}...d_{511}\}[x_{37}...x_{32}x_{3.1}x_{30}]...[x_{1,7}...x_{12}x_{1.1}x_{10}]) = \begin{bmatrix} & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & \\ & & & \\ & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ &$$

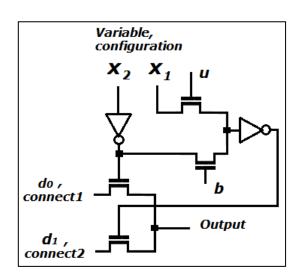

**Таким образом, получаем модель** комбинированного элемента, в которой модифицируется унитарная модель путем разбиения на группы, либо комбинируется путем соединения унитарной и позиционной моделей.

В этом случае n переменных разбиваются на две группы, а настройка логической функции осуществляется по нескольким унитарным блокам размерностью  $n_2$ , количество которых равно количеству конституент единицы в единственном позиционном блоке размерностью  $n_1$ .

В линейной форме получим выражение (2.19):

$$z\{(d_{2^{n_{1}}-1.0}d_{2^{n_{2}}-2.0}...d_{1.0}d_{0.0})...(d_{2^{n_{2}}-1.2^{n_{1}}-1}d_{2^{n_{2}}-1.2^{n_{1}}-1}...d_{1.2^{n_{1}}-1}d_{0.2^{n_{1}}-1})$$

$$(x_{2.2^{n_{2}}-1}...x_{2.0}) \quad [x_{1.n_{1}}...x_{1.1}]\} =$$

$$= \bigvee_{\delta=0}^{2^{n_{2}}-1} (x_{2.\delta} \cdot d_{2.\delta}) \& \{\bigvee_{j=0}^{2^{n_{1}}-1} \binom{n_{1}}{k} x_{i}^{\sigma(i,j)}\},$$

$$(2.19)$$

где  $\sigma(i,j)$  — показатель инверсирования соответствующей СДНФ, позиционного блока, равный 1-B[i(j)], где B[i(j)] — бинарное представление i-го разряда числа  $j;\ d_j \in \{0,1\}$  — конфигурационный бит, значение функции в соответствующей строке таблицы истинности функции z.

Получаем выражение (2.20) в виде комбинированного дерева:

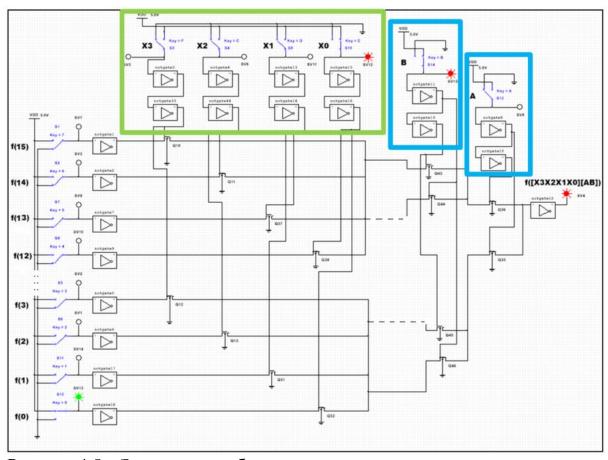

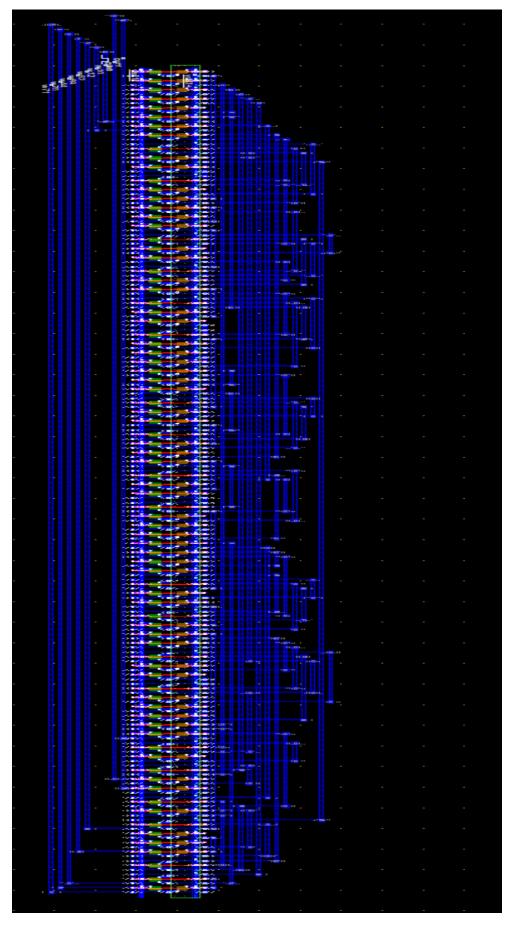

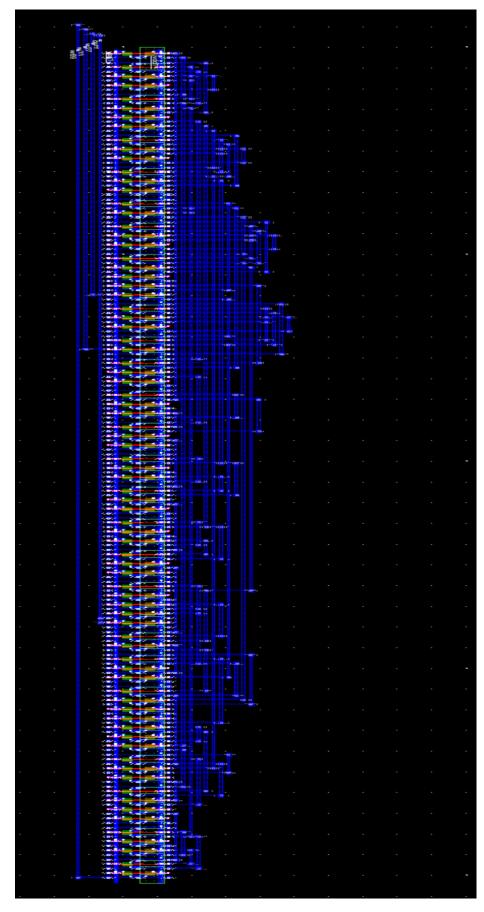

Рамка зеленого цвета обозначает унитарную часть, а синяя позиционную.

В дальнейшем целесообразно исследовать предлагаемые варианты и оценить их эффективность с помощью моделирования и получения показателей сложности.

Другой вариант комбинирования представляет собой выражение (2.21):

$$\frac{\underline{x_{n_{1}-1}}}{\underline{x_{n_{1}-1}}} \underbrace{\frac{x_{2.0}}{\underline{x_{2.0}}}}_{\underline{x_{2.0}}} \underbrace{\frac{x_{2.0}}{\underline{x_{2.0}}}}_{\underline{x_{2.0}}} \underbrace{(\vee \bullet)}_{\underline{x_{n_{1}-1}}} \underbrace{\frac{x_{n_{1}-1}}{x_{n_{1}-1}}}_{\underline{x_{n_{1}-1}}} \underbrace{x_{n_{1}-1}}_{\underline{x_{n_{1}-1}}} \underbrace{(\vee \bullet)}_{\underline{x_{n_{1}-1}}} \underbrace{(\vee$$

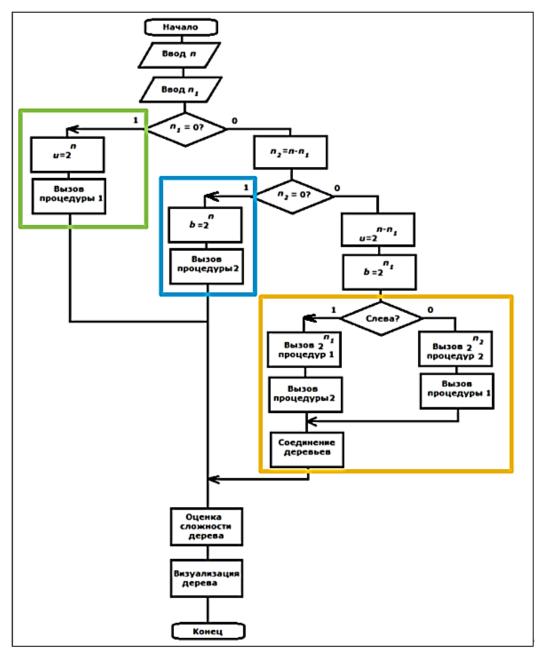

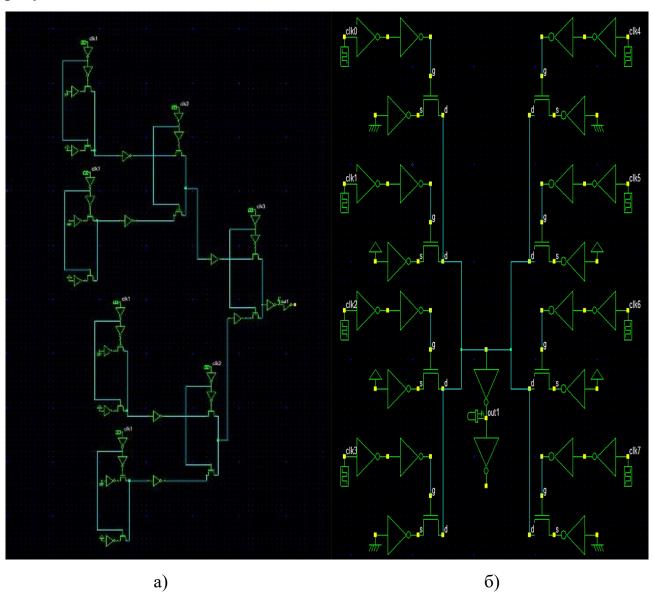

## 2.4 Разработка метода синтеза элементов ПЛИС типа FPGA с использованием комбинированного кодирования

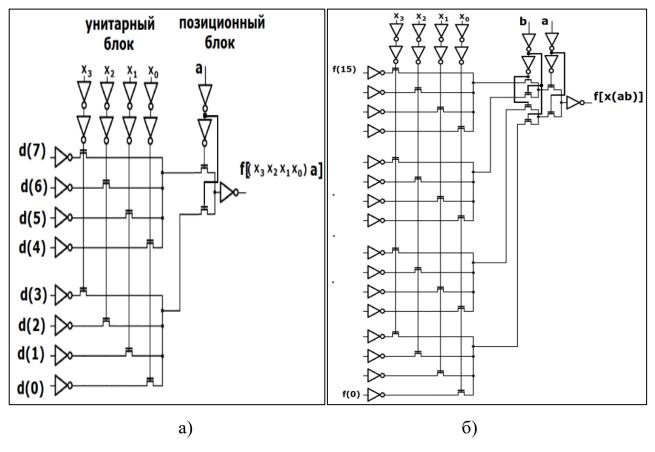

Сущность предлагаемого метода, позволяющего строить элементы в соответствие моделями (2.20), (2.21), заключается в следующем.

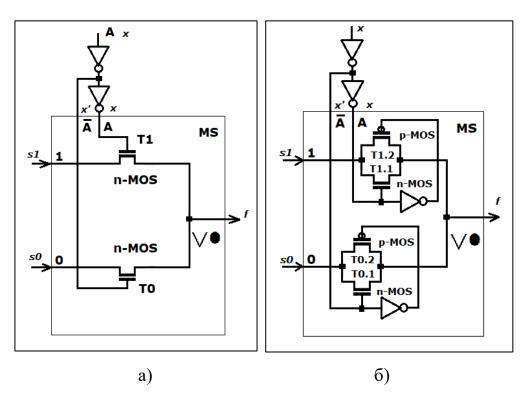

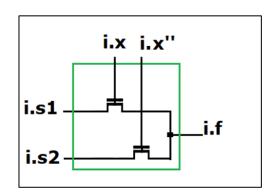

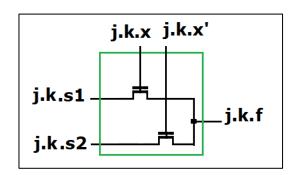

Дано выражение (2.22) элементарных мультиплексоров 2-1 из двух передающих транзисторов n-МОП (или двух КМОП ключей [1, 2]) j.k.x, j.k.x' k-уровень дерева от n до 1 (старшая переменная — уровень 1, но переменная n):

$$j.k.s_0 - j.k.x'$$

$$j.k.s_1 - j.k.x$$

$$(2.22)$$

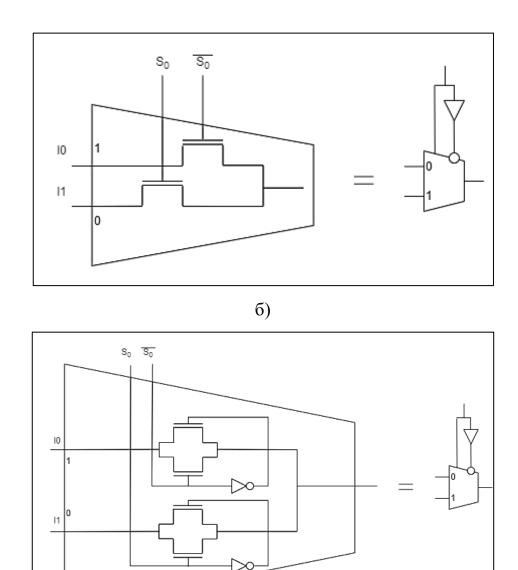

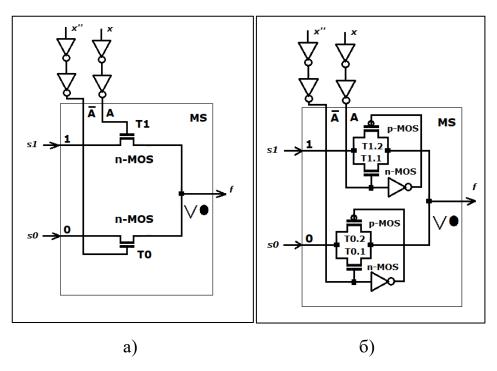

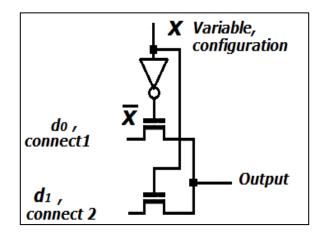

В (2.22) «—» означает соответствующую связь, « $](\lor \bullet)$ » означает корень дерева, реализующий операцию «Монтажное ИЛИ». В этом случае сигналы j.k.x, j.k.x'инверсны (ортогональны), то есть на выходе i.f всегда имеется некоторый логический уровень. На рисунке.2.1 показана реализация (2.22) в виде мультиплексора 2-1 (1-LUT).

Рисунок 2.1 — Мультиплексор 2-1 (1-LUT): а) на базе n-МОП транзисторов; б) на базе КМОП транзисторов

Транзистор n-МОП Т0 (рисунок 2.1 а) получает на исток некоторый сигнал i.s.0, который в случае i.x'=1 передает на выход i.f сигнал i.s.1. Транзистор n-МОП Т1 получает на исток некоторый сигнал i.s.1, который в случае i.x=1 передает на выход i.f сигнал i.s.1. Аналогично работают КМОП-ключи, показанные на рисунке 2.1,6, более предпочтительные при передаче сигналов уровня логического нуля, но и более сложные.

Также имеется выражение (2.23) элементарных коммутаторов 2-1 из двух передающих транзисторов n-МОП i.x, i.x'', где i- номер мультиплексора (или итерации):

$$i.s_0-i.x$$

"

$$](\vee \bullet)i.f.$$

$i.s_1-i.x$  (2.23)

Сигналы i.x, i.x" таковы, что если один равен единице, то другой равен нулю, иначе оба нуля. То есть на выходе i.f может и не быть логического уровня. На рисунке 2.2 показана реализация (2) в виде коммутатора 2-1 (1-LUT).

Рисунок 2.2 — Коммутатор (унитарный 1-LUT) 2-1: а) на базе n-МОП транзисторов; б) на базе КМОП транзисторов

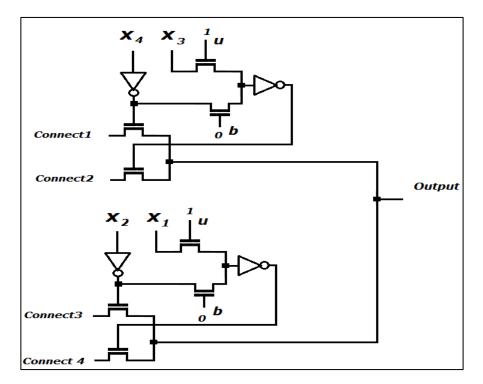

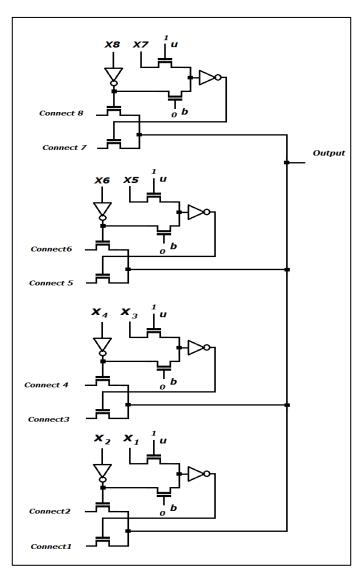

Требуется синтезировать комбинированный элемент LUT с использованием комбинированного кодирования n переменных,  $n=n_2+n_1$ , где  $n_1$  – реализуется обычным (позиционным) LUT, а  $n_2$  – унитарным LUT. При этом  $n_1$  и  $n_2$  могут быть в двух вариантах, выражение (2.24):

1)

$$(n_1, n_2)$$

, 2)  $(n_2, n_1)$ . (2.24).

Для этого предлагается выполнить следующие этапы.

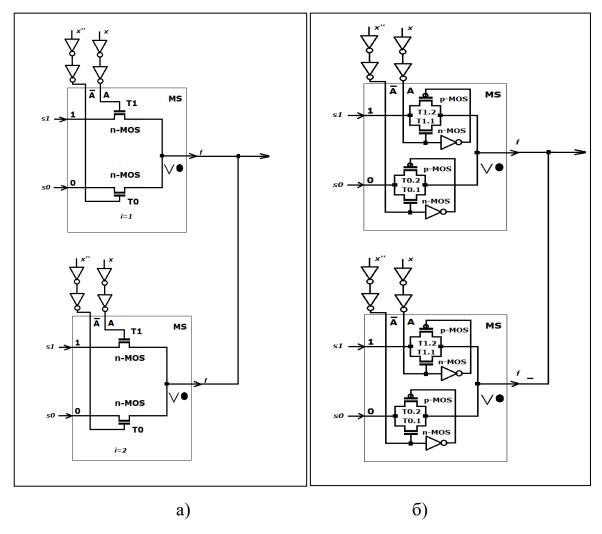

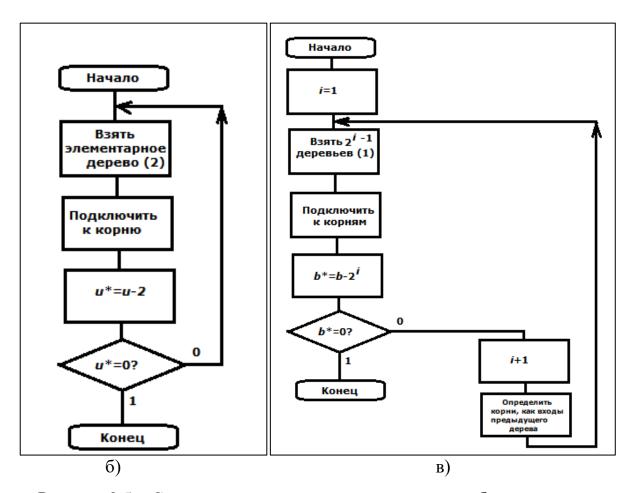

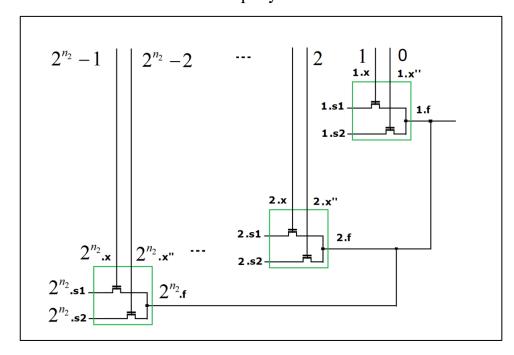

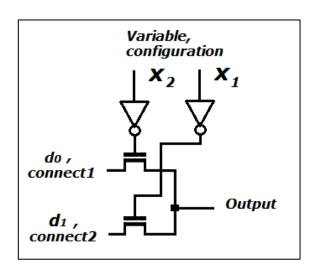

#### 2.4.1 Синтез унитарных блоков

Синтез одного унитарного блока: 1.1. i=1. Соединить i.f c i+l.f — выражение (2.25), рисунок 2.3:

$$\begin{vmatrix}

i.s_0 - i.x'' \\

\vdots \\

i.s_1 - i.x \\

i+1.s_0 - i+1.x''

\end{vmatrix} (\lor \bullet) i.f$$

$$\begin{vmatrix}

i(\lor \bullet)i \\

\vdots \\

i+1.s_1 - i+1.x

\end{vmatrix} (\lor \bullet).$$

(2.25)

Повторить п.  $2^{n_2-1}$  , где 1- раз,  $n_2-$  размерность унитарного блока. В результате получается выражение (2.26):

$$\begin{bmatrix}

i.s_{0}-i.x" \\

j.s_{1}-i.x \\

i+1.s_{0}-i+1.x"

\end{bmatrix}$$

$$\begin{bmatrix}

(\vee \bullet)i.f \\

i+1.s_{1}-i+1.x

\end{bmatrix}$$

$$\vdots$$

$$i+2^{n_{2}}.s_{0}-i+2^{n_{2}}.x" \\

j(\vee \bullet)i.f$$

$$i+2^{n_{2}}.s_{1}-i+2^{n_{2}}.x$$

$$(2.26)$$

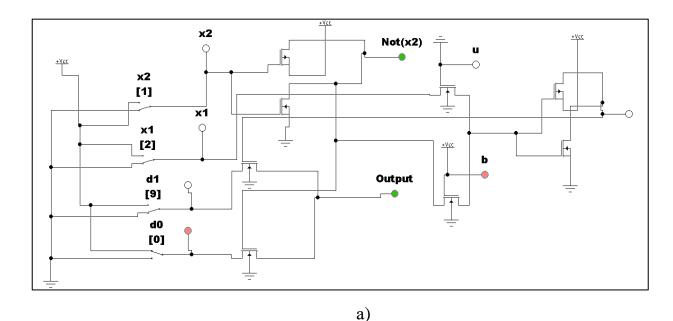

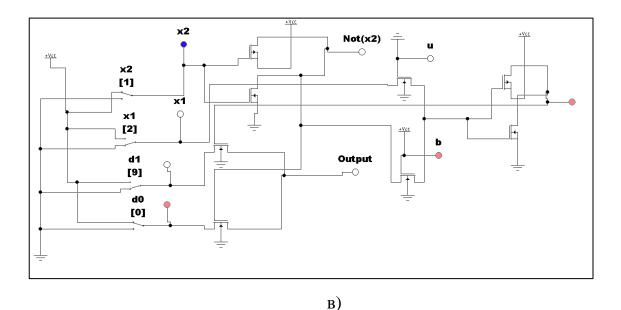

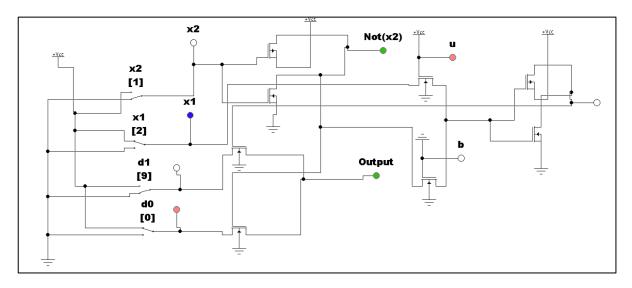

Рисунок 2.3 — Коммутатор (унитарный 2-LUT) 4-1: а) на базе n-МОП транзисторов; б) на базе КМОП транзисторов

Далее, если производится вычисление логической функции f(dx), выполняется пункт 1.3. Подключаются i.s к соответствующим выходам конфигурационной памяти d. 1.4. Подключить i.x, i.x

$$\begin{bmatrix}

d_{0}(i.s_{0})-i.x" \\

d_{1}(i.s_{1})-i.x \\

d_{2}(i+1.s_{0})-i+1.x" \\

\end{bmatrix} (\lor \bullet)i.f(dx)$$

$$d_{3}(i+1.s_{1})-i+1.x$$

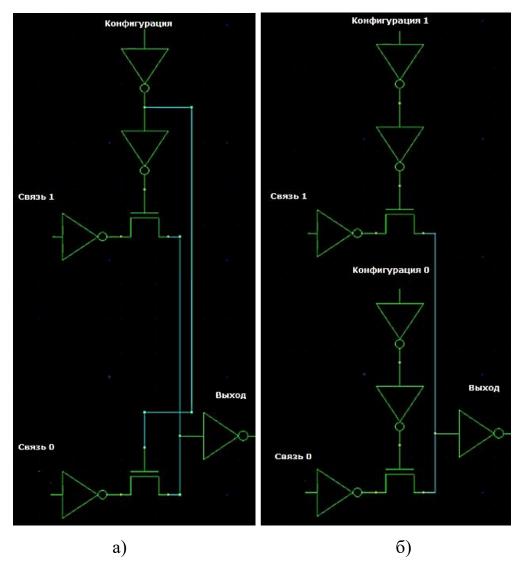

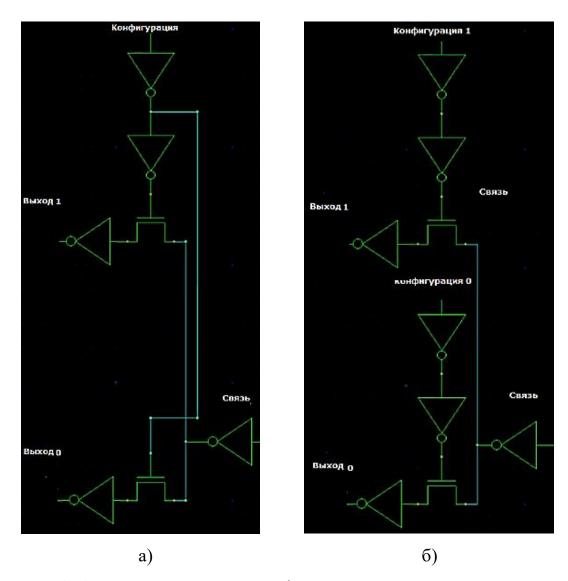

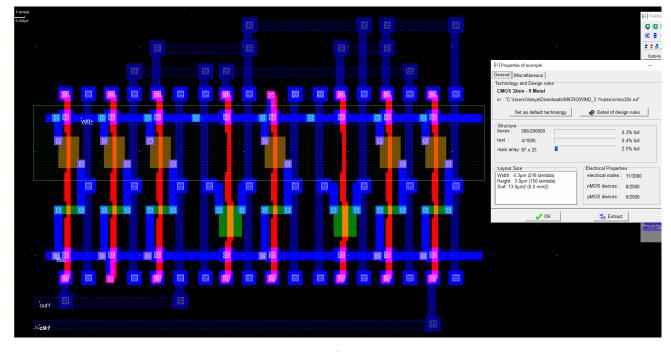

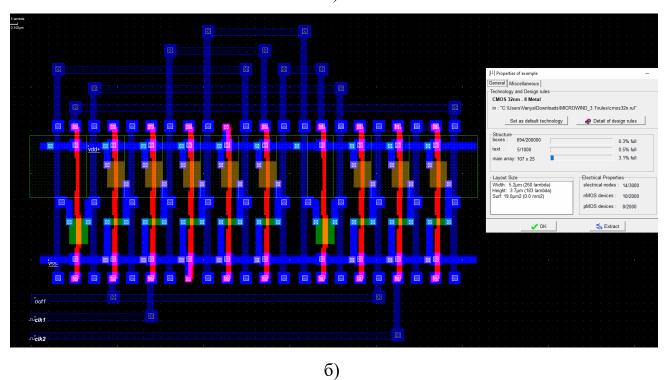

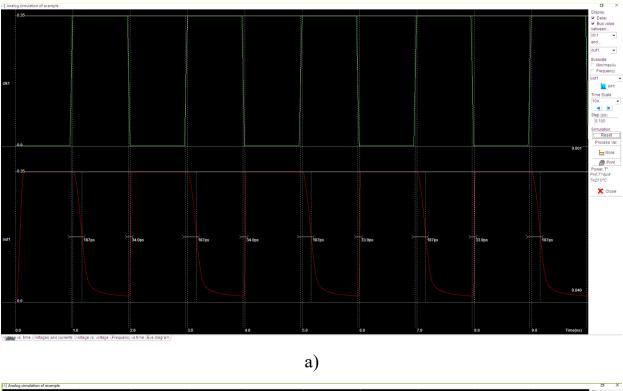

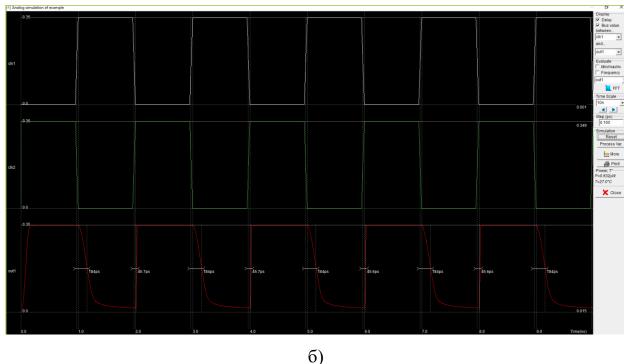

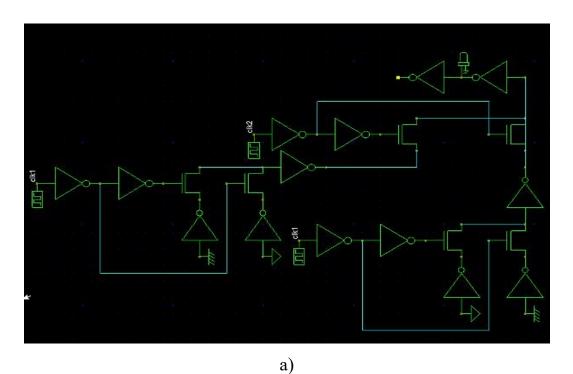

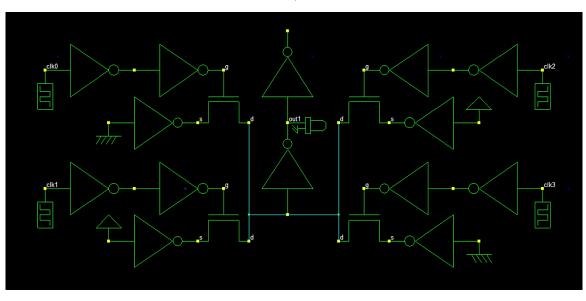

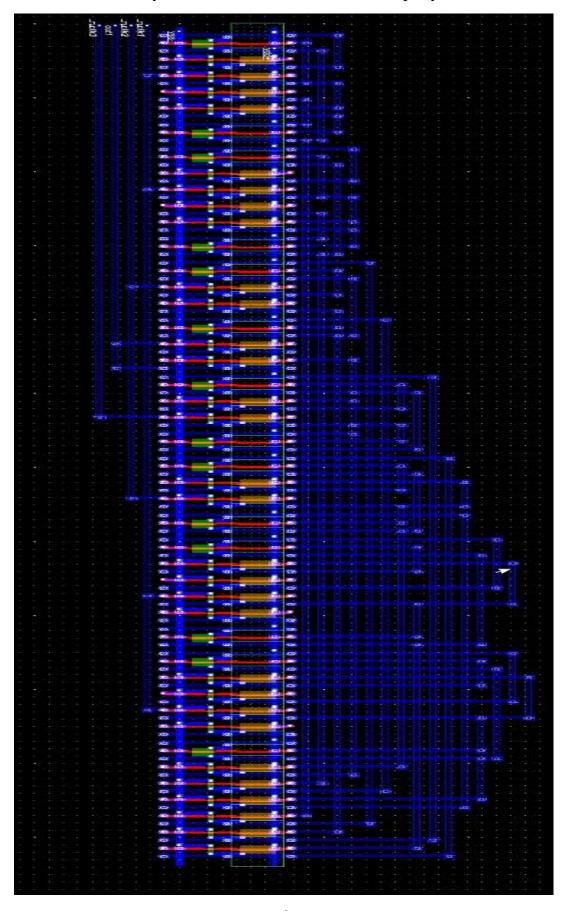

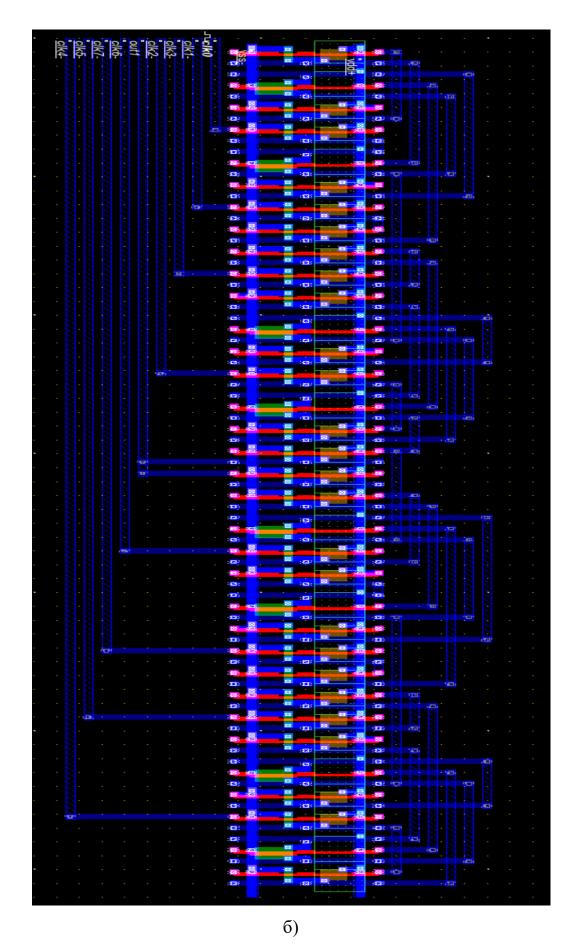

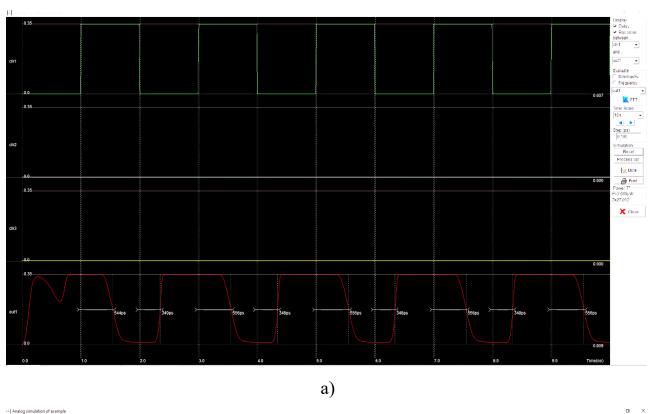

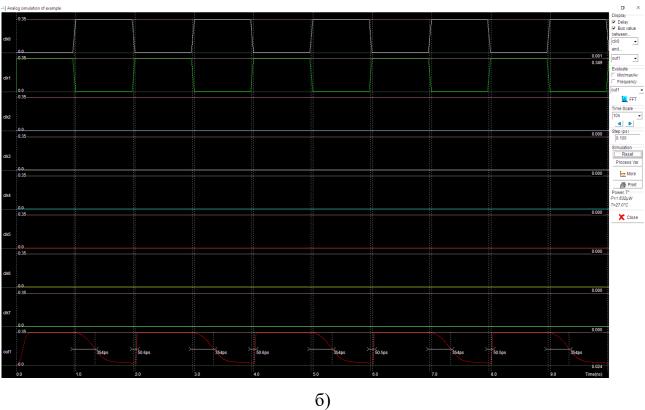

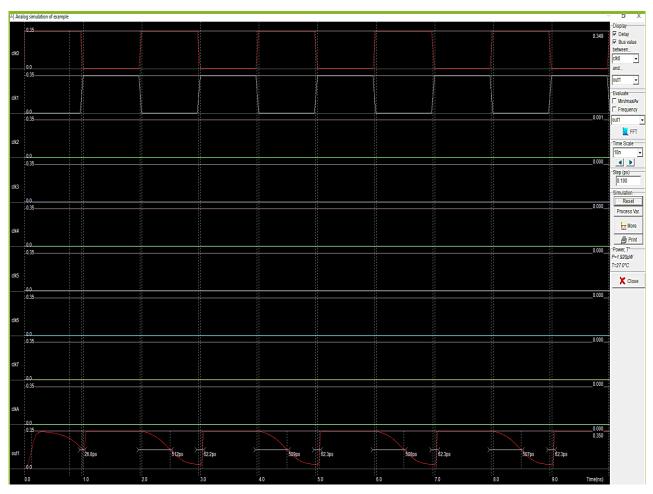

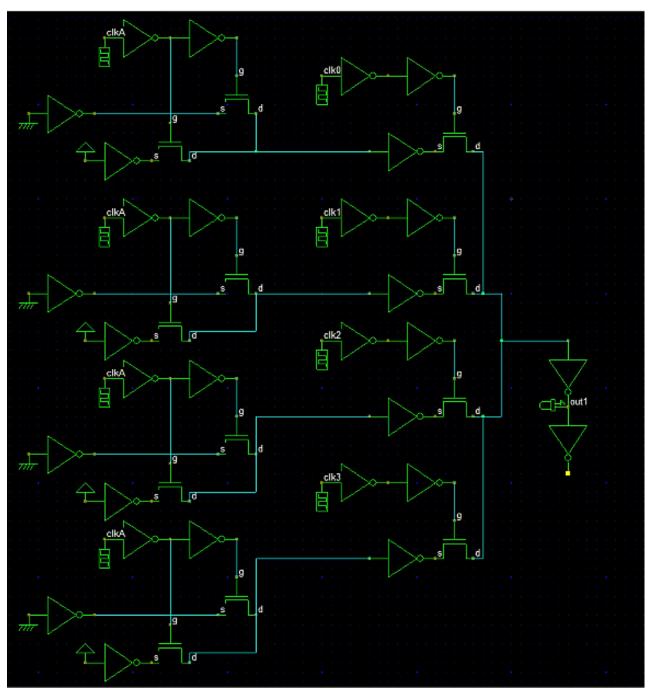

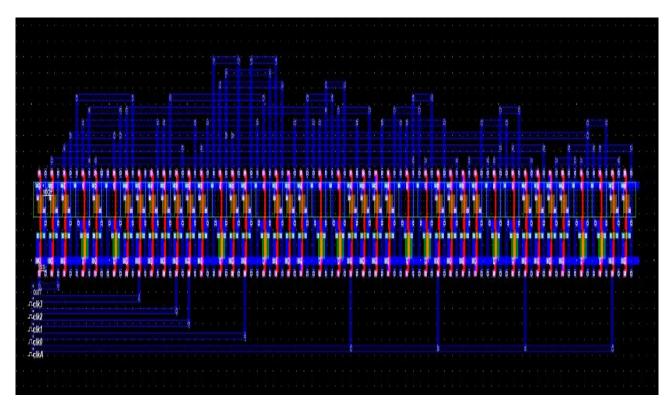

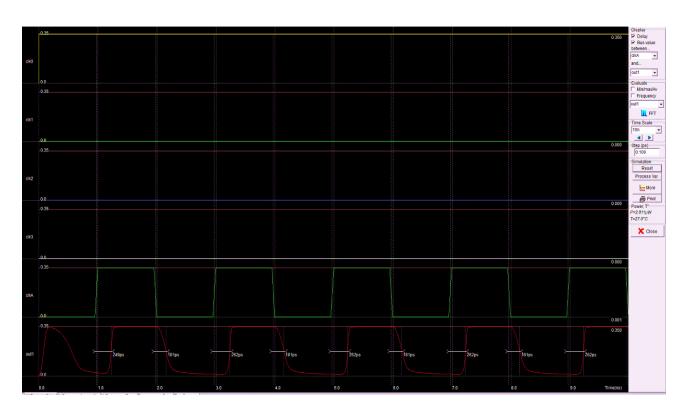

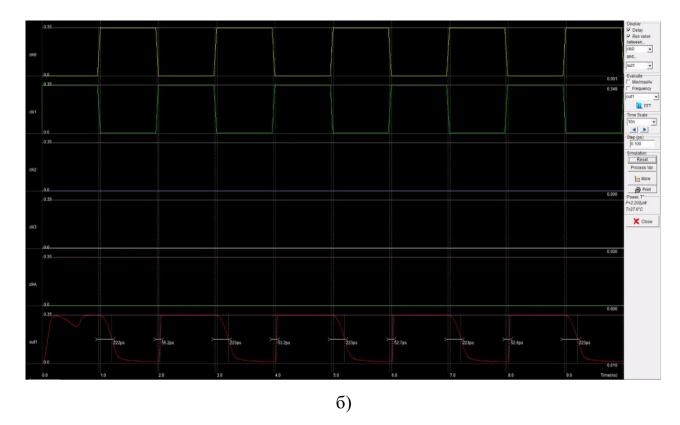

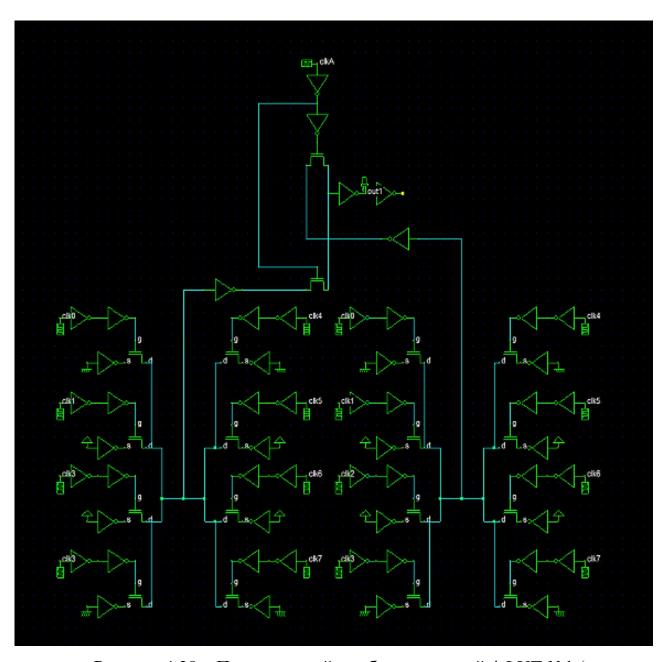

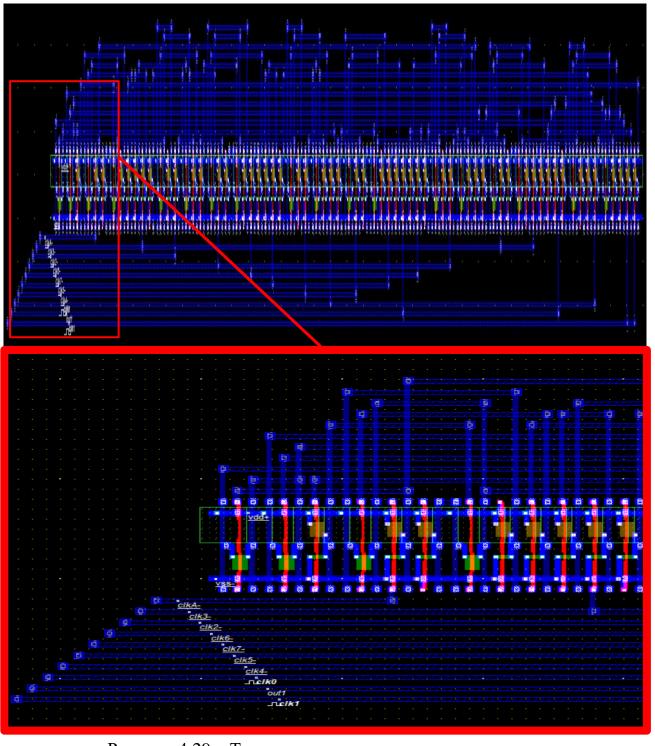

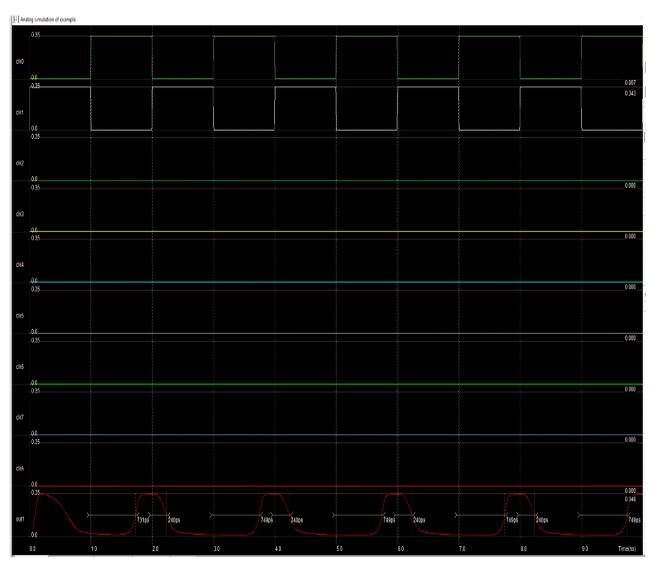

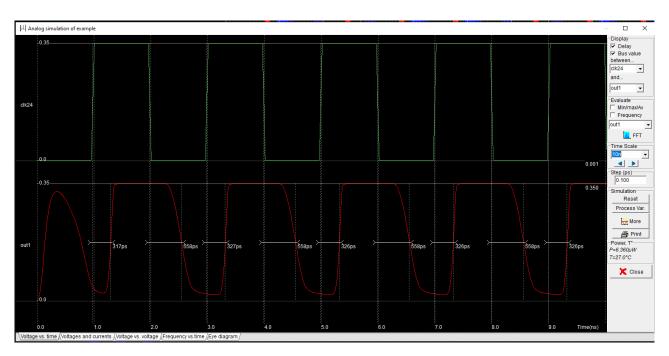

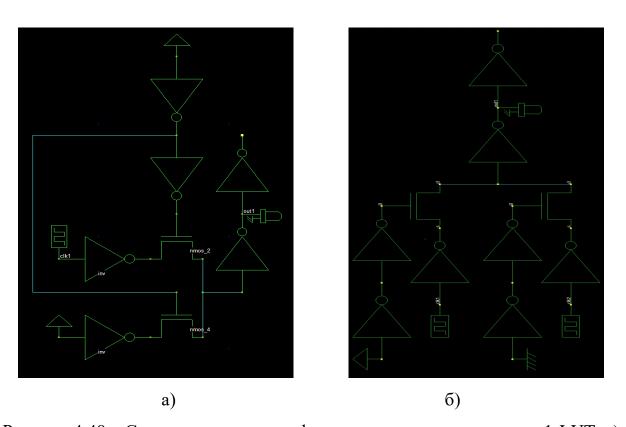

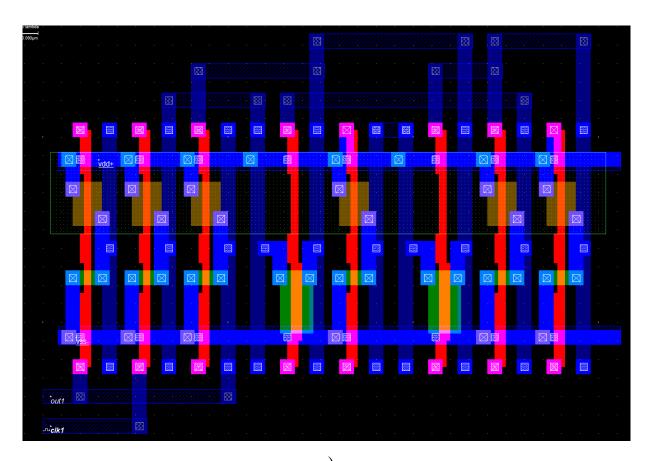

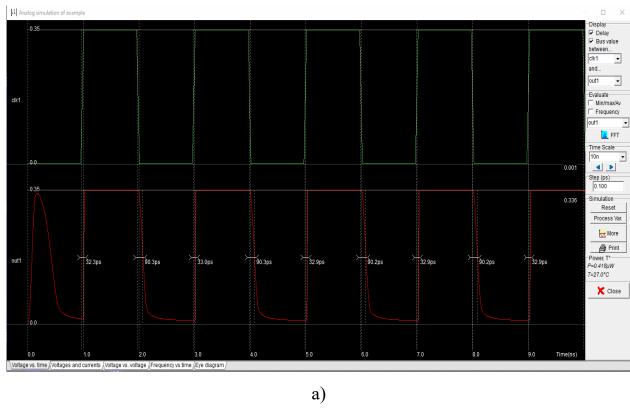

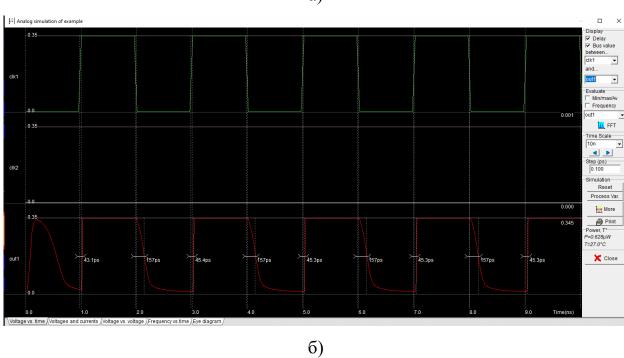

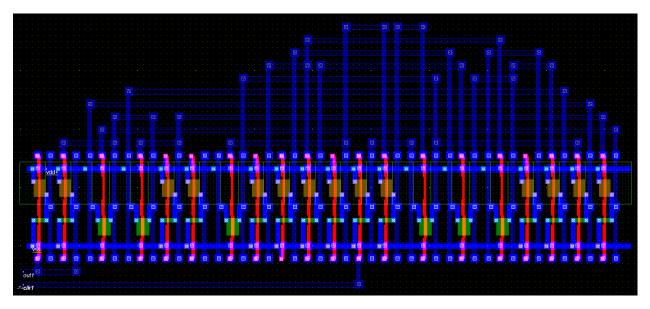

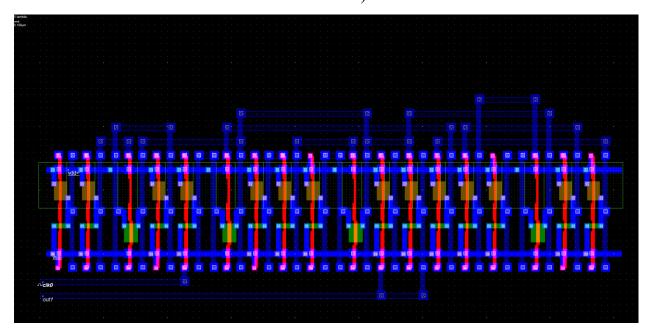

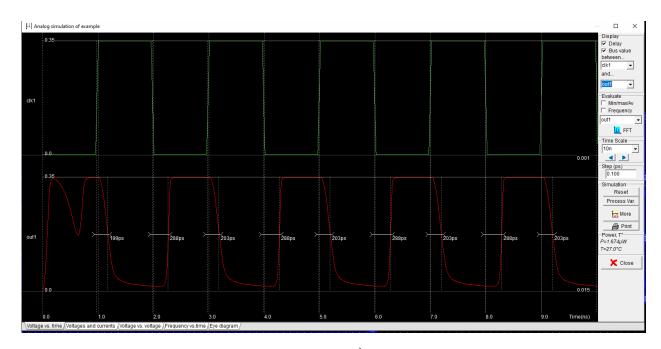

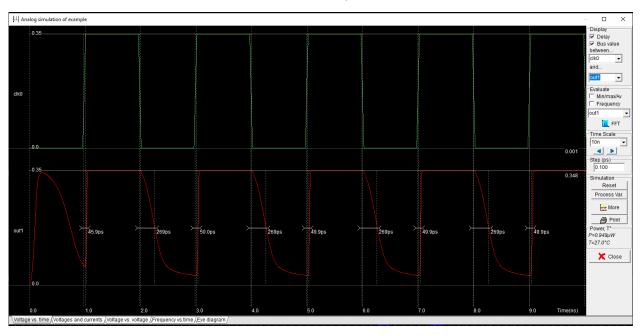

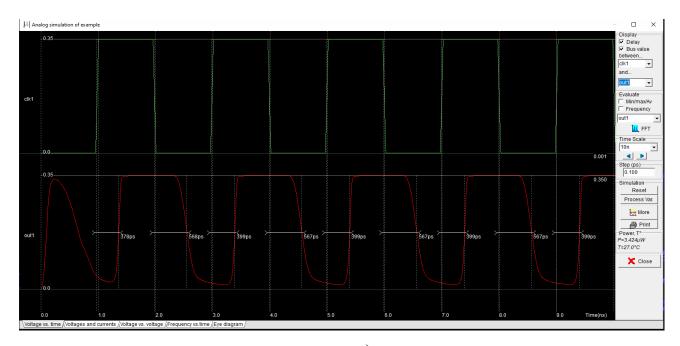

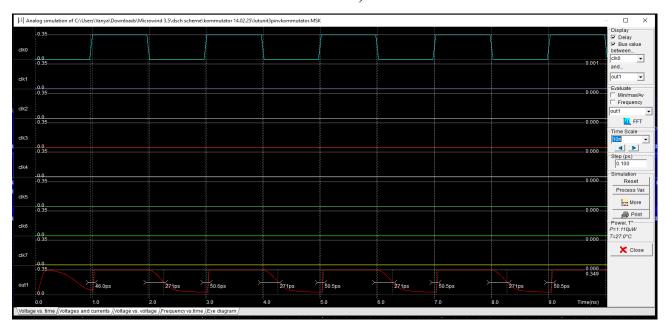

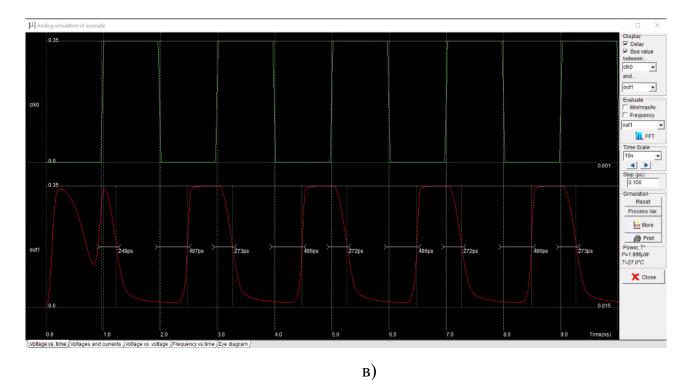

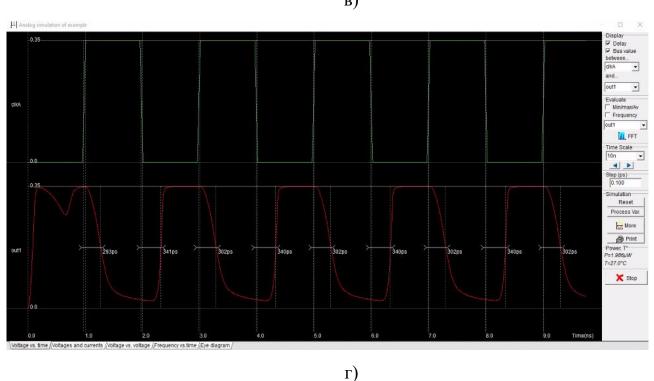

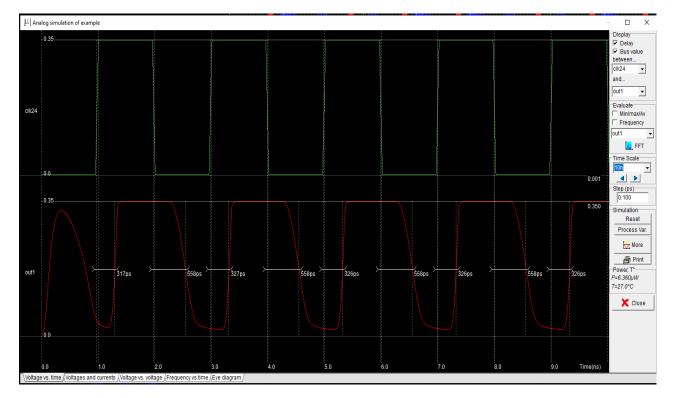

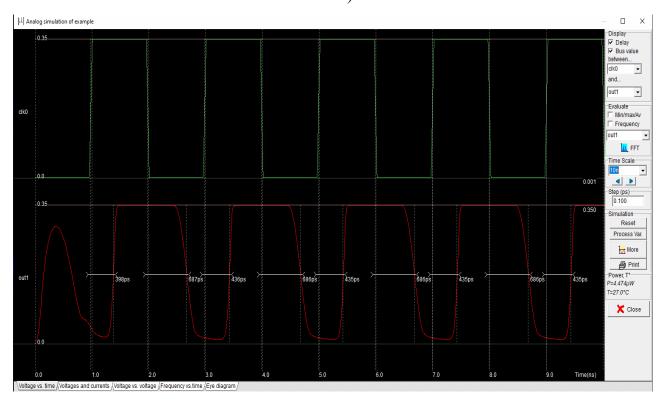

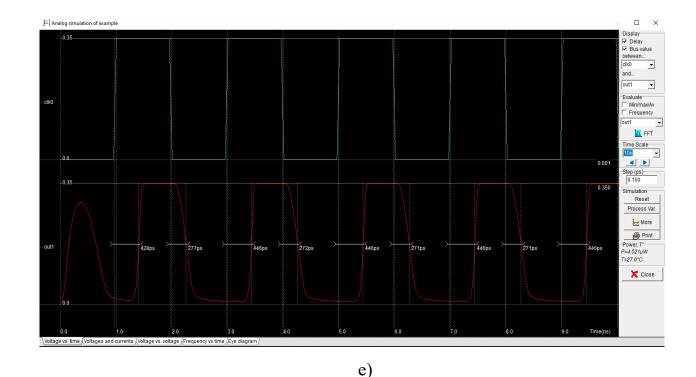

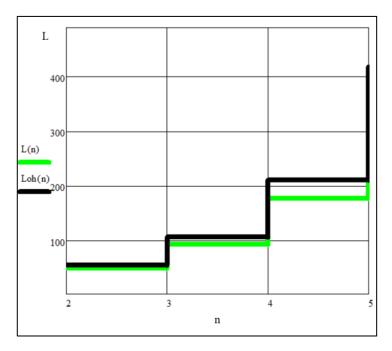

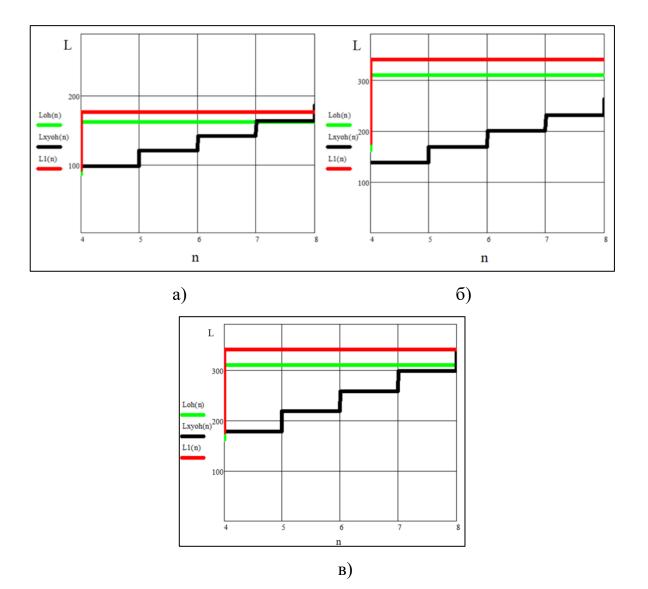

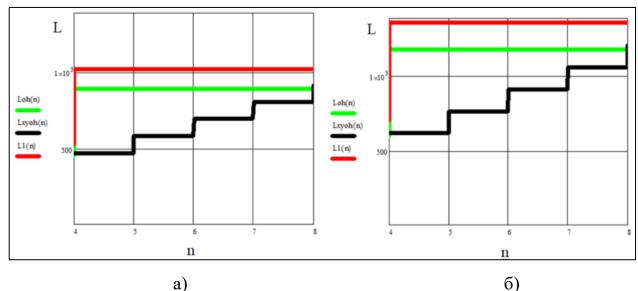

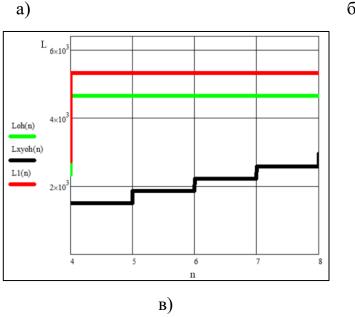

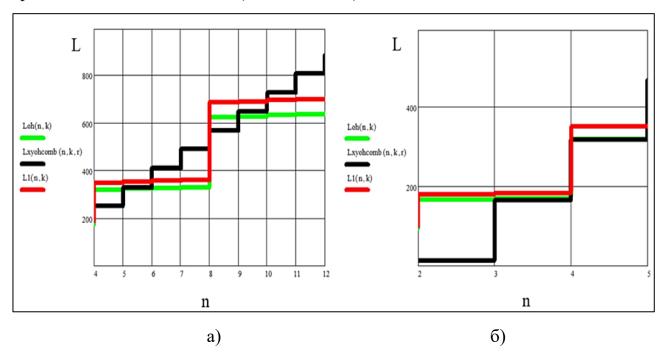

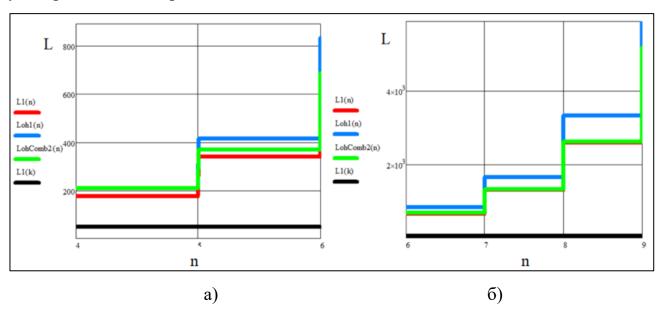

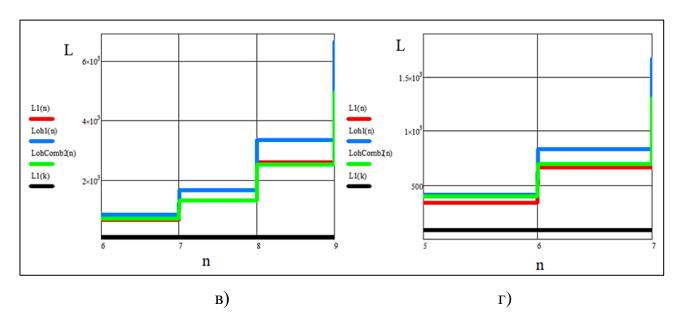

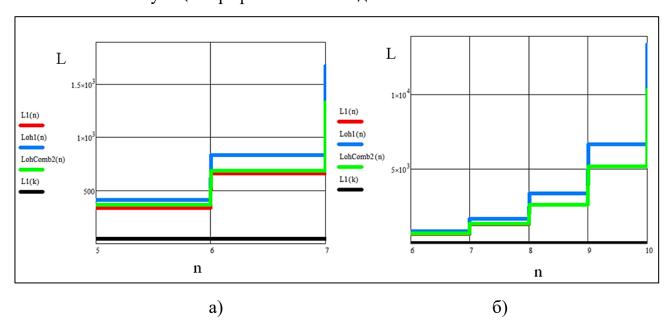

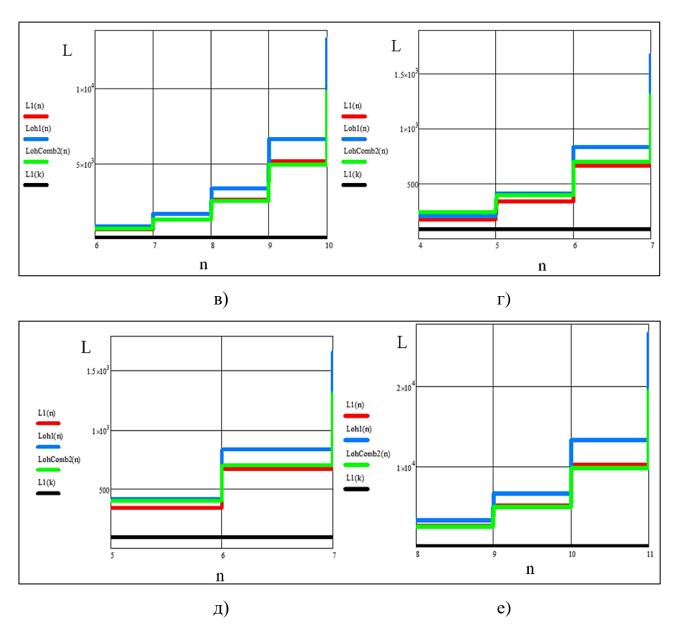

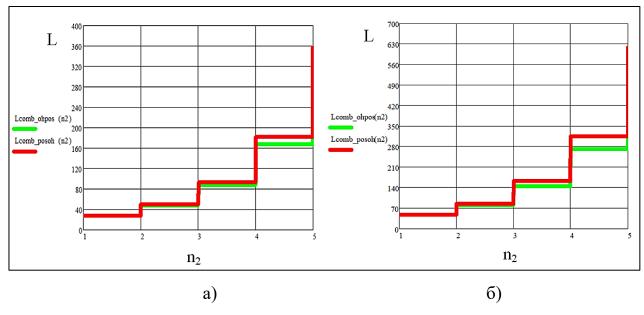

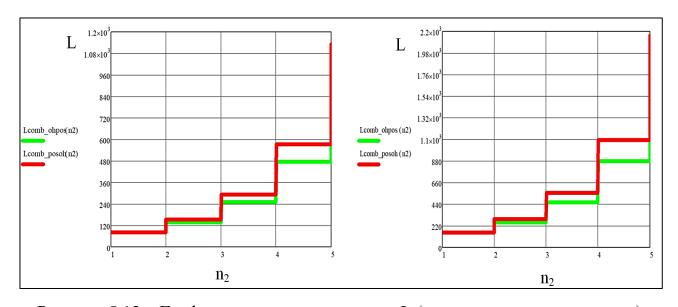

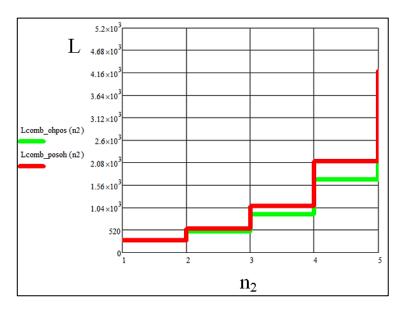

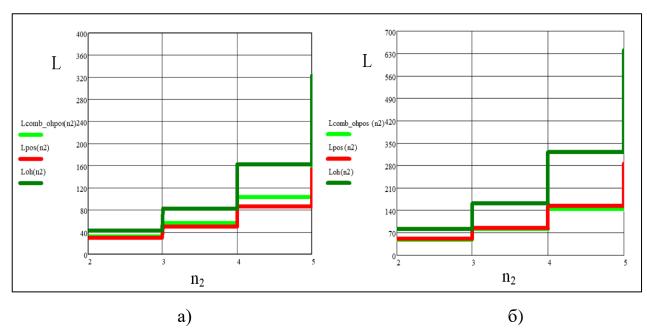

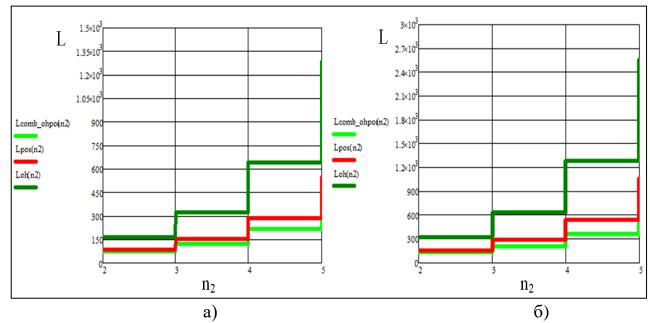

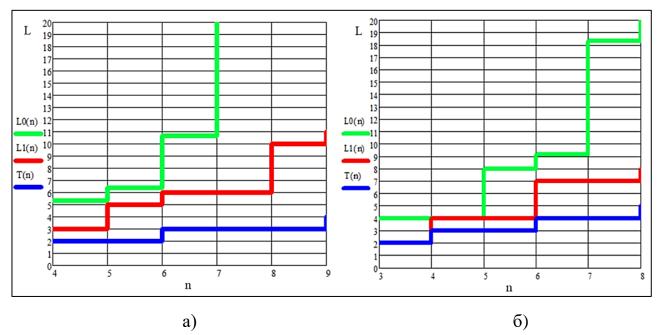

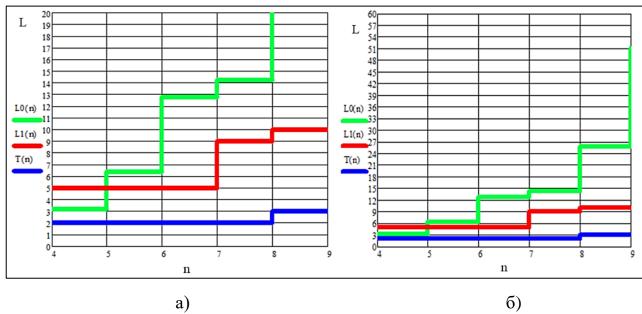

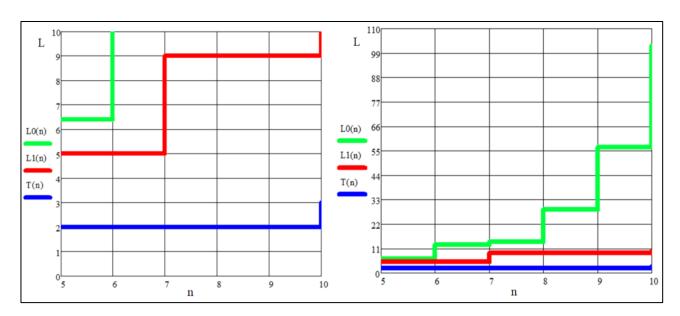

$$\vdots$$