## ВИХОРЕВ РУСЛАН ВЛАДИМИРОВИЧ

## ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ ПЛИС FPGA ДЛЯ РЕАЛИЗАЦИИ СИСТЕМ ФУНКЦИЙ

05.13.05 – Элементы и устройства вычислительной техники и систем управления

АВТОРЕФЕРАТ диссертации на соискание ученой степени кандидата технических наук

Работа выполнена в Федеральном государственном бюджетном образовательном учреждении высшего образования «Пермский национальный исследовательский политехнический университет»

Научный руководитель: ТЮРИН Сергей Феофентович,

доктор технических наук, профессор

Официальные оппоненты: АНИКИН Игорь Вячеславович,

доктор технических наук, профессор, заведующий

кафедрой «Системы информационной безопасности» ФГБОУ ВО «Казанский

национальный исследовательский технический

университет им. А.Н. Туполева-КАИ»

ЛЕСНИКОВ Владислав Алексеевич,

кандидат технических наук, доцент, доцент

кафедры «Радиоэлектронные средства» ФГБОУ ВО

«Вятский государственный университет»

Ведущая организация: Федеральное государственное автономное

образовательное учреждение высшего образования «Национальный исследовательский университет «Московский институт электронной техники»

Защита состоится «27» декабря 2019 г. в 14.00 часов на заседании диссертационного совета Пермского национального исследовательского политехнического университета Д ПНИПУ.05.04, по адресу: 614990, г. Пермь, Комсомольский проспект, д. 29, ауд. 345.

С диссертацией можно ознакомиться в библиотеке и на сайте Федерального государственного бюджетного образовательного учреждения высшего образования «Пермский национальный исследовательский политехнический университет» (http://pstu.ru).

Автореферат разослан «28» октября 2019 г.

Ученый секретарь диссертационного совета Д ПНИПУ.05.04, доктор технических наук, доцент

### ОБЩАЯ ХАРАКТЕРИСТИКА РАБОТЫ

Актуальность темы исследования. В настоящее время для реализации цифровых элементов и устройств вычислительной техники и систем управления широко используются программируемые логические интегральные схемы (ПЛИС). Основой ПЛИС типа Field-Programmable Gate Array (FPGA) является логический элемент (ЛЭ) – генератор функций Look Up Table (LUT), число входных переменных которого увеличилось за 30 лет с 4-х до 8, а количество ЛЭ в ПЛИС – до десятка миллионов. Разработаны адаптивные логические модули (АЛМ), в которых разрядность ЛЭ может гибко изменяться под конкретный проект. Даже при наличии таких возможностей ПЛИС в ряде областей применения, количества ЛЭ может оказаться недостаточно, например, в системах управления летательных аппаратов в связи с возрастанием возложенных на них задач и наличия очень жестких масса-габаритных ограничений. Таким образом задача улучшения характеристик ЛЭ ПЛИС является актуальной. технических Олним сдерживающих факторов является то, что существующие ЛЭ ПЛИС типа FPGA не ориентированы на реализацию систем функций, зависящих от переменных одного ЛЭ. Для данного конфигурационного файла логический элемент FPGA реализует только одну логическую функцию в совершенной дизъюнктивной нормальной форме  $(СДН\Phi)$ . Реализация систем из m логических функций выполняется на m ЛЭ, то есть каждая логическая функция реализуется на отдельном LUT, что приводит к значительной избыточности при вычислении систем логических функций, зависящих от одних и тех же переменных, особенно, когда количество переменных достаточно велико. В то же время реализация систем функций в дизъюнктивной нормальной форме (ДНФ) используется в ПЛИС типа Complex Programmable Logic Device (CPLD). Оба подхода имеют свои плюсы и минусы, однако особенности комплексирования подходов FPGA и CPLD до конца не выявлены.

Таким образом, актуальным является проведение исследований в области создания методов и средств реализации систем логических функций в ЛЭ ПЛИС FPGA, особенно в связи с известными проблемами импортозамещения в отечественной электронной компонентной базе.

Степень разработанности темы исследования. Особенности логики ПЛИС Ерванта, Мехта, рассмотрены работах 3. Н. A.B. С.А. Цыбина, А.Н. Денисова, В.И. Хаханова, В.С. Харченко, А.В. Дрозда, Г.П. Аксеновой, Д.Е. Иванова, Ю.А. Скобцова, М. Abusultan, S. P Khatri, M Turi, J. Delgado-Frias, N. Jha. Новые логические элементы ПЛИС разрабатывались и С.Ф. работах A.B. Грекова, исследовались В Тюрина, O.A. А.Ю. Городилова, А.Н. Каменских. Однако эти работы не затрагивают реализацию систем логических функций в LUT FPGA. Созданием гибридной FPGA (Hybrid FPGA), которая по сути является совокупностью ЛЭ LUT и встроенных программируемых логических матриц (PLA, PAL), занимались исследователи Alireza Kaviani, Stephen Brown, Chi Wai Yu.

Однако в полной мере вопросы реализации систем логических функций при комплексировании подходов FPGA и CPLD до сих пор не решены.

Объектом исследования являются логические элементы ПЛИС.

**Предметом исследования** являются методы реализации систем логических функций в ПЛИС.

**Целью** диссертационного исследования является решение научной задачи выбора оптимального набора логических элементов для адаптивно-гибридной реализации систем логических функций в ПЛИС FPGA.

#### Основные задачи исследования:

- 1. Усовершенствовать метод реализации логических функций в СДНФ на основе соответствующего адаптивного логического элемента.

- 2. Усовершенствовать метод реализации логических функций в ДНФ.

- 3. Произвести оценку сложности реализации систем логических функций на основе разработанных логических элементов.

- 4. Разработать и исследовать модели предложенных логических элементов FPGA для реализации систем логических функций в типовых проектах на ПЛИС.

- 5. Разработать алгоритм оптимизации набора логических элементов ПЛИС FPGA для реализации систем логических функций в типовых проектах на ПЛИС.

## Научная новизна диссертационной работы заключается в следующем:

- Предложен усовершенствованный метод реализации логических функций в СДНФ на основе соответствующего адаптивного логического элемента, отличающийся тем, что в зависимости от настройки возможна реализация либо стандартного логического элемента LUT, либо дешифратора для реализации систем логических функций.

- Предложен усовершенствованный метод реализации систем логических функций в ДНФ, отличающийся тем, что использовано оригинальное кодирование конъюнкций ДНФ, обеспечивающее формирование значения конъюнкции без использования подтягивающего резистора.

- Получены оценки сложности реализации систем логических функций на основе разработанных логических элементов, отличающиеся декомпозицией, учитывающей ограничения Мида-Конвей на число последовательно соединенных передающих транзисторов.

- Выполнена оптимизация набора логических элементов ПЛИС FPGA на основе комбинирования ЛЭ, вычисляющих функции в СДНФ, и ЛЭ, вычисляющих функции в ДНФ, отличающаяся тем, что для этих целей модифицирован венгерский метод.

**Теоретическая значимость** диссертационной работы состоит в том, что развиты методы синтеза логических элементов, реализующих системы функций в ПЛИС. Разработаны и получены патентоспособные технические решения для реализации систем логических функций в ПЛИС типа FPGA, полученные оценки сложности показывают предпочтительность их по аппаратным затратам по сравнению с существующими АЛМ.

**Практическая значимость** диссертационной работы состоит в том, что предложенные усовершенствованные методы позволили снизить аппаратные затраты на реализацию систем логических функций (акт Федерального исследовательского центра "Информатика и управление" Российской академии

наук, акт Публичного акционерного общества «Пермская научно-производственная приборостроительная компания»).

Полученные научные и практические результаты используются в учебном процессе кафедры «Автоматика и телемеханика» Пермского национального исследовательского политехнического университета в рамках практических занятий профильных дисциплин «Электроника», «Проектирование дискретных устройств», «Схемотехника» у студентов направления 27.03.04 «Управление в технических системах» (акт Федерального государственного бюджетного образовательного учреждения высшего образования «Пермский национальный исследовательский политехнический университет»).

Методология исследования. В диссертационной И методы топологического используются методы средства схемотехнического И моделирования, синтеза анализа И схем, структурное программирование. Применяемые методы и средства основаны на положениях дискретной математики, математической логики, теории булевых функций и автоматов, комбинаторики, теории надежности, принципах МОП-схемотехники.

**Область исследования**, обозначенная в сформулированных задачах, соответствует п. 3 «Разработка принципиально новых методов анализа и синтеза элементов и устройств вычислительной техники и систем управления с целью улучшения их технических характеристик» паспорта научной специальности 05.13.05.

## Основные положения, выносимые на защиту:

- 1. Усовершенствованный метод реализации логических функций в СДНФ на основе разработанного адаптивного логического элемента.

- 2. Усовершенствованный метод реализации логических функций в ДНФ.

- 3. Алгоритм оптимизации набора логических элементов ПЛИС FPGA для реализации типовых систем логических функций.

Степень достоверности результатов. Полученные в диссертационной работе результаты не противоречат теоретическим положениям, известным из научных публикаций отечественных и зарубежных исследователей, и подтверждаются результатами, полученными в двух системах моделирования, апробацией и внедрением предложенных в диссертации методов, моделей и алгоритма оптимизации.

Апробация результатов. Основные теоретические и практические результаты диссертационной работы докладывались на научно-технических конференциях: «Микроэлектроника и информатика», Зеленоград, 2015, 2017; ЛЭТИ - IEEE North West Russia Section Young Researchers in Electrical and Electronic Engineering Conference, EIConRusNW, Санкт-Петербург, 2016, 2018; 2-я конференция Российско-белорусская научно-техническая «Элементная база отечественной радиоэлектроники: импортозамещение и применение», Нижний Новгород, 2015; 14-я международная конференция «Авиация и космонавтика», Москва, 2015; на международном форуме «Микроэлектроника-2017» в рамках 3-й международной научной конференции «Электронная компонентная база и электронные модули», Республика Крым, г. Алушта, 2017; 14-я всероссийская школа-конференция молодых ученых «Управление большими

УБС-2017», г. Пермь, 2017; на международной выставке SEMIEXPO RUSSIA 2017; на всероссийской научно-технической конференции «Автоматизированные системы управления и информационные технологии» г. Пермь, 2019; на семинарах в ИПИ РАН, ИПУ РАН, МИЭТ, ПНИПУ, других региональных и всероссийских конкурсе научно-технических международном конференциях; на «Инновационная радиоэлектроника», 2017 г.

Публикации. Основные результаты диссертационной работы опубликованы в 21 печатной работе, из них 5 публикаций в ведущих рецензируемых научных изданиях, 2 публикации в изданиях, индексированных в международных базах цитирования Scopus и Web of Science, 3 патента на изобретение, 1 свидетельство о государственной регистрации программ для ЭВМ.

Структура и объем работы. Диссертационная работа состоит из введения, четырех глав, заключения, списка использованных источников и приложений. Содержит 180 страниц машинописного текста, из которых основной текст составляет 151 страницы, 170 рисунков и 6 таблиц, список литературы из 82 наименований, 3 приложений.

#### ОСНОВНОЕ СОДЕРЖАНИЕ РАБОТЫ

Во введении обосновывается актуальность выбранной темы исследования, формулируются цели и задачи диссертационной работы, раскрывается научная новизна и практическая значимость полученных результатов, сформулированы научные положения, выносимые на защиту.

В первой главе сделан обзор существующих методов реализации логических функций в больших интегральных схемах программируемой логики. Проводится анализ адаптивных многоразрядных ЛЭ FPGA. Исследуются методы и средства реализации систем логических функций в ПЛИС. Ставятся задачи исследования. Постановка задачи формулируется следующим образом:

Дано: архитектуры существующих ЛЭ и адаптивного логического модуля – АЛМ на

их основе, множество элементов АЛМ:  $\overset{e}{\underset{i=1}{\cup}}\Psi_i$  , их количество:  $\overset{e}{\underset{i=1}{\sum}}\!|\Psi_i|$  , значения элементов **FPGA** сложности существующих логических **CPLD** мощности)

$$E - \sum_{i=1}^{e} \sum_{\mu=1}^{|\Psi_{\mu}|} \mathrm{E}(n,m,v,k,r)_{i\mu}$$

и максимальной задержки тах  $au_{\Psi_i}$  относительно максимального

количества n переменных, m функций, v конъюнкций в реализуемых логических функциях, а также k декомпозиции дерева транзисторов, r ограничения Мида-Конвей на число последовательно включенных передающих транзисторов (Pass Transistors).

Требуется:

Усовершенствовать методы реализации существующих АЛМ путем комплексирования подходов к реализации логики в FPGA и CPLD, и создания гибридного АЛМ - АЛМ\*. Выбрать оптимальный набор логических элементов для реализации систем логических функций в АЛМ\*, для чего:

- 2. Получить для АЛМ\*:  $\bigcup_{j=1}^{q} \Psi_{i}^{*}$  множество новых элементов на основе усовершенствованных методов реализации систем логических функций.

- 3. Для сравнения их между собой и с существующими элементами с целью выбора наиболее предпочтительных вариантов  $\bigcup_{j=1}^q \Psi_i^*$  \* получить оценки сложности по числу транзисторов, выполнить моделирование в среде Multisim и Microwind с оценкой площади топологии S, энергопотребления E и максимальной задержки  $\max \tau_{\Psi_i}$ .

- 4. Относительно полученных вариантов  $\bigcup_{j=1}^{q} \Psi_{i}^{*} *$  осуществить оптимизацию (минимизацию) по количеству транзисторов и площади S на основе получения их оценок сложности  $L_{s}^{*}(n,m,v,k,r)_{jy}$  и модифицирования венгерского метода (алгоритма) с целью получения оптимального набора (вектора) элементов  $z_{1}z_{2}....z_{\pi}$ :

$$\{z_1 z_2 \dots z_{\pi}\}(n, m, v, k, r); z_{\lambda} = \sum_{\sigma=1}^{v} \psi_{\sigma}; \psi_{\sigma} \in \Psi_i^*; v \le j; \sum_{\kappa=1}^{\pi} z = \sum_{i=1}^{e} |\Psi_i|$$

(1)

для заданного набора параметров n, m, v, k, r:

$$L_{s(z_1 z_2 \dots z_n)}(n, m, v, k, r) \rightarrow \min.$$

(2)

5. С использованием полученных наборов  $\{z_1z_2....z_\pi\}(n,m,v,k,r)$  определить множество Парето, учитывающее полученные в результате моделирования оценки площади топологии, энергопотребления и задержки и их аппроксимацию для реальных значений параметров систем логических функций.

В результате получить требуемое количество новых элементов в одном АЛМ\*:  $\sum_{j=1}^{q} |\Psi_{j}^{*}|$  \* так, чтобы с меньшими затратами в количестве транзисторов и

площади топологии реализовать заданные системы логических функций

$$\sum_{j=1}^{q} \sum_{\gamma=1}^{|\Psi_{\gamma}^{*}|} L_{s}^{*}(n,m,v,k,r)_{j\gamma} << \sum_{i=1}^{e} \sum_{\xi=1}^{|\Psi_{\xi}|} L_{s}(n,m,v,k,r)_{i\xi};$$

(3)

при этом не ухудшая энергопотребление и задержку:

$$\sum_{j=1}^{q} \sum_{\gamma=1}^{|\Psi_{\gamma}^{*}|} E(n, m, v, k, r)_{j\gamma} \leq \sum_{i=1}^{e} \sum_{\xi=1}^{|\Psi_{\xi}|} E(n, m, v, k, r)_{i\xi};$$

$$\forall \tau_{\Psi_{j}^{*}} \forall \tau_{\Psi_{i}} (\max \tau_{\Psi_{j}^{*}} \leq \max \tau_{\Psi_{i}}).$$

$$(4)$$

**Вторая глава** посвящена усовершенствованию методов реализации систем логических функций в ПЛИС. Для реализации системы из m логических функций, представленных в СДНФ, в существующих ПЛИС FPGA используются m деревьев передающих транзисторов, которые могут быть выражены следующим образом:

$$z_{out} = \bigvee_{i=1}^{2^n} \left( \bigotimes_{j=1}^n x_j^{\sigma(i-1,j)} \cdot d_i \right), \tag{5}$$

где  $\sigma(i,j)$  - показатель инвертирования переменной в соответствующей ветви дерева передающих транзисторов, его значение противоположно значению j-го разряда в двоичной записи числа i,  $d_i \in \{0,1\}$  — настройка, значение i-й конфигурационной

ячейки SRAM. Выражение (5) реализует n-уровневое дерево передающих транзисторов. Представим его следующим образом:

$$x_{n} \leftarrow \frac{\bar{x}_{n-1} \leftarrow \bar{x}_{n-2} \leftarrow \bar{x}_{1} \cdot d_{0}}{x_{n-2} \leftarrow x_{n-2} \leftarrow x_{1} \cdot d_{1}} \\

x_{n-1} \leftarrow \frac{\bar{x}_{n-2} \leftarrow \bar{x}_{n-2} \leftarrow \bar{x}_{1} \cdot d_{1}}{x_{n-2} \leftarrow x_{n-2} \leftarrow x_{n-2$$

где ∨•-корень дерева, монтажное ИЛИ (wired OR).

Предлагается реализация систем логических функций в СДНФ на основе обратного дерева – DC-LUT "дешифратор-LUT":

$$d_{out.i} = \mathop{\&}_{j=1}^{n} (x_j^{\sigma(i-1,j)}); i = 1,2^n,$$

(7)

где  $d_{out.i}$  - выход i-ой ветви дерева «наоборот», соответствующий истинности i-ой конъюнкции из  $2^n$  конъюнкций n переменных.

$$x_n \xrightarrow{\overline{x}_{n-1} \to \overline{x}_{n-2} \to \cdots} \overline{x}_2 \xrightarrow{\overline{x}_1 \to d_{out} 0} x_1 \xrightarrow{\overline{x}_{n-2} \to d_{out} 1} x_{n-1} \xrightarrow{\overline{x}_{n-2} \to d_{out} 1} x_{n-1} \xrightarrow{\overline{x}_{n-2} \to d_{out} 1} x_n \xrightarrow{\overline{x}_{n-2} \to d_{out} 1} x_n \xrightarrow{\overline{x}_{n-2} \to d_{out} 2^n - 2} x_{n-1} \xrightarrow{\overline{x}_{n-2} \to d_{out} 2^n - 2} x_{n-2} \xrightarrow{\overline{x}_{n-2} \to d_{out} 2^n - 2} x_{n-2} \xrightarrow{\overline{x}_{n-2} \to d_{out} 2^n - 2} (8)$$

$d_m \in 0,1$  определяет активный уровень при реализации соответствующей цепочки в обратном дереве. Программирование значений m логических функций z осуществляется следующим образом:

$$z_{l} = \bigvee_{i=1}^{2^{n}} (d_{out.i} \cdot h_{l.i}); l = 1, m.$$

(9)

где h — настройка вхождения конституент i в данную функцию из m функций системы. Элементарные DC-LUT-R (использует подтягивающие резисторы R на основе транзисторов в режиме истощения), DC-LUT-O (для n=1) с  $d_{in}$  = 0 и активной

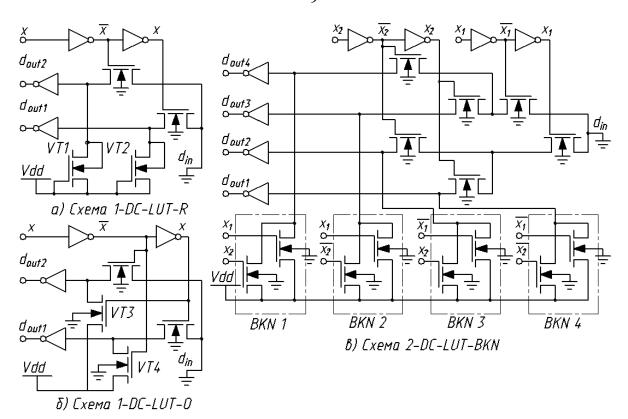

Рисунок 1. Предлагаемые варианты ЛЭ DC-LUT: а) Схема элементарного DC-LUT-R с восстановителями сигнала VT1, VT2, б) Схема элементарного DC-LUT-O с обеспечением ортогональности сигналов на выходах  $d_{out}1$ ,  $d_{out}2$  с помощью дополнительных транзисторов ортогональности VT3, VT4, в) Схема элементарного DC-LUT-BKN с обеспечением ортогональности сигналов на выходах с помощью 4 блоков конституент нуля BKN1-BKN4

логической единицей на двух выходах изображен на рисунке1 (a, б). Элементарный DC-LUT-BKN (для n=2) с  $d_{in}=0$  изображен на рисунке 1 (в).

Предлагаемый адаптивный логический элемент ADC-LUT может в зависимости от настройки реализовать либо LUT, либо DC-LUT. Настройка дерева на реализацию дешифратора осуществляется конфигурационной константой s:

$$\begin{array}{c} -\frac{\bar{x}n-2}{x_{n-1}x_{n-2}} \cdots x_{2} \\ x_{1} \cdot (\bar{s} \cdot d_{2n-1} \vee s \cdot [=z_{0}]) \\ x_{n} \\ x_{n-1} \cdot (\bar{s} \cdot d_{2n-1+1} \vee s \cdot [=z_{1}]) \\ x_{n} \\ x_{n-2} \\ x_{n-1} \cdot (\bar{s} \cdot d_{2n-1+1} \vee s \cdot [=z_{1}]) \\ x_{n-1} \cdot (\bar{s} \cdot d_{2n-1} - 2 \times s \cdot [=z_{2n-2}]) \\ x_{n-1} \cdot (\bar{s} \cdot d_{2n-1-1} \vee s \cdot [=z_{2n-1}]). \end{array}$$

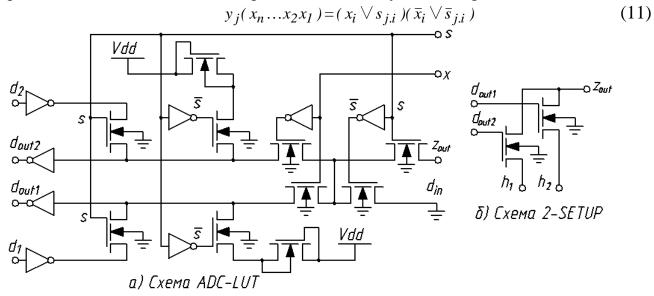

Реализация дизъюнкций (функций) осуществляется подключением выходов - выражения (10) к блокам, реализующим выражения (9). Схема ADC-LUT на одну переменную изображена на рисунке 2.

Для реализации систем функций в ДНФ предлагается модифицировать подход, используемый в CPLD. Программирование по i-ой переменной j-ой конъюнкции ДНФ, зависящей от одной переменной, с учетом ее возможного инверсного значения может быть представлено следующим образом:

Рисунок 2. а) Схема ADC-LUT на одну переменную, s - информация из конфигурационной ячейки (1, реализуется— DC-LUT; 0, реализуется— LUT) б) Схема блока дизъюнкций конституент (блок настройки "Setup") логической функции 2-х выходного DC-LUT(ADC-LUT в режиме DC-LUT).

Для j-ой конъюнкции от n переменных, получим:

$$y_{j} = \underset{i=1}{\overset{n}{\&}} (x_{i} \vee s_{j,i}) (\bar{x}_{i} \vee \bar{s}_{j,i}), j = 1,k$$

(12)

Причем, для настройки s выполняются следующие условия:  $s_{j,i}\bar{s}_{j,i}=0$ ;  $s_{j,i}\sqrt{\bar{s}}_{j,i}=1$  для существенной переменной j-ой конъюнкции,  $s_{j,i}\bar{s}_{j,i}=1$  для не существенной переменной. В качестве альтернативы известным решениям (PAL, PLA) с подтягивающими транзисторами DNF-R - (11), (12) предложено следующее выражение программирования одной i-ой переменной:

$$s_{i} = (d_{SRAM.i} \ d_{in} \vee \overline{d}_{SRAM.i} \ d_{0}) \ x_{i} \vee (d_{SRAM.i} \ d_{in} \vee \overline{d}_{SRAM.i} \ d_{0}) \ \overline{x}_{i}; i=n.$$

(13)

В выражении (13)  $d_{SRAM.i}$ ,  $d_{SRAM.i}$ , - настройка вхождения i-ой переменной из n переменных в j-ую конъюнкцию системы из m функций;  $d_{in}$  - входная константа, которая должна формироваться при «правильном» значении переменной, либо ее несущественности;  $d_0$  - признак того, что заданная переменная имеет «неправильное» значение. Для учета всех переменных данной конъюнкции предложено выражение:

$$\overset{n}{\underset{i=1}{\&}} \{(d_{SRAM.i} \ d_{in} \vee \overline{d}_{SRAM.i} \ d_0) \ x_i \vee (d_{SRAM.i} \ d_{in} \vee \overline{d}_{SRAM.i} \ d_0) \ \overline{x}_i \}. (14)$$

Причем  $d_{in}=1$  для старшей переменной и передает логическую единицу, которая транслируется на выход всей цепочки. Программирование одной переменной изображено на рисунке 3.

Исследуются варианты с последовательным (P) и параллельным (S) соединением блоков одной переменной.

| , ,                 |            | , ,                                          | 1   |                        |

|---------------------|------------|----------------------------------------------|-----|------------------------|

| SRAMd;              | <u>d</u> ; | $\overline{\chi_i} \circ \underline{\chi_i}$ |     |                        |

| d <sub>in</sub> o   | ╆┖         |                                              | -   | ]                      |

| SRAM <del>d</del> ; |            |                                              |     | <i>y<sub>j</sub></i> → |

| 0                   |            | <del>-</del>                                 |     |                        |

| L                   |            |                                              | ┦╬╙ | J                      |

|                     |            | a) _                                         |     |                        |

| SRAM<br>di | SRAM<br>не di | На выходе         | На выходе 0 |

|------------|---------------|-------------------|-------------|

| 1          | 0             | При Х             | При не Х    |

| 0          | 1             | При не Х          | При Х       |

| 1          | 1             | в любом<br>случае | -           |

| 0          | 0             | Запрещен          | Запрещен    |

|            | б)            |                   |             |

Рисунок 3. Блок DNF-S: а) блок одной переменной; б) таблица программирования

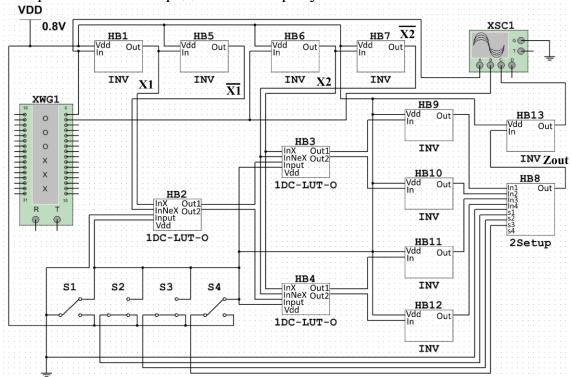

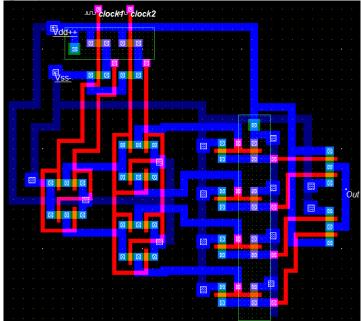

**В третьей главе** выполняется моделирование предложенных технических решений в системе схемотехнического моделирования NI Multisim фирмы National Instruments Electronics Workbench Group и в системе автоматизированного проектирования специализированных (заказных) интегральных схем MicroWind. Получены осциллограммы предлагаемых и существующих ЛЭ, а также построены их топологии. Фрагмент модели логического элемента DC-LUT-O с количеством входных переменных n=2 представлен на рисунке 4.

Рисунок 4. Моделирование одного разряда дешифратора DC-LUT-O для n=2

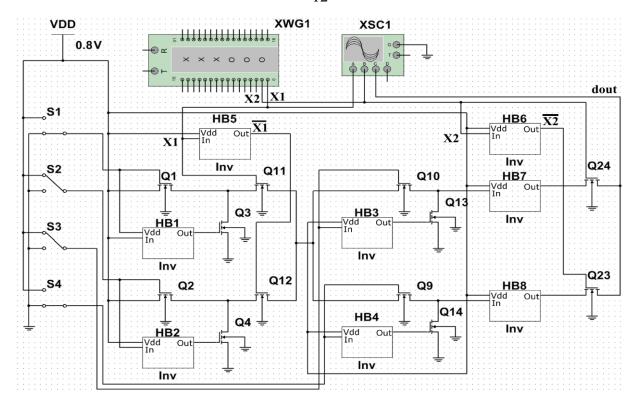

Рисунок 5. Моделирование ЛЭ ПЛИС FPGA на основе DNF-S с последовательным подключением для n=2

Фрагмент модели логического элемента ПЛИС FPGA на основе DNF-S с количеством входных переменных n=2 представлен на рисунке 5.

На рисунках 4,5 Inv — инверторы; S1-S4 — имитация конфигурационной настройки. Q1-Q24 — передающие транзисторы.

Осциллограмма работы DC-LUT-O с количеством входных переменных n=2 при реализации функции исключающее ИЛИ представлена на рисунке 6.

| 0.8V<br>X1 | 1 | 1 | 0 | 0 |      |

|------------|---|---|---|---|------|

| X2         | 1 | 0 | 1 | 0 |      |

| Zout       | 0 | 1 | 1 | 0 | t,ps |

Рисунок 6. Осциллограмма работы DC-LUT с количеством входных переменных n=2 при напряжении питания 0.8В при реализации логической функции исключающее ИЛИ

Осциллограмма работы ADC-LUT в режиме LUT и DC-LUT с количеством входных переменных n=2 при реализации функции исключающее ИЛИ представлена на рисунке 7 и рисунке 8.

| 0.8V<br>X1 | 0   | / 1 | 1     | 0 |      |

|------------|-----|-----|-------|---|------|

| X2         | / 1 | 1   | 0     | 0 |      |

| Zout       | 1   | 0   | <br>1 | 0 | t,ps |

Рисунок 7. Осциллограмма работы ADC-LUT в режиме DC-LUT с количеством входных переменных n=2 при напряжении питания 0.8B при реализации функции исключающее ИЛИ.

| 0.8V | 0 | 0 | 0   | / 1         |

|------|---|---|-----|-------------|

| X2   | 0 | 0 | / 1 | 1           |

| Zout | 1 | 0 | 1   | $\neg$ 0 tn |

Рисунок 8. Осциллограмма работы ADC-LUT в режиме LUT с количеством входных переменных n=2 при напряжении питания 0.8В при реализации функции исключающее ИЛИ

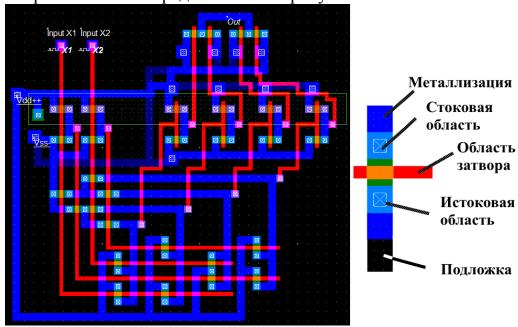

Разработанные топологии ЛЭ LUT и ЛЭ DC-LUT-BKN с количеством входных переменных n=2 представлены на рисунке 9.

Рисунок 9. Топология ЛЭ DC-LUT-BKN на 2 входные переменные, 32 нм

Разработанная топология ЛЭ DC-LUT-O с количеством входных переменных n=2 представлена на рисунке 10.

Рисунок 10. Топология ЛЭ DC-LUT-O на 2 входные переменные, 32 нм

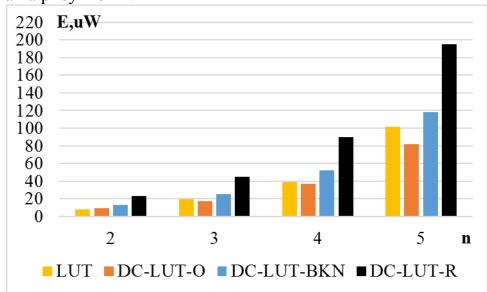

Полученная диаграмма изменения энергопотребления логических элементов LUT, DC-LUT(-R,-O,-BKN) для разного количества входных переменных при напряжении питания 0,8 B, реализующих 3 логические функции (m=3), представлена на рисунке 11.

Рисунок 11. Энергопотребление ЛЭ LUT, DC-LUT для разного количества входных переменных n при напряжении питания 0.8 B; количество реализуемых логических функций m=3

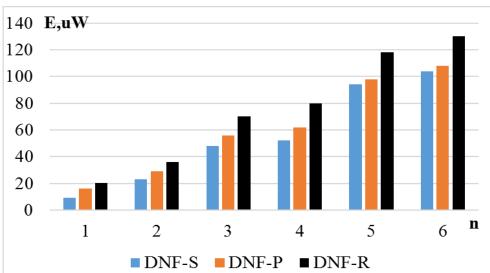

Диаграмма изменения энергопотребления логических элементов DNF(-S,-R,-P) для разного количества входных переменных при напряжении 0,8 В представлена на рисунке 12.

Рисунок 12. Энергопотребление ЛЭ ДНФ для разного количества входных переменных n, при напряжении питания 0,8 В; количество реализуемых логических функций m=3

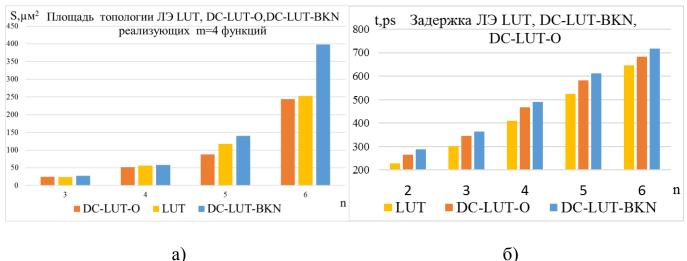

Диаграмма значений площади топологий и диаграмма значений максимальной задержки логических элементов LUT, DC-LUT (-BKN, -O) для различных n, реализующих 4 логические функции (m=4), представлены на рисунке 13 (a, b).

Выполненное моделирование подтверждает работоспособность предложенных устройств DC-LUT-O, DC-LUT-BKN, ADC-LUT и DNF-S, DNF-P на различных частотах (до 2ГГц) при напряжении питания (от 0,35 до 1,2В).

Рисунок 13. Моделирование ЛЭ LUT, DC-LUT-O, DC-LUT-BKN для разного количества входных переменных n, количество реализуемых логических функций m=4: а) площадь топологий б) максимальная задержка

Анализ показал, что при реализации систем функций в СДНФ уже при количестве функций *m*=4 предпочтительным по энергопотреблению ЛЭ является DC-LUT-O в отличии от существующего LUT и предлагаемых DC-LUT-BKN с блоками конституент нуля и DC-LUT-R с нагрузочным транзистором, при этом задержка предлагаемых ЛЭ снижается незначительно в сравнении с существующим LUT. Наибольший выигрыш достигается при реализации дешифратора на *п* переменных. Для реализации систем функций в ДНФ предпочтительным ЛЭ как по быстродействию, так и по энергопотреблению является DNF-S с последовательной реализацией в отличии от ЛЭ DNF-P с параллельной реализацией и существующего ЛЭ DNF-R.

**В четвертой главе** выполняется оценка эффективности разработанных устройств по количеству транзисторов, площади топологии, максимальной задержке, энергопотреблению. Реализация DC LUT оценивается выражением:

$$L_{dc-nk} = 2^{\lfloor n \rfloor} \cdot 8 + (2^{\lfloor k \rfloor + 1} + 6 \lfloor k \rfloor) \cdot \sum_{i=1}^{\lfloor \lfloor n \rfloor} 2^{\lfloor n \rfloor - \lfloor i \rfloor \lfloor k \rfloor} + (2^{\lfloor n \rfloor - \lfloor \lfloor n \rfloor \rfloor - \lfloor \lfloor k \rfloor \rfloor - \lfloor \lfloor k \rfloor \rfloor - \lfloor \lfloor n \rfloor - \lfloor \lfloor n \rfloor \rfloor - \lfloor \lfloor n \rfloor - \lfloor n \rfloor - \lfloor n \rfloor - \lfloor n \rfloor - \lfloor n \rfloor - \lfloor \lfloor n \rfloor - \lfloor n \rfloor -$$

где  $2^{\lfloor k \rfloor + 1} + 6 \lfloor k \rfloor$  - сложность одного k-дерева  $\lfloor \ldots \rfloor$ -округление в нижнюю строну (floor); таких деревьев (k-LUT) необходимо в первом слое  $2^{\lfloor n \rfloor + \lfloor k \rfloor}$ , затем нужно провести декомпозицию k-LUT этого первого слоя, получаем  $2^{\lfloor n \rfloor + \lfloor k \rfloor + \lfloor k \rfloor}$  Всего необходимо i

k-LUT, где i определяется из соотношения:  $\lfloor i \rfloor = \left\lfloor \frac{\lfloor n \rfloor}{\lfloor k \rfloor} \right\rfloor$  всего  $\sum_{i=1}^{\left\lfloor \frac{\lfloor n \rfloor}{\lfloor k \rfloor} \right\rfloor} 2^{\lfloor n \rfloor - \lfloor i \rfloor \lfloor k \rfloor}$  и последний LUT на  $\lfloor n \rfloor - \left\lfloor \frac{\lfloor n \rfloor}{\lfloor k \rfloor} \right\rfloor \cdot \lfloor k \rfloor$  переменных.

Сложность ADC-LUT описывается выражением:

$$L_{adc-n,k} = 2^{\lfloor n \rfloor} \cdot 8 + (2^{\lfloor k \rfloor + 1} + 6 \lfloor k \rfloor) \cdot \sum_{i=1}^{\lfloor \lfloor n \rfloor} 2^{\lfloor n \rfloor - \lfloor i \rfloor \lfloor k \rfloor} + (2^{\lfloor n \rfloor - \lfloor \lfloor n \rfloor \rfloor \lfloor \lfloor k \rfloor \rfloor} + 6 \cdot \left( \lfloor n \rfloor - \left\lfloor \frac{\lfloor n \rfloor}{\lfloor k \rfloor} \right\rfloor \lfloor \lfloor k \rfloor \right) + 6 \lfloor n \rfloor + 2^{\lfloor n \rfloor} (17) + 6m(2^n + 2) + 14$$

(16)

где  $2^{\lfloor n\rfloor}$ (17) - сложность конфигурации выходов, 17 — сложность конфигурации корня дерева,  $6m(2^n+2)$  - сложность m блоков реализации функций в СДНФ.

При использовании DNF-LUT получаем сложность в количестве транзисторов:

$$L_{dnf} = \lfloor v \rfloor (6 \lfloor n \rfloor) + 6 \cdot \lfloor m \rfloor (\lfloor v \rfloor + 2) + 3 \left| \frac{n}{r} \right| \lfloor k \rfloor, \tag{17}$$

где  $\lfloor v \rfloor$  (6 $\lfloor n \rfloor$ ) учитывает сложность реализации v настраиваемых конъюнкций; 6· $\lfloor m \rfloor$  ( $\lfloor v \rfloor$ +2) -сложность m блоков функций от v конъюнкций (реализация монтажного И), 3 $\lfloor \frac{n}{r} \rfloor$   $\lfloor k \rfloor$ - учитывает r ограничения Мида-Конвей и восстановитель по k конъюнкциям, сложностью 3 транзистора (инвертор и дополнительный р-транзистор).

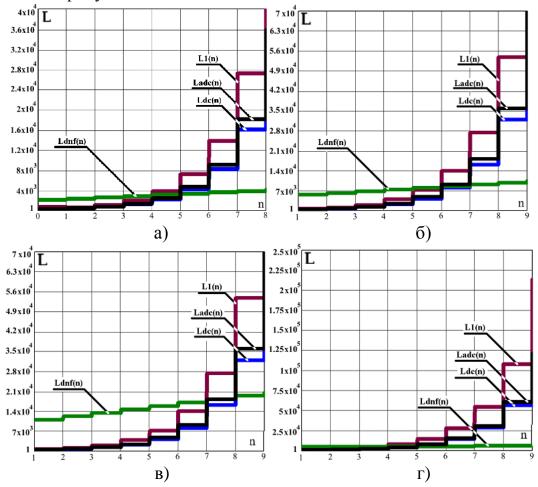

Графики сравнения сложности ЛЭ LUT, ADC-LUT, DC-LUT, DNF представлены на рисунке 14.

Рисунок 14. Сравнение сложности L1(n), Ldc(n), Ldnf(n), Ladc(n) при: а) m=8; k=3; v=20; б) m=8; k=3; v=50в) m=8; k=3; v=100; г) m=16, k=3, v=20

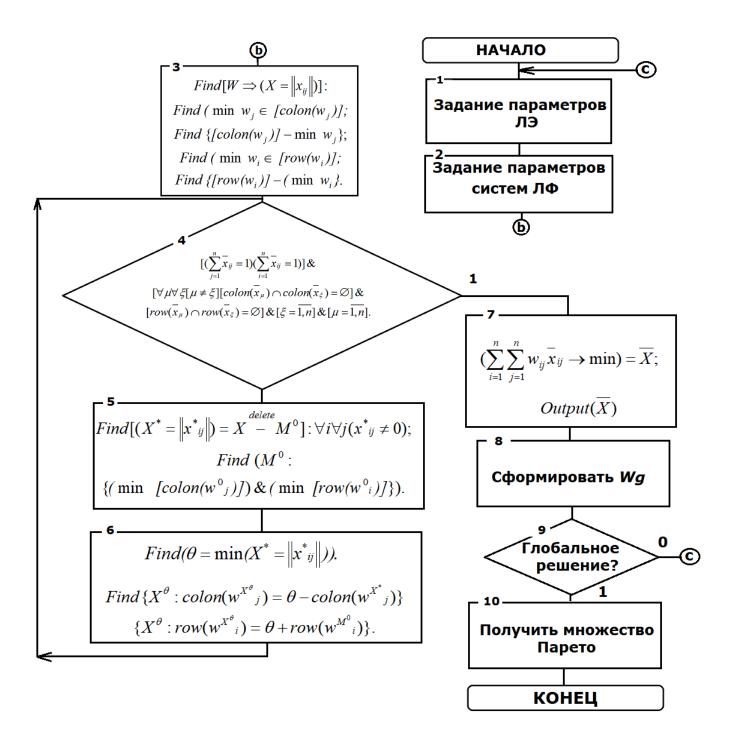

Разрабатывается алгоритм оптимизации набора логических элементов ПЛИС FPGA для реализации типовых систем логических функций с использованием венгерского метода. Предлагаемая матрица назначений имеет вид – рисунок 15.

| № Вариантов наборов    | нтов наборов Средние характеристики различных систем |      |      |  |      |  |  |

|------------------------|------------------------------------------------------|------|------|--|------|--|--|

| логических элементов і | логических функций в проектах ј                      |      |      |  |      |  |  |

|                        | 1                                                    | 2    | 3    |  | s=n  |  |  |

| 1                      | W1.1                                                 | W1.2 | W1.3 |  | W1.s |  |  |

| 2                      | W2.1                                                 | W2.2 | W2.3 |  | W2.s |  |  |

| 3                      | W3.1                                                 | W3.2 | W3.3 |  | W3.s |  |  |

| • • •                  |                                                      |      |      |  |      |  |  |

| v=n                    | Wv.1                                                 | Wv.2 | Wv.3 |  | Wv.s |  |  |

Рисунок 15 Матрица назначений при оптимизации набора логических элементов ПЛИС FPGA

Предлагается использовать известный венгерский метод оптимизации итеративно - для получения нескольких назначений по параметрам логических элементов и систем логических функций так, чтобы из частичных решений в дальнейшем построить глобальную таблицу назначений и получить глобальные назначения, которые и описывают требуемый результат выбора.

Вводятся процедуры задания параметров логических элементов (блок 1) с использованием результатов расчета по полученным оценкам сложности и по результатам моделирования. Вводится процедура задания параметров систем логических функций (блок 2). Вводится блок получения Парето-оптимальных решений (блок 10). Разработана программа выбора оптимального набора логических элементов.

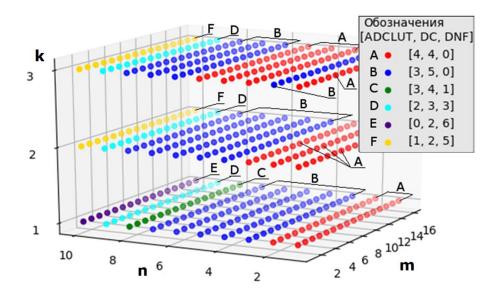

Результаты оптимизации по вариантам наборов элементов представлены на рисунке 16. Видно, что при большом числе переменных n и функций m предпочтительными вариантами АЛМ становятся наборы, включающие ЛЭ DNF. Предлагаемый алгоритм представлен на рисунке 17.

Рисунок 16 Результаты оптимизации наборов логических элементов.

Рисунок 17. Предлагаемый алгоритм оптимизации набора логических элементов ПЛИС FPGA на основе венгерского метода

**В** заключении приведены основные результаты диссертационного исследования, сформулированы выводы и определены основные направления развития предложенных подходов.

**В приложениях** представлены: результаты моделирования, топологии, листинг программы для ЭВМ, документы, подтверждающие внедрение результатов диссертационной работы.

#### ЗАКЛЮЧЕНИЕ

Выполненная диссертационная работа посвящена решению актуальной научной задачи выбора оптимального набора логических элементов для адаптивногибридной реализации систем логических функций в ПЛИС FPGA. В диссертационной работе поставлены и решены следующие задачи исследования:

- 1. Разработан усовершенствованный метод реализации логических функций в СДНФ на основе предложенного адаптивного логического элемента ADC-LUT, который может работать как в режиме LUT, так и в режиме DC-LUT. Адаптивный ЛЭ в режиме DC-LUT реализует системы функций, что позволяет снизить аппаратные затраты ориентировочно на 15-20% при реализации 8 функций от 4 входных переменных.

- 2. Разработан усовершенствованный метод реализации логических функций в ДНФ, отличающийся тем, что использовано оригинальное кодирование конъюнкций, что способствует реализации систем функций большего числа переменных, практически нереализуемых в LUT.

- 3. Получены оценки сложности реализации систем логических функций на основе разработанных логических элементов, которые позволили оценить выигрыш в количестве транзисторов, в площади топологии и доказать предпочтительность DC-LUT в сравнении с LUT при реализации систем функций большого числа переменных.

- 4. Разработаны исследованы модели предложенных логических элементов ПЛИС FPGA для реализации типовых систем логических функций, DC-LUT, **ADC-LUT** показывают, ЧТО обладают большими которые функциональными возможностями при незначительном снижении задержки и существенном выигрыше в энергопотреблении перед реализацией на нескольких существующих LUT систем, содержащих большое число функций от одинаковых переменных.

- 5. Разработан алгоритм оптимизации набора логических элементов FPGA для реализации систем логических функций, используемых в типовых проектах на ПЛИС, который позволяет на основе венгерского метода и получения множества Парето установить наиболее предпочтительные наборы предлагаемых ЛЭ в АЛМ.

- 6. Направлениями дальнейшей работы может быть использование транзисторов Tri-Gate, а также разработка новых подходов к обеспечению надёжности предложенных ЛЭ, а также адаптация к области самосинхронной схемотехники.

# СПИСОК ПУБЛИКАЦИЙ ПО ТЕМЕ ДИССЕРТАЦИОННОЙ РАБОТЫ Публикации в ведущих рецензируемых научных изданиях

- 1. Тюрин, С.Ф. Усовершенствованный метод реализации в FPGA систем логических функций, заданных в СДНФ [Электронный ресурс] / С.Ф. Тюрин, **Р.В. Вихорев** // Инженерный вестник Дона. 2017. № 1. С. 10 Режим доступа: http://www.ivdon.ru/ru/magazine/archive/n1y2017/4044

- 2. Вихорев Р.В. Программируемые логические элементы ПЛИС FPGA для реализации систем логических функций / **Р.В. Вихорев**, С.Ф. Тюрин // Вестник Пермского национального исследовательского политехнического университета.

Электротехника, информационные технологии, системы управления. —  $2017. - N_{\odot} 23.$  — С. 133-145.

- 3. Вихорев Р.В. Моделирование и оптимизация инновационных логических элементов ПЛИС. / **Р.В. Вихорев**, А.С. Прохоров, С.Ф. Тюрин, А.С. Никитин // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления.  $-2017. N \cdot 24. C. 192-208.$

- 4. Тюрин С.Ф. Адаптивный логический модуль ПЛИС с архитектурой FPGA. / С.Ф. Тюрин, **Р.В. Вихорев** // Вестник Рязанского государственного радиотехнического университета. -2018. -№63. С. 69-76.

- 5. Вихорев Р.В Топологическое моделирование логических элементов нейронных сетей / Р.В. Вихорев, М.С. Никитин, С.Ф. Тюрин // Нейрокомпьютеры: разработка, применение. 2019. № 73. С. 45-55.

# Публикации в изданиях, индексируемых в международных базах цитирования Web of Science и Scopus

- 6. **Vikhorev R.** Universal logic cells to implement systems functions. / R. Vikhorev // Proceedings of the 2016 IEEE North West Russia Section Young Researchers in Electrical and Electronic Engineering Conference. EIConRusNW-2016. 2016. PP. 404-406. (Scopus)

- 7. **Vikhorev R.** Improved FPGA logic elements and their simulation. / R. Vikhorev //Proceedings of the 2018 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering. EIConRus. 2018. PP. 275-280. (Scopus)

## Свидетельства о государственной регистрации программ для ЭВМ

8. Свидетельство о государственной регистрации программы для ЭВМ №2017663289 «Программа оптимизации набора логических элементов модифицированным венгерским методом «ВЕННИТ»» / Тюрин С.Ф., Никитин А.С., **Вихорев Р.В.**, Скорнякова А.Ю., Прохоров А.С. Дата регистрации 28.11.2017

#### Патенты РФ

- 9. Тюрин С.Ф. Программируемое логическое устройство / С.Ф. Тюрин, А.Ю. Городилов, **Р.В. Вихорев** // Патент на изобретение №2547229; опубл. 10.04.2015, Бюл. №10.-16 с.

- 10. Тюрин С.Ф. Программируемое логическое устройство / С.Ф. Тюрин, **Р.В. Вихорев** // Патент на изобретение №2573732; опубл. 27.01.2016, Бюл. №3. -15 с.

- 11. Тюрин С.Ф. Программируемое логическое устройство / С.Ф. Тюрин, **Р.В. Вихорев,** А.Ю. Плотникова // Патент на изобретение № 2602780; опубл. 20.11.2016, Бюл. №32. 19 с.

## Публикации в прочих изданиях, в том числе материалы конференций

- 12. Тюрин С.Ф. Модифицированный логический элемент LUT FPGA. / С.Ф. Тюрин, А.Ю. Городилов, **Р.В. Вихорев** // Вестник Пермского университета. Серия: Математика. Механика. Информатика. 2014. № 1 (24). С. 69-74.

- 13. Вихорев Р.В. Обзор методов тестирования и диагностики FPGA. / **Р.В. Вихорев,** Ю.Е. Зажигин // В сборнике: Актуальные вопросы образования и

- науки сборник научных трудов по материалам Международной научнопрактической конференции: в 14 частях. 2014. С. 44-47.

- 14. Вихорев Р.В. Логическая ячейка для реализации систем функций / **Р.В. Вихорев** // 14-я Международная конференция «Авиация и космонавтика-2015» Москва. -2015. С. 170-171.

- 15. Вихорев Р.В. Усовершенствованные методы реализации программируемой логики. / **Р.В. Вихорев**, А.С. Прохоров, А.Ю. Скорнякова, С.Ф. Тюрин // Управление большими системами. УБС-2017 материалы XIV Всероссийской школы-конференции молодых ученых. Пермь- 2017. С. 306-315.

- 16. Никитин А.С. Оптимизация LUT FPGA на основе модифицированного венгерского метода / А.С. Никитин, **Р.В. Вихорев**, А.Ю. Скорнякова //Управление большими системами УБС-2017 Материалы 14 Всероссийской школы-конференции молодых ученых Пермь, 2017. С. 563-572.

- 17. Тюрин С.Ф Выбор набора конфигурируемых логических элементов с использованием венгерского метода / С.Ф. Тюрин, А.С. Никитин, **Р.В. Вихорев**, А.Ю. Скорнякова // Вестник пермского университета. Серия: Математика. Механика. Информатика. 2017. Вып. 2(37). С. 65-68.

- 18. Вихорев Р.В. Моделирование усовершенствованных устройств программируемой логики / **Р.В. Вихорев**, А.Ю.Скорнякова // Вестник пермского университета. Серия: Математика. Механика. Информатика. 2017. Вып.3 С. 77-81.

- 19. Вихорев Р.В. Особенности моделирования и оптимизации комплекта новых логических элементов ПЛИС / **Р.В. Вихорев** // Вестник Пермского университета. Серия: Математика. Механика. Информатика. 2018. № 3. С. 111-116.

- 20. Vikhorev R.V. Implementation of systems of logic functions based on LUT FPGA. / **R.V. Vikhorev** // Инновационные процессы в исследовательской и образовательной деятельности. 2015. Т.1. С. 13-16.

- 21. Tyurin S. Advanced FPGA Look up tables. / S. Tyurin, A. Grekov, **R. Vikhorev**, A. Prokhorov // International Journal of Pure and Applied Mathematics. 2017. vol. 117 no. 22. PP. 143-147.