# Федеральное государственное бюджетное образовательное учреждение высшего образования ПЕРМСКИЙ НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

На правах рукописи

# ВИХОРЕВ Руслан Владимирович

# ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ ПЛИС FPGA ДЛЯ РЕАЛИЗАЦИИ СИСТЕМ ФУНКЦИЙ

05.13.05 – Элементы и устройства вычислительной техники и систем управления

### ДИССЕРТАЦИЯ

на соискание ученой степени кандидата технических наук

Научный руководитель: доктор технических наук, профессор Тюрин С.Ф.

# Оглавление

| Введение6                                                                |

|--------------------------------------------------------------------------|

| Глава 1. Исследование методов и средств реализации систем логических     |

| функций в существующих ПЛИС. Постановка задачи исследования 12           |

| 1.1. Анализ существующих БИС программируемой логики                      |

| 1.2. Анализ адаптивных многоразрядных логических элементов FPGA 21       |

| 1.3. Анализ научно-методического аппарата оптимизации логики ПЛИС 26     |

| 1.4. Постановка задачи исследования                                      |

| 1.5. Выводы по главе 1                                                   |

| Глава 2. Разработка усовершенствованных методов реализации в FPGA систем |

| логических функций                                                       |

| 2.1. Усовершенствованный метод реализации в FPGA систем логических       |

| функций, заданных в СДНФ                                                 |

| 2.2. Разработка адаптивного логического элемента                         |

| 2.3. Усовершенствованный метод реализации в FPGA систем логических       |

| функций, заданных в ДНФ46                                                |

| 2.4 Выводы по главе 2                                                    |

| Глава 3. Моделирование разработанных устройств для реализации систем     |

| логических функций в ПЛИС - FPGA54                                       |

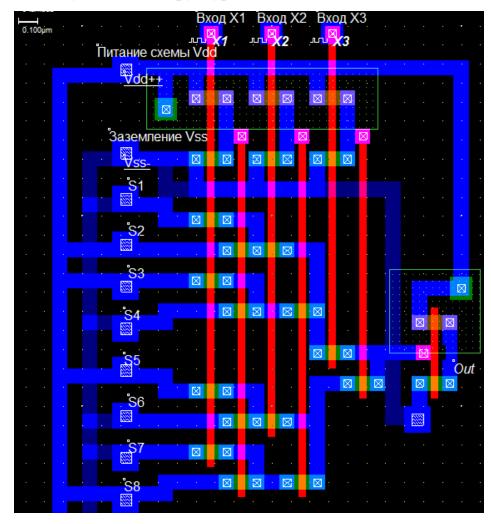

| 3.1. Моделирование логического элемента – LUT                            |

| 3.1.1. Статическое моделирование логического элемента - LUT 54           |

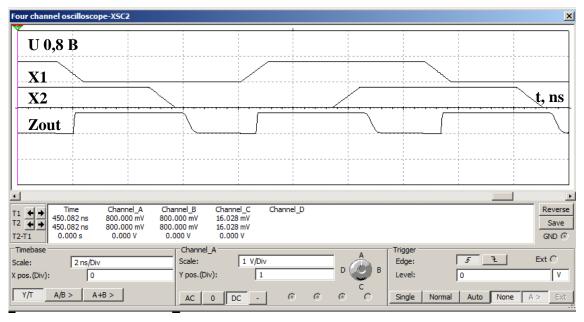

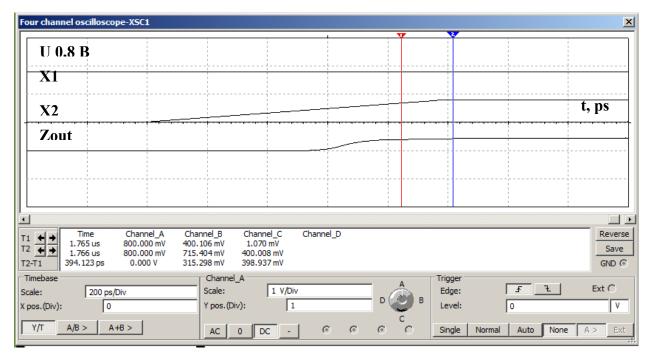

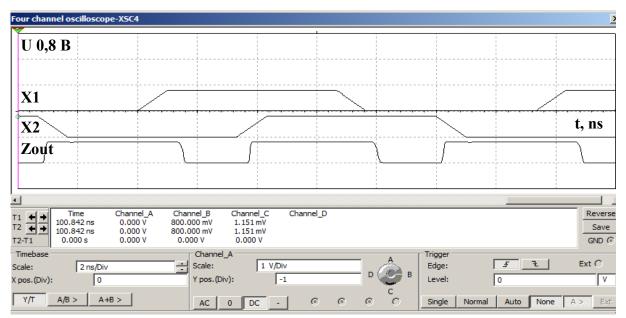

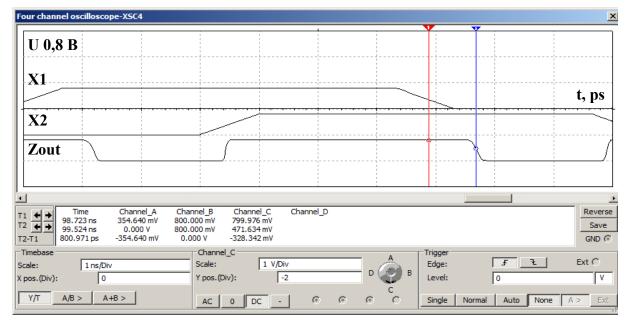

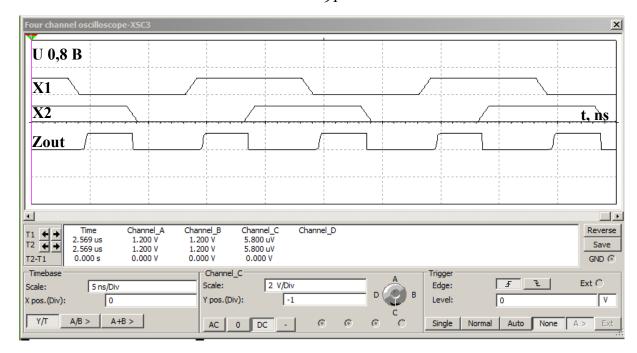

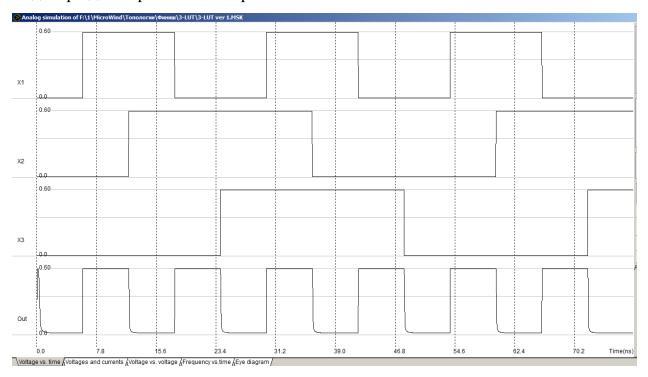

| 3.1.2. Динамическое моделирование логического элемента - LUT 57          |

| 3.2. Моделирование логического элемента – дешифратора DC-LUT 59          |

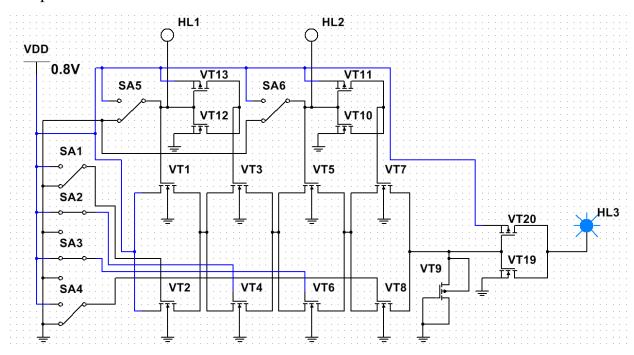

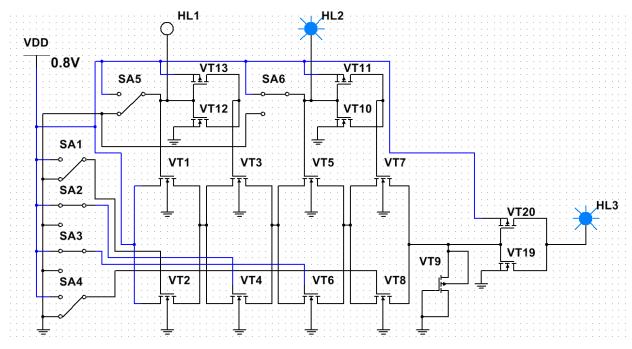

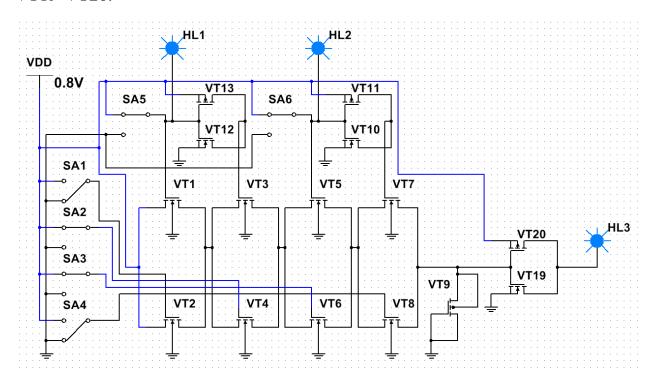

| 3.2.1 Статическое моделирование логического элемента – DC-LUT-O 59       |

| 3.2.2 Статическое моделирование логического элемента – DC-LUT-R 62       |

| 3.2.3 Статическое моделирование логического элемента – DC-LUT-BKN 64     |

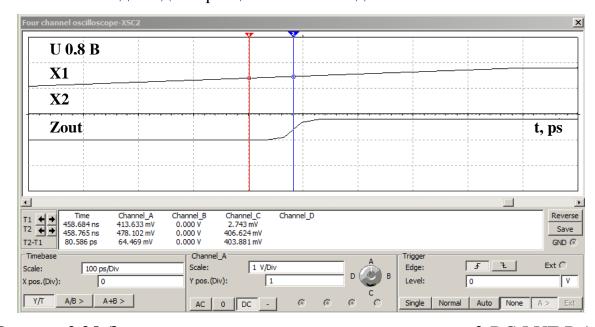

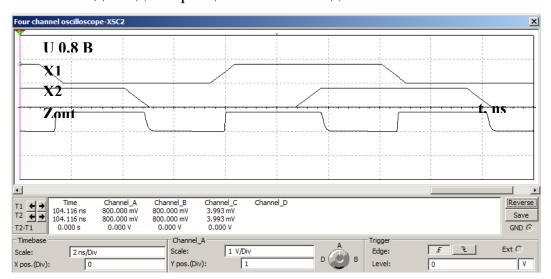

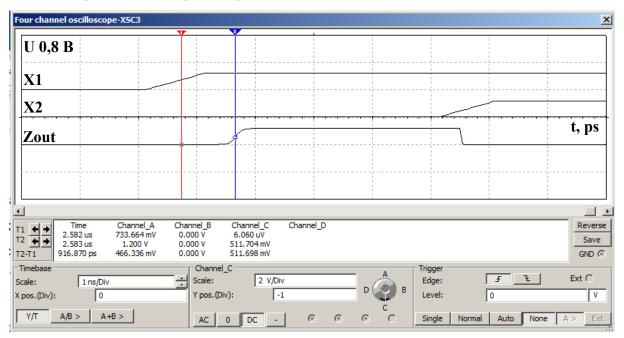

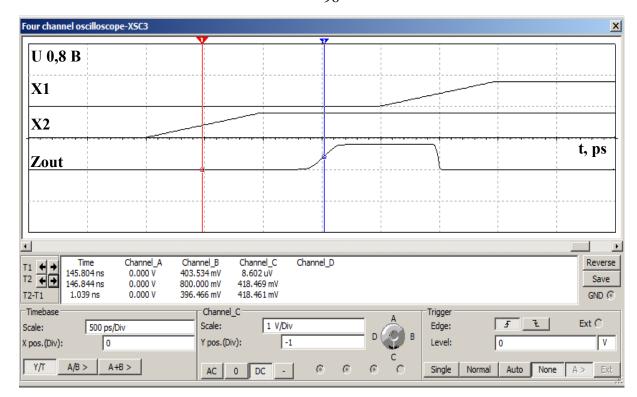

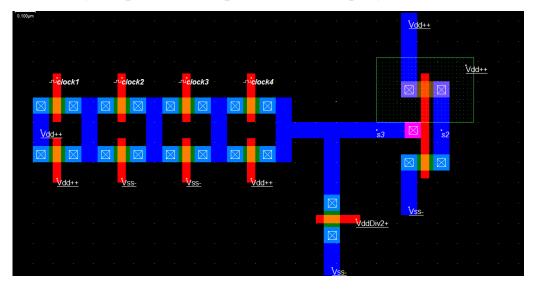

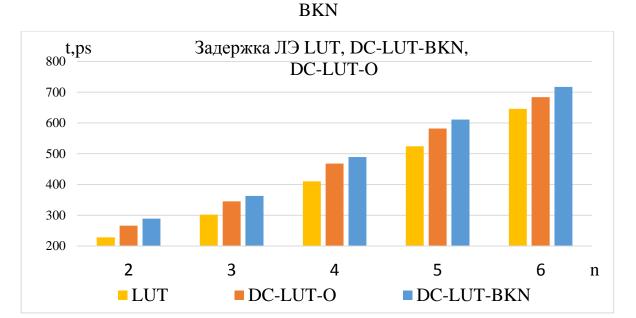

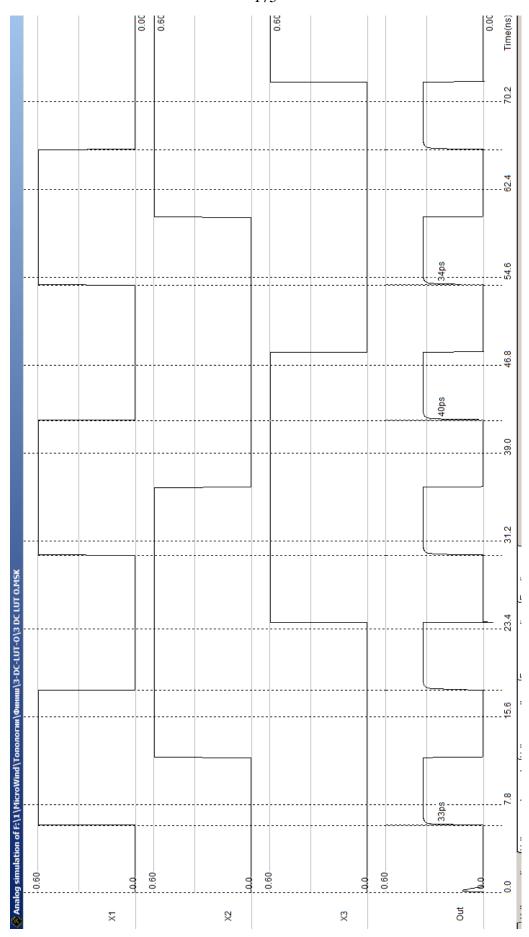

| 3.2.4. Динамическое моделирование логического элемента – DC-LUT-O 67     |

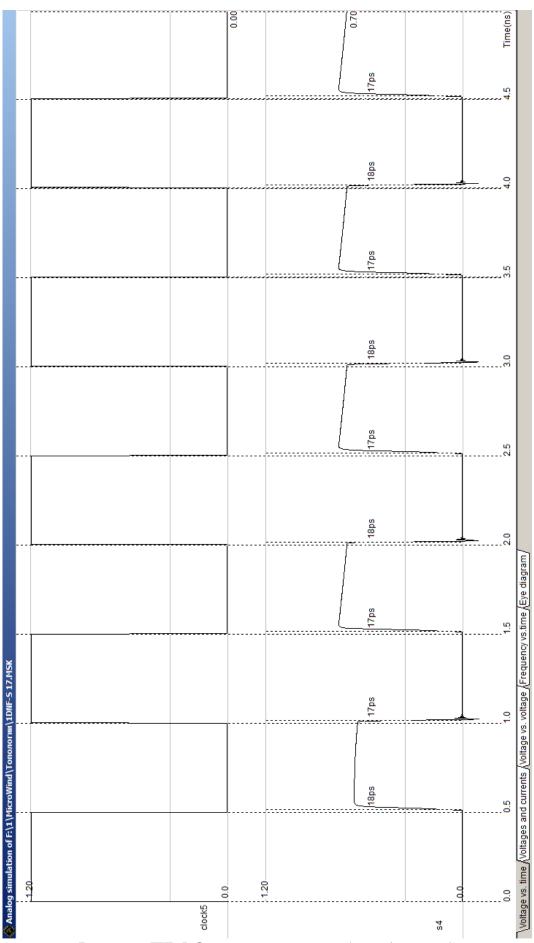

| 3.2.5. Динамическое моделирование логического элемента – DC-LUT-R 69     |

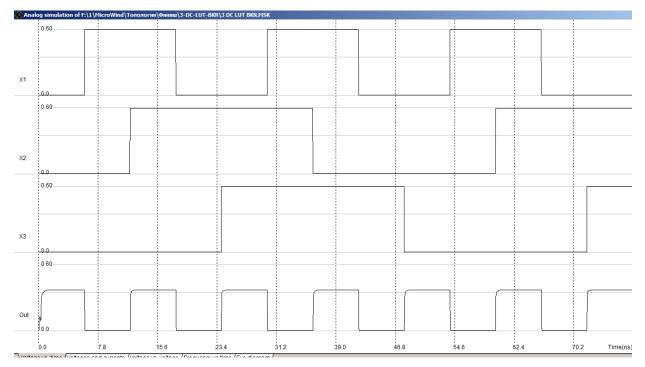

| 3.3. Моделирование логического элемента ADC-LUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.2.6. Динамическое моделирование логического элемента – DC-LUT-BKN   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

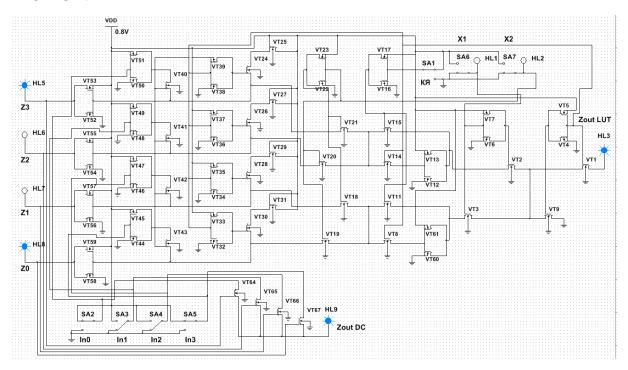

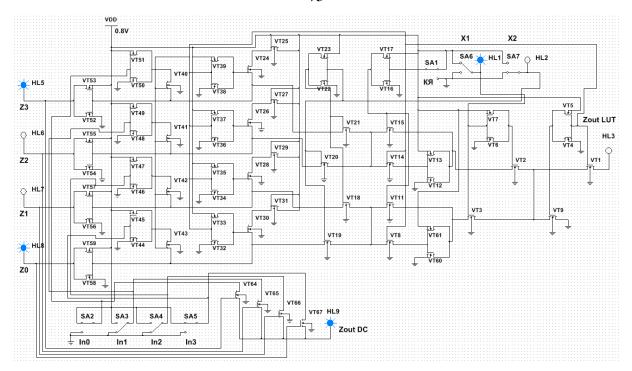

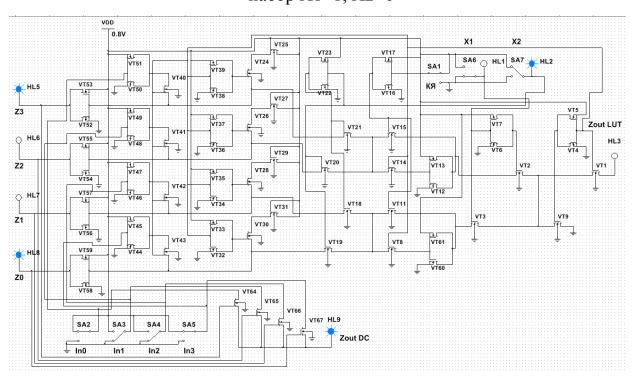

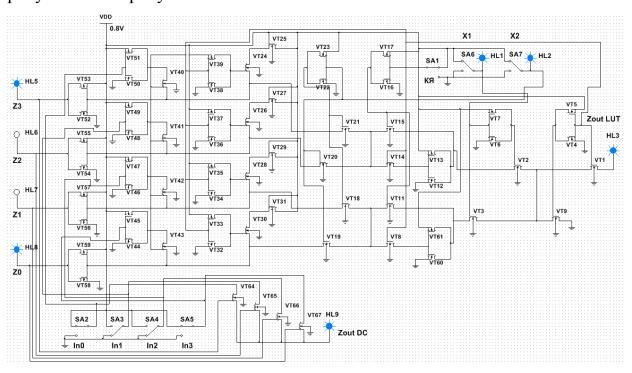

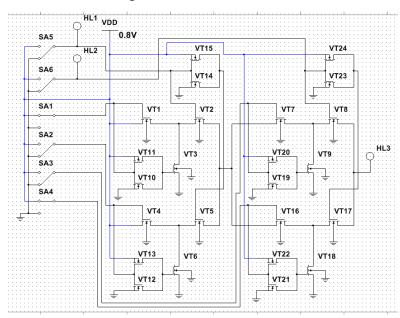

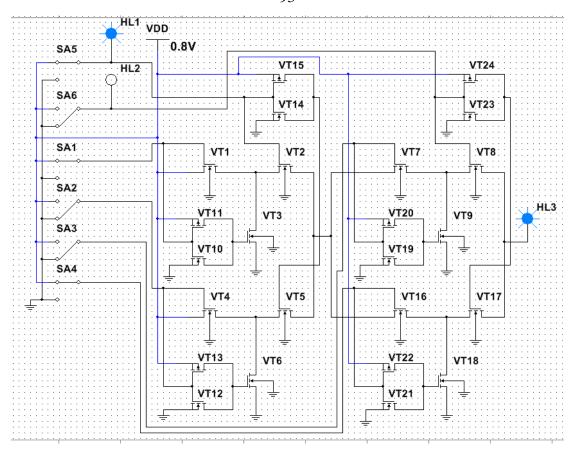

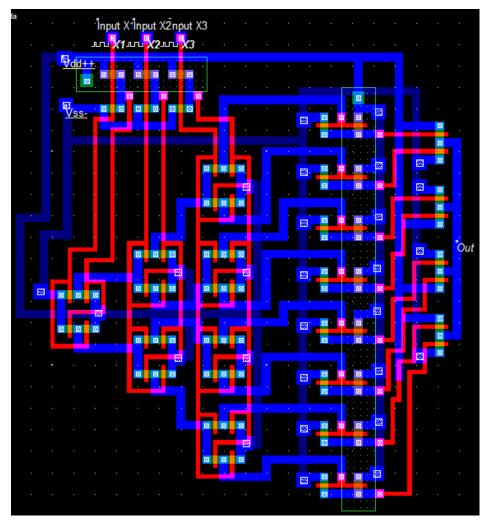

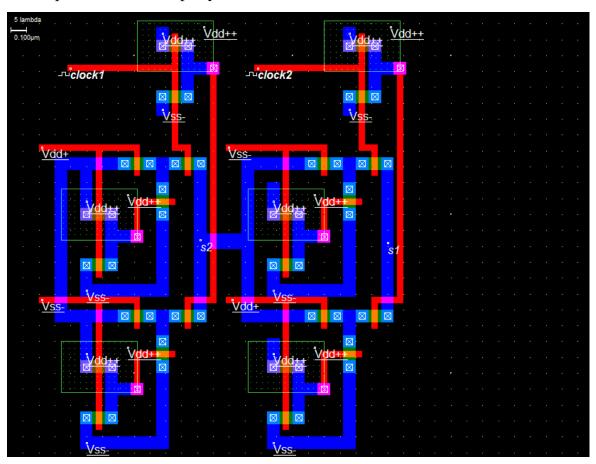

| 3.3.1 Статическое моделирование логического элемента ADC-LUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71                                                                    |

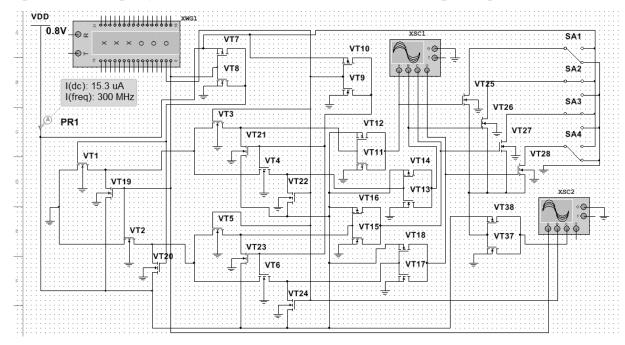

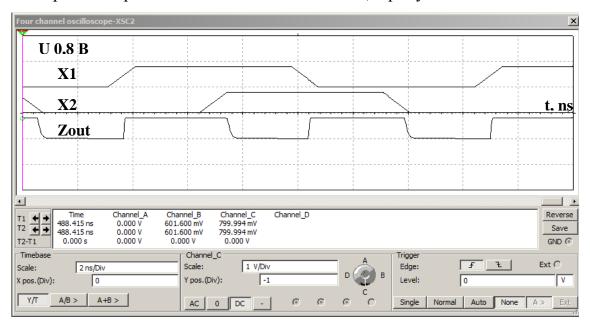

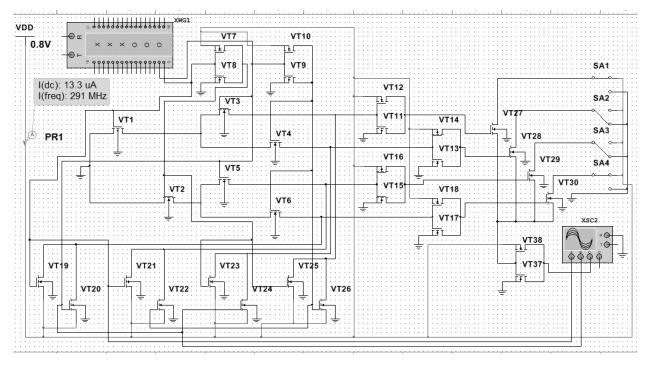

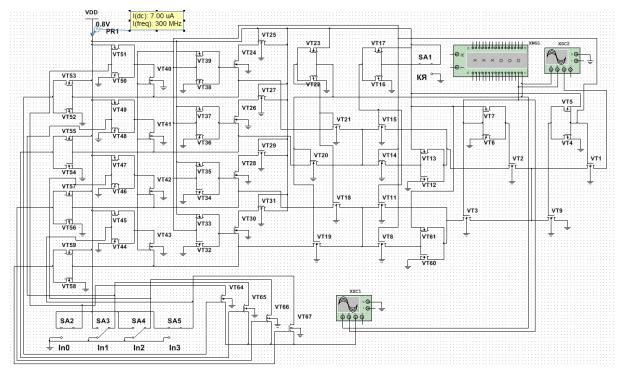

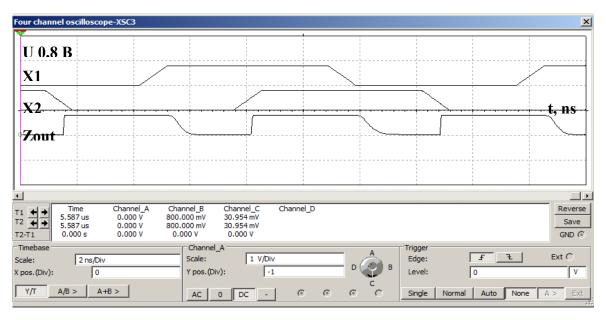

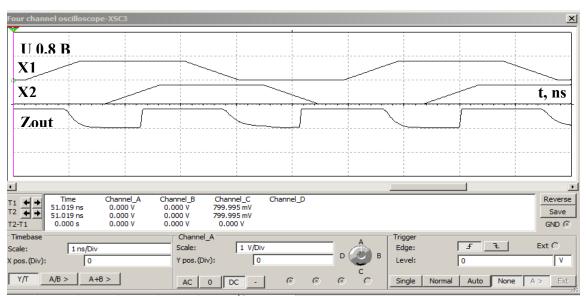

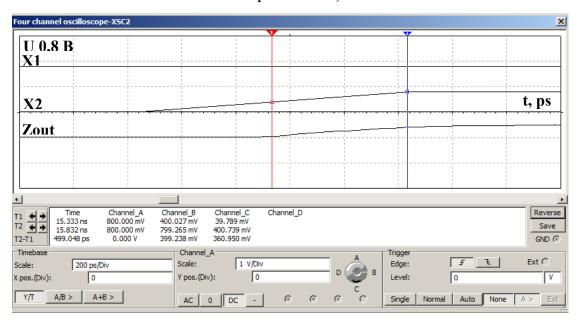

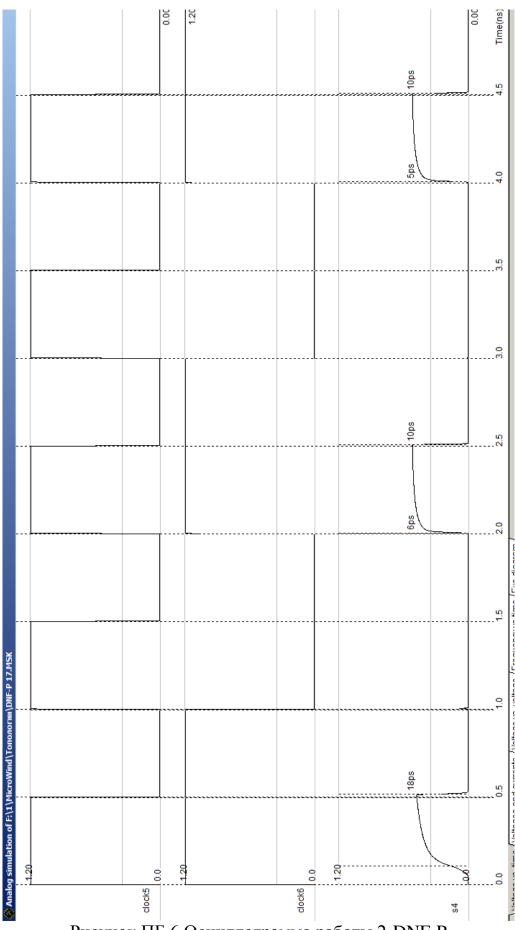

| 3.3.2. Динамическое моделирование логического элемента — ADC-LUT 78 3.4. Моделирование одного разряда блока конъюнкций для ДНФ реализации логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.3. Моделирование логического элемента ADC-LUT                       |

| 3.4. Моделирование одного разряда блока конъюнкций для ДНФ реализации логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.3.1 Статическое моделирование логического элемента ADC-LUT 73       |

| 3.4.1 Статическое моделирование блока конъюнкций для ЛЭ DNF-R с нагрузочным транзистором для реализации систем логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3.2. Динамическое моделирование логического элемента – ADC-LUT 78   |

| 3.4.1 Статическое моделирование блока конъюнкций для ЛЭ DNF-R с нагрузочным транзистором для реализации систем логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.4. Моделирование одного разряда блока конъюнкций для ДНФ реализации |

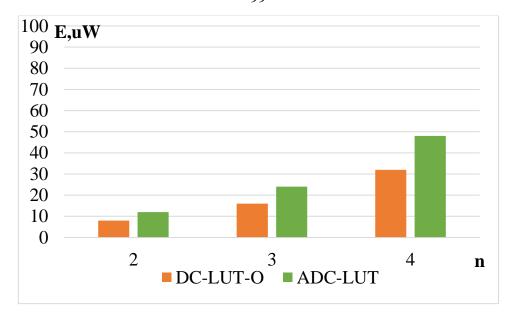

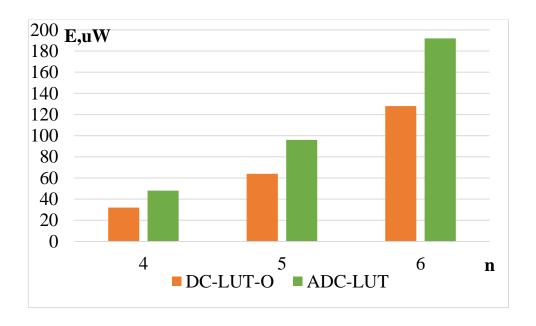

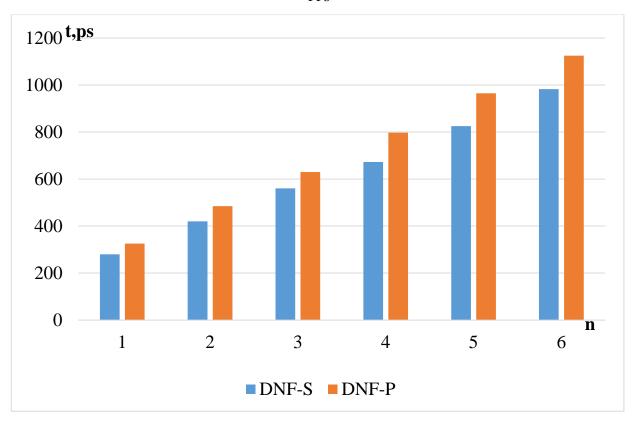

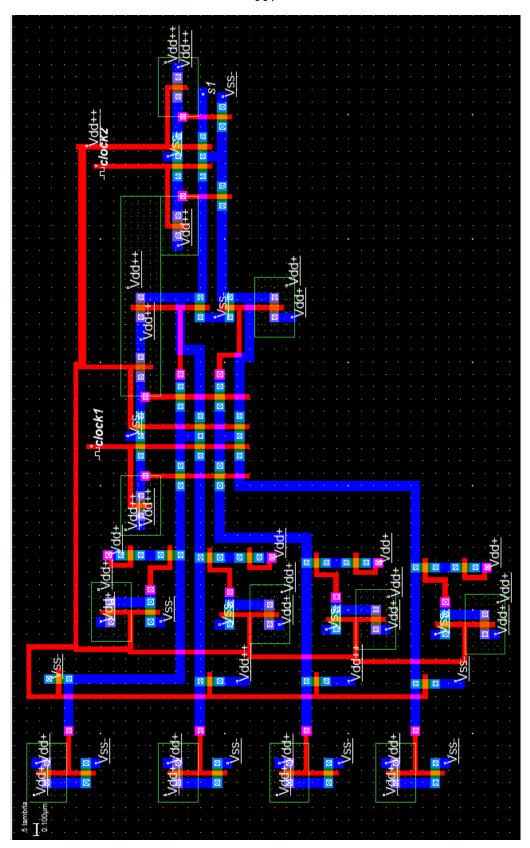

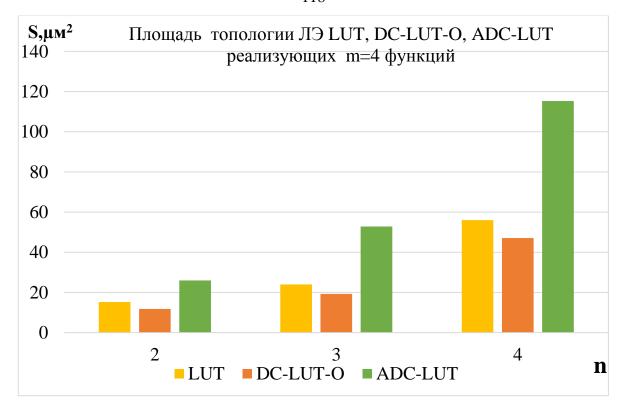

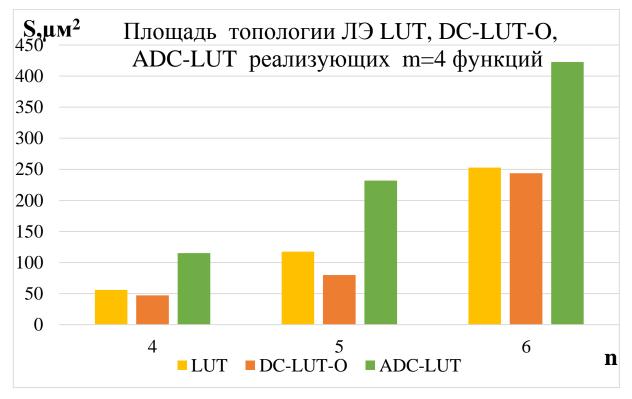

| нагрузочным транзистором для реализации систем логических функций в ПЛИС 81  3.4.2 Динамическое моделирование блока конъюнкций для ЛЭ DNF-R с нагрузочным транзистором для реализации систем логических функций в ПЛИС 84  3.4.3. Статическое моделирование блока конъюнкций для ЛЭ DNF-P с параллельным подключением для реализации систем логических функций в ПЛИС 87  3.4.4. Динамическое моделирование блока конъюнкций для ЛЭ DNF-P с параллельным подключением для реализации систем логических функций в ПЛИС 90  3.4.5. Статическое моделирование блока конъюнкций для ЛЭ DNF-S с последовательным подключением для реализации систем логических функций в ПЛИС 92  3.4.6. Динамическое моделирование блока конъюнкций для ЛЭ DNF-S с последовательным подключением для реализации систем логических функций в ПЛИС 94  3.5. Сравнительная оценка энергопотребления ЛЭ DC-LUT, DNF-LUT и ADC 96 | логических функций в ПЛИС81                                           |

| ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.4.1 Статическое моделирование блока конъюнкций для ЛЭ DNF-R с       |

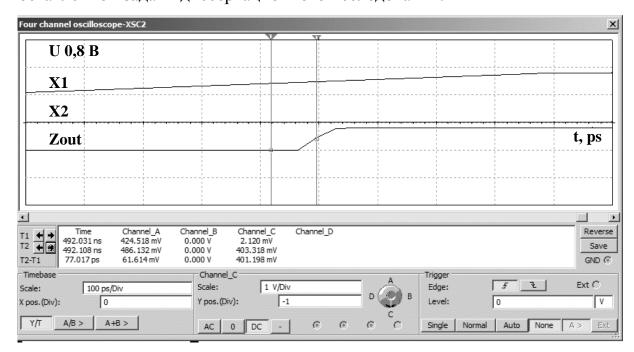

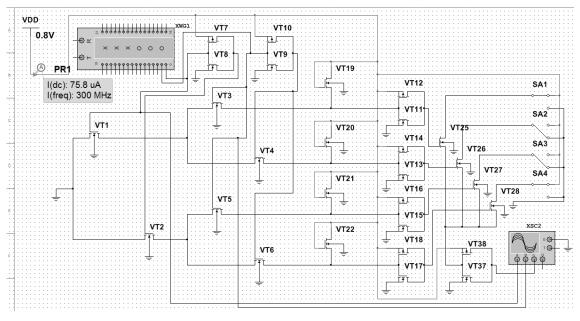

| 3.4.2 Динамическое моделирование блока конъюнкций для ЛЭ DNF-R с нагрузочным транзистором для реализации систем логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                       |

| нагрузочным транзистором для реализации систем логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11ЛИС81                                                               |

| 3.4.3. Статическое моделирование блока конъюнкций для ЛЭ DNF-P с параллельным подключением для реализации систем логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | нагрузочным транзистором для реализации систем логических функций в   |

| параллельным подключением для реализации систем логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | параллельным подключением для реализации систем логических функций в  |

| последовательным подключением для реализации систем логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | параллельным подключением для реализации систем логических функций в  |

| функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.4.5. Статическое моделирование блока конъюнкций для ЛЭ DNF-S с      |

| <ul> <li>3.4.6. Динамическое моделирование блока конъюнкций для ЛЭ DNF-S с последовательным подключением для реализации систем логических функций в ПЛИС</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •                                                                     |

| последовательным подключением для реализации систем логических функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | функций в ПЛИС92                                                      |

| функций в ПЛИС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.4.6. Динамическое моделирование блока конъюнкций для ЛЭ DNF-S с     |

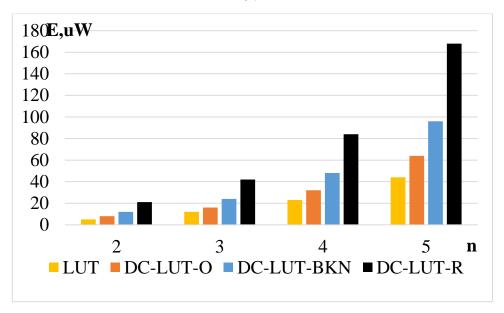

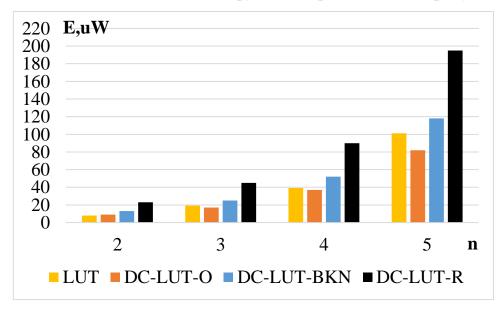

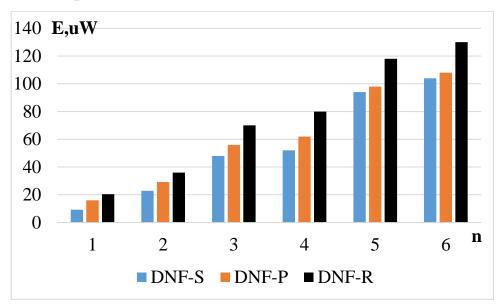

| 3.5. Сравнительная оценка энергопотребления ЛЭ DC-LUT, DNF-LUT и ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ·                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.5. Сравнительная оценка энергопотребления ЛЭ DC-LUT, DNF-LUT и ADC  |

| , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                       |

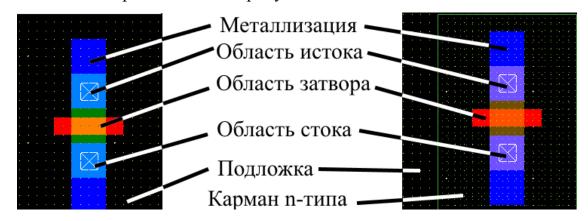

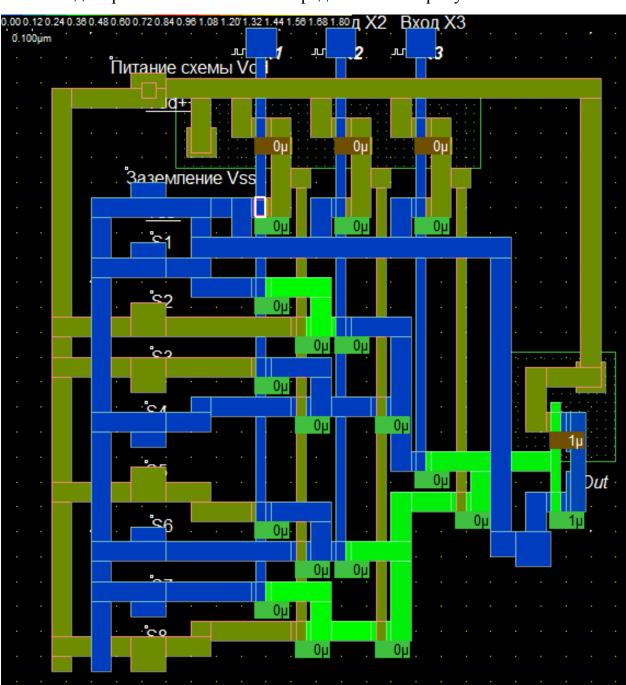

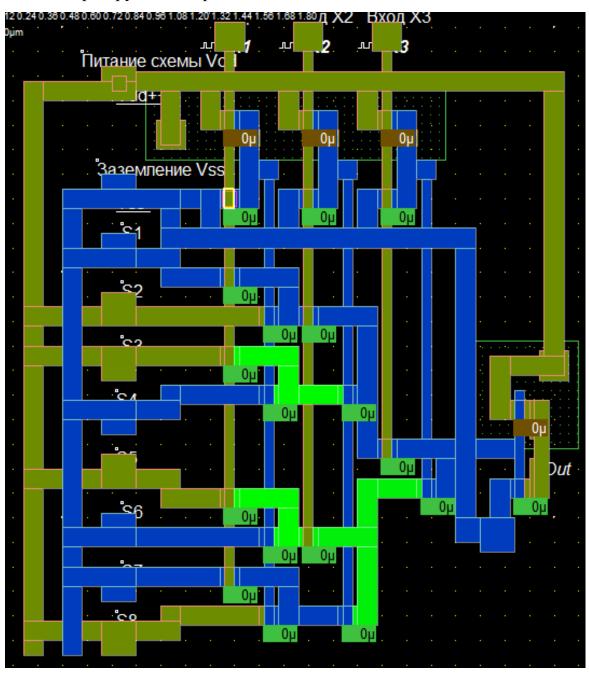

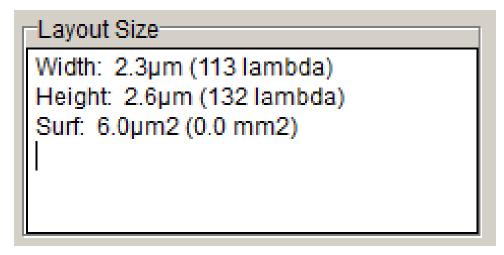

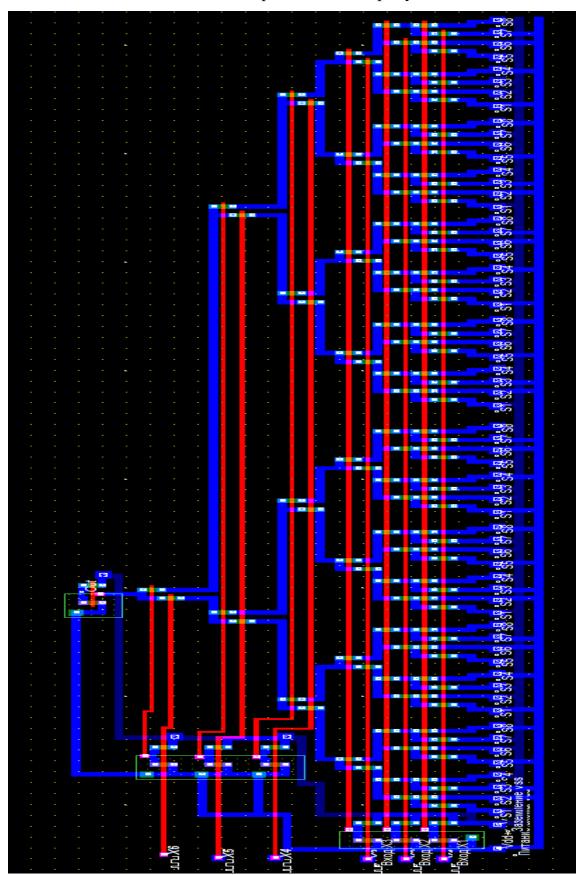

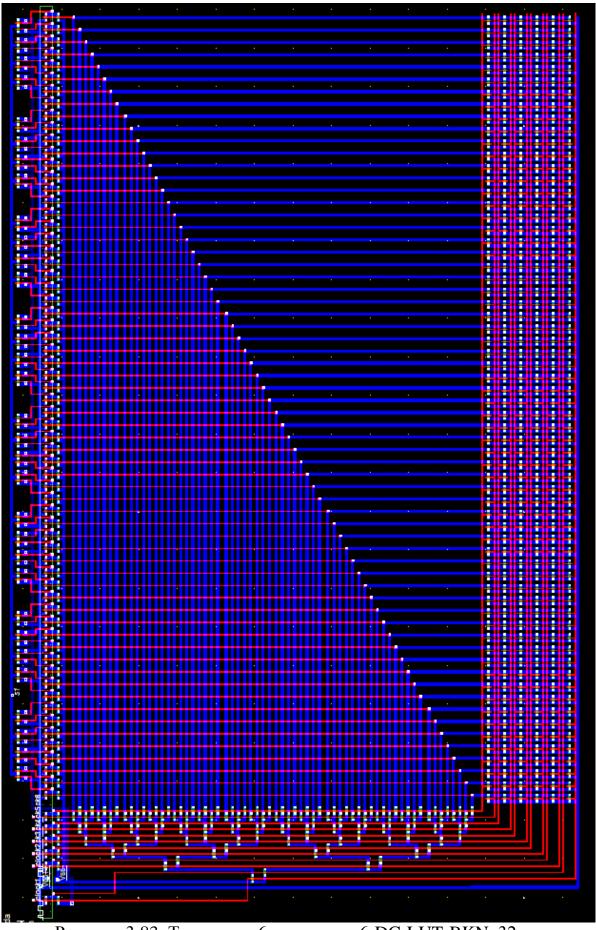

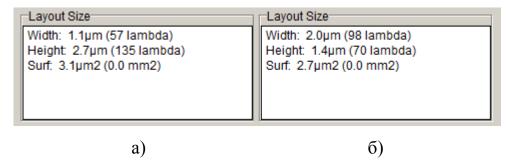

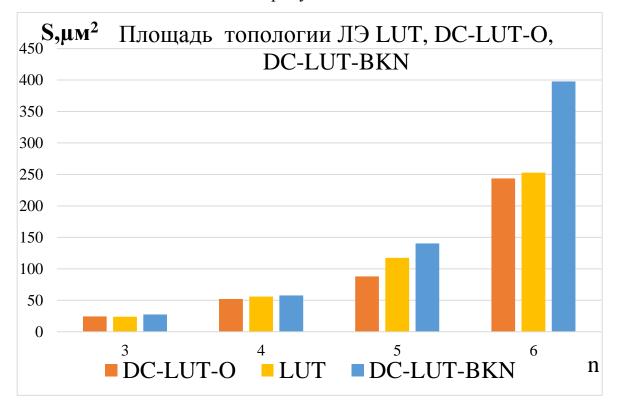

| 3.6.1.Топологическое моделирование ЛЭ LUT                    | 100            |

|--------------------------------------------------------------|----------------|

| 3.6.2. Топологическое моделирование логического элемента –   | DC-LUT-BKN     |

|                                                              | 106            |

| 3.6.3. Топологическое моделирование логического элемента     | a – DC-LUT-O   |

|                                                              |                |

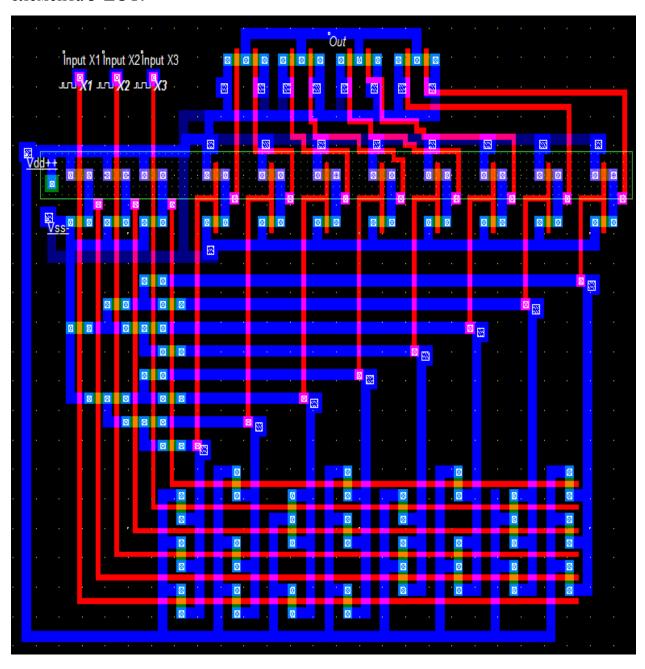

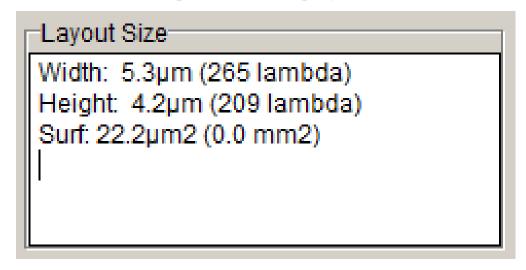

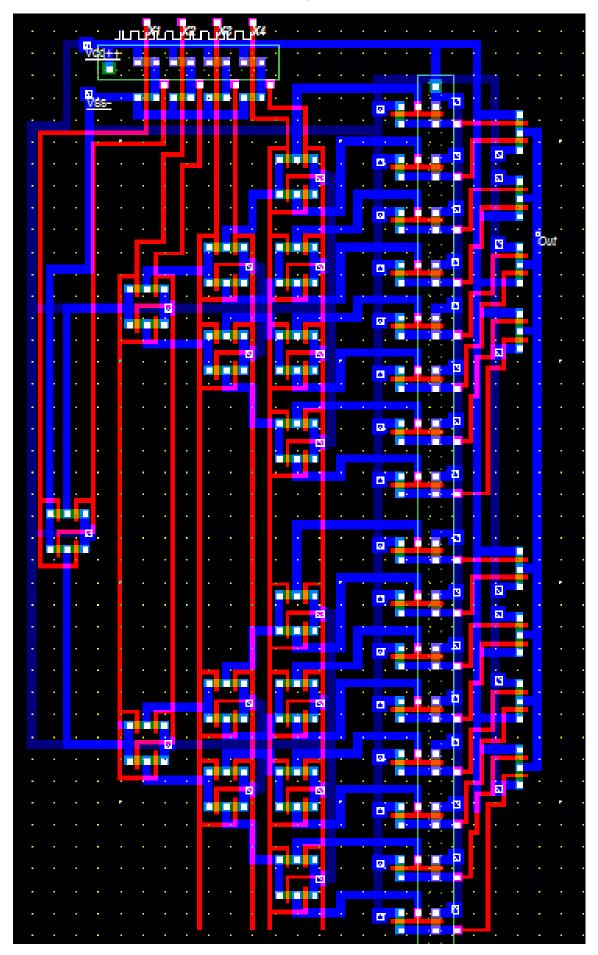

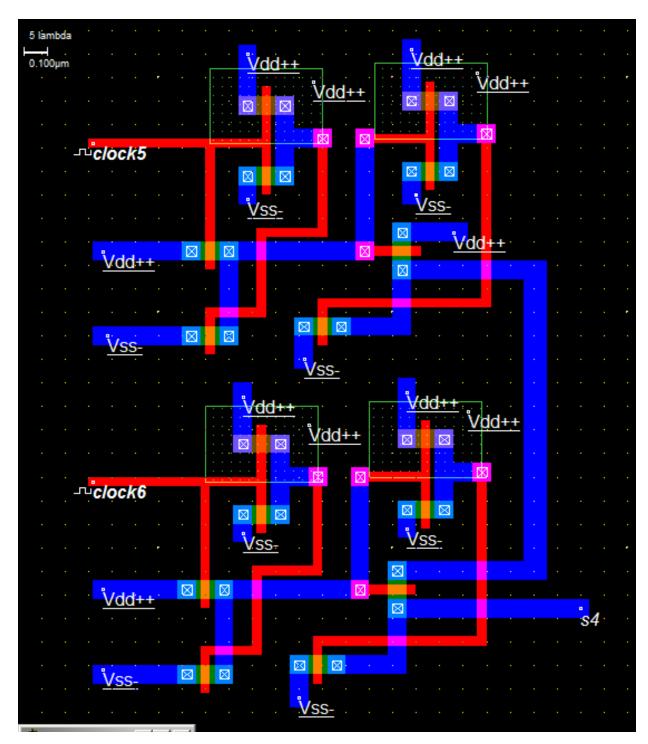

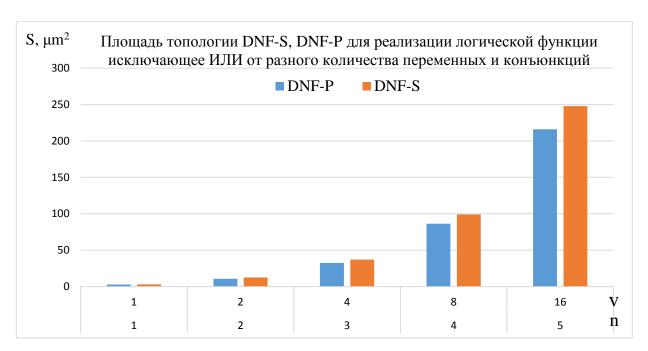

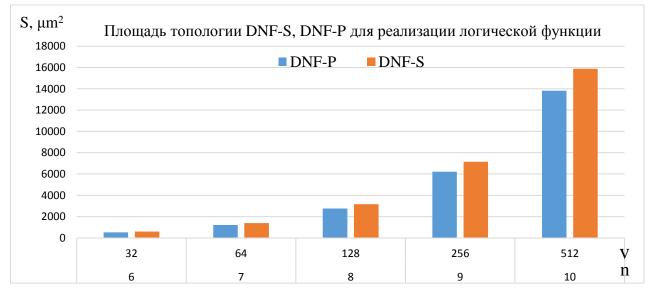

| 3.6.4. Топологическое моделирование логических элементов     |                |

| 3.6.5. Результаты топологического моделирования предложе     | енных ЛЭ DC-   |

| LUT-O, DC-LUT-BKN, DNF-LUT-S, DNF-LUT-P                      | 113            |

| 3.6.6. Топологическое моделирование логического элемента     | ADC-LUT . 116  |

| 3.7. Выводы по главе 3                                       | 119            |

| Глава 4. Оценка технической эффективности усовершенствова    | анных методов  |

| реализации в FPGA систем логических функций и выбор оптима   | ального набора |

| логических элементов                                         | 122            |

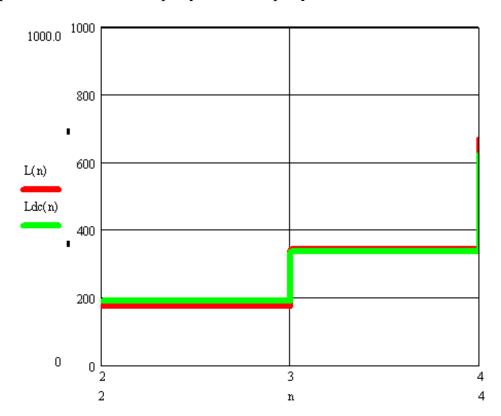

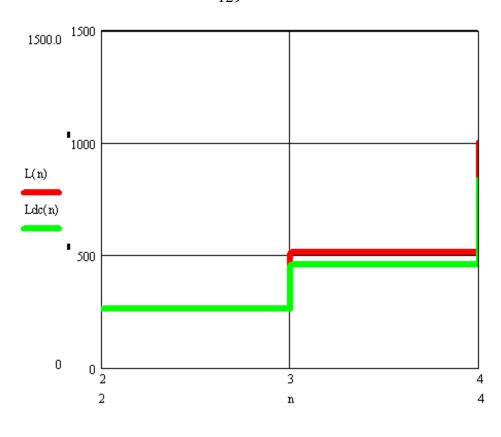

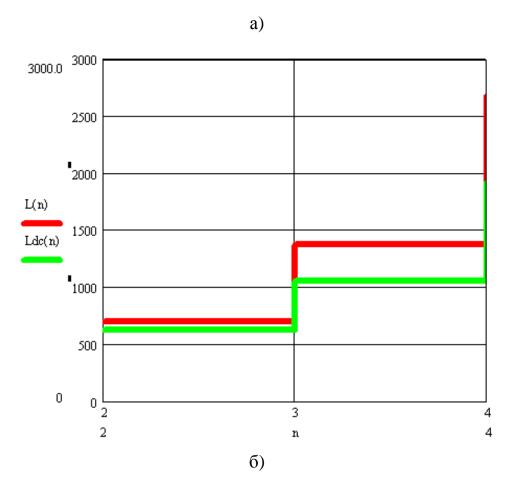

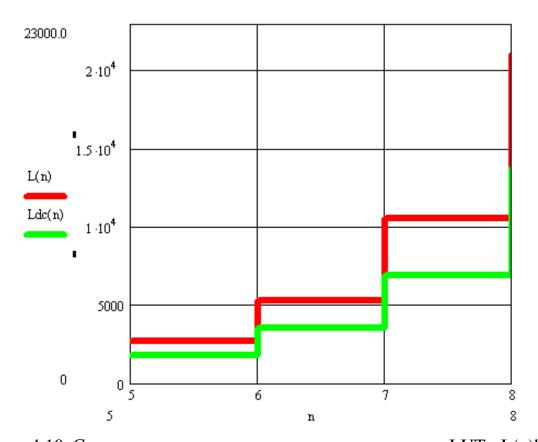

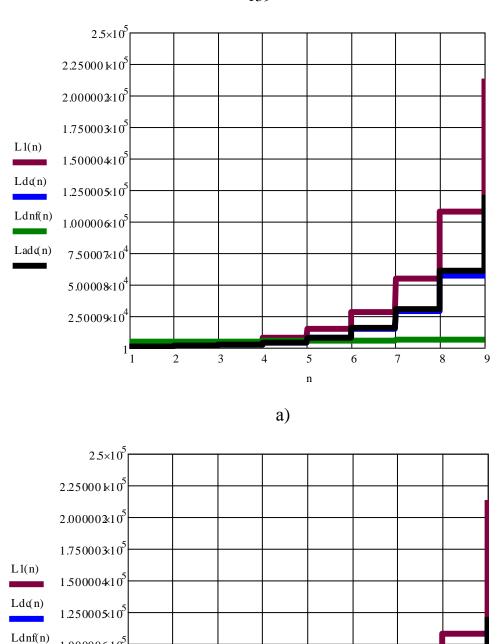

| 4.1. Исследование масштабирования разрядности LUT            | 122            |

| 4.2. Оценка сложности предлагаемых ЛЭ DC-LUT, ADC-LUT        | ПЛИС FPGA      |

|                                                              | 128            |

| 4.3. Оценка сложности предлагаемого DNF-LUT                  | 135            |

| 4.4. Разработка алгоритма выбора оптимального набора логичес | ских элементов |

| FPGA для реализации систем логических функций                | 141            |

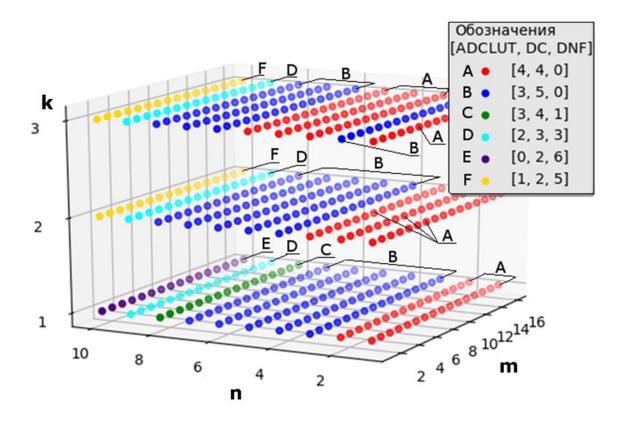

| 4.5. Выбор оптимального набора логических элементов FPGA д   | для реализации |

| систем функций                                               | 145            |

| 4.6. Выводы по главе 4                                       | 148            |

| Заключение                                                   | 149            |

| Список сокращений                                            | 151            |

| Список литературы                                            |                |

| Приложение А Программа оптимизации набора логическ           | их элементов   |

| модифицированным венгерским методом «ВЕННИТ»                 | 163            |

| П   | риложение                               | Б Дополнительные резу  | ультаты топологич | еского моделирования |

|-----|-----------------------------------------|------------------------|-------------------|----------------------|

| В   | системе                                 | автоматизированного    | проектирования    | специализированных   |

| (38 | аказных) иі                             | нтегральных схем Місго | Wind              | 172                  |

| Пр  | оиложение                               | В Акты внедрения резу  | льтатов диссертац | ионного исследования |

|     | • • • • • • • • • • • • • • • • • • • • |                        |                   | 178                  |

#### Введение

Актуальность темы исследования. В настоящее время для реализации цифровых элементов и устройств вычислительной техники и систем управления широко используются программируемые логические интегральные схемы (ПЛИС). Основой ПЛИС типа Field-Programmable Gate Array (FPGA) является логический элемент (ЛЭ) – генератор функций Look Up Table (LUT), число входных переменных которого увеличилось за 30 лет с 4-х до 8, а количество ЛЭ в ПЛИС – до десятка миллионов. Разработаны адаптивные логические модули (АЛМ), в которых разрядность ЛЭ может гибко изменяться под конкретный проект. Даже при наличии таких возможностей ПЛИС в ряде областей применения, количества ЛЭ может оказаться недостаточно, например, в системах управления летательных аппаратов в связи с возрастанием возложенных на них задач и наличия очень жестких масса-габаритных ограничений. Таким образом задача улучшения технических характеристик ЛЭ ПЛИС является актуальной. Одним из сдерживающих факторов является то, что существующие ЛЭ ПЛИС типа FPGA не ориентированы на реализацию систем функций, зависящих от переменных одного ЛЭ. Для данного конфигурационного файла логический элемент FPGA реализует только одну логическую функцию в совершенной дизъюнктивной нормальной форме (СДНФ). Реализация систем из т логических функций выполняется на т ЛЭ, то есть каждая логическая функция реализуется на отдельном LUT, что приводит к значительной избыточности при вычислении систем логических функций, зависящих от одних и тех же переменных, особенно, когда количество переменных достаточно велико. В то же время реализация систем функций в дизъюнктивной нормальной форме (ДНФ) используется в ПЛИС типа Complex Programmable Logic Device (CPLD). Оба подхода имеют свои плюсы и минусы, однако особенности комплексирования подходов FPGA и CPLD до конца не выявлены.

Таким образом, актуальным является проведение исследований в области создания методов и средств реализации систем логических функций в ЛЭ ПЛИС FPGA, особенно в связи с известными проблемами импортозамещения в отечественной электронной компонентной базе.

Степень разработанности темы исследования. Особенности логики ПЛИС рассмотрены в работах 3. Ерванта, Н. Мехта, А.В. Строгонова, С.А. Цыбина, А.Н. Денисова, В.И. Хаханова, В.С. Харченко, А.В. Дрозда, Г.П. Аксеновой, Д.Е. Иванова, Ю.А. Скобцова, М. Abusultan, S. P Khatri, М Тигі, Ј. Delgado-Frias, N. Jha. Новые логические элементы ПЛИС разрабатывались и исследовались в работах С.Ф. Тюрина, А.В. Грекова, О.А. Громова, А.Ю. Городилова, А.Н. Каменских. Однако эти работы не затрагивают реализацию систем логических функций в LUT FPGA. Созданием гибридной FPGA (Hybrid FPGA), которая по сути является совокупностью ЛЭ LUT и встроенных программируемых логических матриц (PLA, PAL), занимались исследователи Alireza Kaviani, Stephen Brown, Chi Wai Yu.

Однако в полной мере вопросы реализации систем логических функций при комплексировании подходов FPGA и CPLD до сих пор не решены.

Объектом исследования являются логические элементы ПЛИС.

**Предметом исследования** являются методы реализации систем логических функций в ПЛИС.

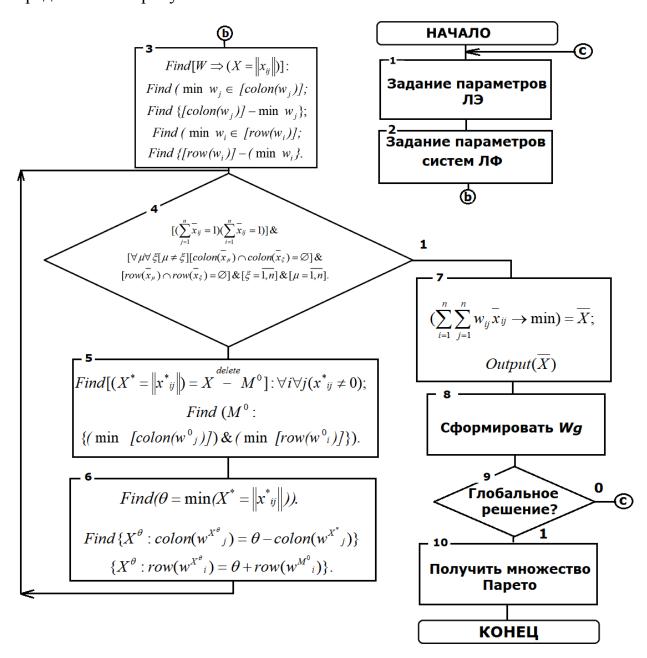

**Целью** диссертационного исследования является решение научной задачи выбора оптимального набора логических элементов для адаптивногибридной реализации систем логических функций в ПЛИС FPGA.

#### Основные задачи исследования:

- 1. Усовершенствовать метод реализации логических функций в СДНФ на основе соответствующего адаптивного логического элемента.

- 2. Усовершенствовать метод реализации логических функций в ДНФ.

- 3. Произвести оценку сложности реализации систем логических функций на основе разработанных логических элементов.

- 4. Разработать и исследовать модели предложенных логических элементов FPGA для реализации систем логических функций в типовых проектах на ПЛИС.

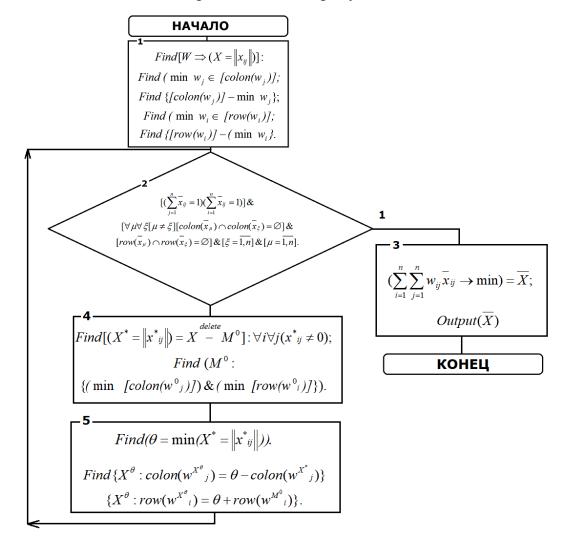

- 5. Разработать алгоритм оптимизации набора логических элементов ПЛИС FPGA для реализации систем логических функций в типовых проектах на ПЛИС.

Научная новизна диссертационной работы заключается в следующем:

- Предложен усовершенствованный метод реализации логических функций в СДНФ на основе соответствующего адаптивного логического элемента, отличающийся тем, что в зависимости от настройки возможна реализация либо стандартного логического элемента LUT, либо дешифратора для реализации систем логических функций.

- Предложен усовершенствованный метод реализации систем логических функций в ДНФ, отличающийся тем, что использовано оригинальное кодирование конъюнкций ДНФ, обеспечивающее формирование значения конъюнкции без использования подтягивающего резистора.

- Получены оценки сложности реализации систем логических функций на основе разработанных логических элементов, отличающиеся декомпозицией, учитывающей ограничения Мида-Конвей на число последовательно соединенных передающих транзисторов.

- Выполнена оптимизация набора логических элементов ПЛИС FPGA на основе комбинирования ЛЭ, вычисляющих функции в СДНФ, и ЛЭ, вычисляющих функции в ДНФ, отличающаяся тем, что для этих целей модифицирован венгерский метод.

**Теоретическая значимость** диссертационной работы состоит в том, что развиты методы синтеза логических элементов, реализующих системы функций в ПЛИС. Разработаны и получены патентоспособные технические решения для реализации систем логических функций в ПЛИС типа FPGA,

полученные оценки сложности показывают предпочтительность их по аппаратным затратам по сравнению с существующими АЛМ.

Практическая значимость диссертационной работы состоит в том, что предложенные усовершенствованные методы позволили снизить аппаратные затраты на реализацию систем логических функций (акт Федерального исследовательского центра "Информатика и управление" Российской академии наук, акт Публичного акционерного общества «Пермская научнопроизводственная приборостроительная компания»).

Полученные научные и практические результаты используются в учебном процессе кафедры «Автоматика и телемеханика» Пермского национального исследовательского политехнического университета в рамках занятий профильных практических дисциплин «Электроника», «Проектирование дискретных устройств», «Схемотехника» у студентов направления 27.03.04 «Управление В технических системах» (акт Федерального государственного бюджетного образовательного учреждения высшего образования «Пермский национальный исследовательский политехнический университет»).

**Методология и методы исследования.** В диссертационной работе используются методы и средства схемотехнического и топологического моделирования, анализа и синтеза схем, структурное программирование. Применяемые методы и средства основаны на положениях дискретной математики, математической логики, теории булевых функций и автоматов, комбинаторики, теории надежности, принципах МОП-схемотехники.

**Область исследования,** обозначенная в сформулированных задачах, соответствует п. 3 «Разработка принципиально новых методов анализа и синтеза элементов и устройств вычислительной техники и систем управления с целью улучшения их технических характеристик» паспорта научной специальности 05.13.05.

### Основные положения, выносимые на защиту:

- 1. Усовершенствованный метод реализации логических функций в СДНФ на основе разработанного адаптивного логического элемента.

- 2. Усовершенствованный метод реализации логических функций в ДНФ.

- 3. Алгоритм оптимизации набора логических элементов ПЛИС FPGA для реализации типовых систем логических функций.

Степень достоверности результатов. Полученные в диссертационной работе результаты не противоречат теоретическим положениям, известным из научных публикаций отечественных и зарубежных исследователей, и подтверждаются результатами, полученными в двух системах моделирования, апробацией и внедрением предложенных в диссертации методов, моделей и алгоритма оптимизации.

Апробация результатов. Основные теоретические и практические результаты диссертационной работы докладывались на научно-технических конференциях: «Микроэлектроника и информатика», Зеленоград, 2015, 2017; ЛЭТИ - IEEE North West Russia Section Young Researchers in Electrical and Electronic Engineering Conference, EIConRusNW, Санкт-Петербург, 2016, 2018; 2-я Российско-белорусская научно-техническая конференция «Элементная база отечественной радиоэлектроники: импортозамещение и применение», Нижний Новгород, 2015; 14-я международная конференция «Авиация и космонавтика», Москва, 2015; форуме на международном «Микроэлектроника-2017» В рамках 3-й международной научной конференции «Электронная компонентная база и электронные модули», Республика Крым, г. Алушта, 2017; 14-я всероссийская школа-конференция молодых ученых «Управление большими системами УБС-2017», г. Пермь, **SEMIEXPO** 2017; международной выставке RUSSIA 2017; всероссийской научно-технической конференции «Автоматизированные системы управления и информационные технологии» г. Пермь, 2019; на семинарах в ИПИ РАН, ИПУ РАН, МИЭТ, ПНИПУ, других региональных и всероссийских конференциях; на международном конкурсе научнотехнических работ «Инновационная радиоэлектроника», 2017 г.

**Публикации.** Основные результаты диссертационной работы опубликованы в 21 печатной работе, из них 5 публикаций в ведущих рецензируемых научных изданиях, 2 публикации в изданиях, индексированных в международных базах цитирования Scopus и Web of Science, 3 патента на изобретение, 1 свидетельство о государственной регистрации программ для ЭВМ.

Структура и объем работы. Диссертационная работа состоит из введения, четырех глав, заключения, списка использованных источников и приложений. Содержит 180 страниц машинописного текста, из которых основной текст составляет 151 страницы, 152 рисунков и 6 таблиц, список литературы из 82 наименований, 3 приложений.

# Глава 1. Исследование методов и средств реализации систем логических функций в существующих ПЛИС. Постановка задачи исследования

# 1.1. Анализ существующих БИС программируемой логики

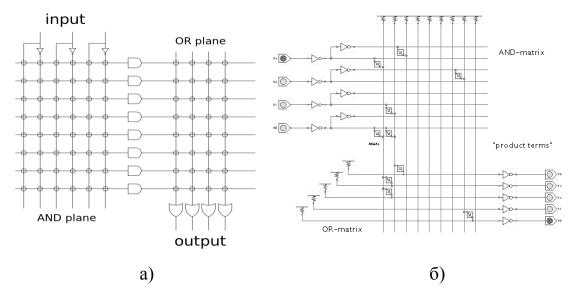

В начале 70-х годов XX века компания Texas Instruments (TI) выпустила первую ПЛМ - программируемую (с помощью маски – mask - programmable) логическую матрицу, содержащую матрицу И – для программирования конъюнкций и матрицу ИЛИ – для программирования дизъюнкций. С ПЛМ (PLA, programmable logic array) и началась эпоха ПЛИС. Структура ПЛМ [1,2] изображена на рисунке 1.1.

Рисунок 1.1. Структура ПЛМ, а) упрощённая; б) с детализацией коммутаций

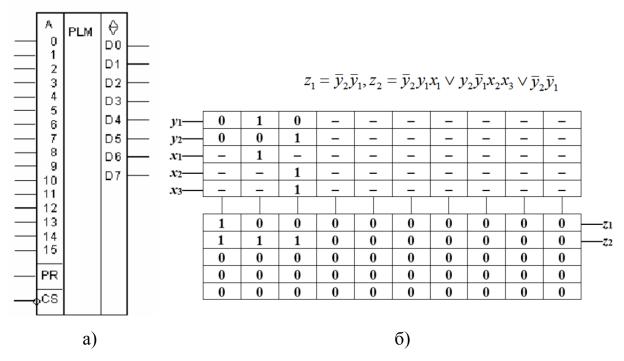

Как видно реализуется монтажная (проводная) логика — функции в дизъюнктивной нормальной форме — ДНФ. Программируются как матрица И, так и матрица ИЛИ. На рисунке 1.2 изображено условное графическое обозначение ПЛМ и пример программирования.

Структура другого типа программируемой логики — ПМЛ - программируемой матрицы логики (Programmable Array Logic - PAL) [3], где программируются только конъюнкции (Product terms) — матрица И, изображена на рисунке 1.3.

Рисунок 1.2. ПЛМ: а) Условное графическое обозначение ПЛМ; б) пример программирования

Рисунок 1.3. Структура ПМЛ, а) структура; б) упрощённая схемы реализации ДНФ; с) макроячейка

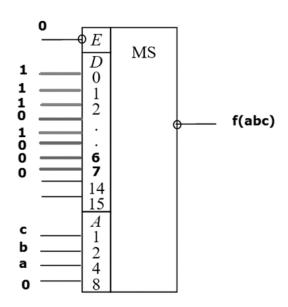

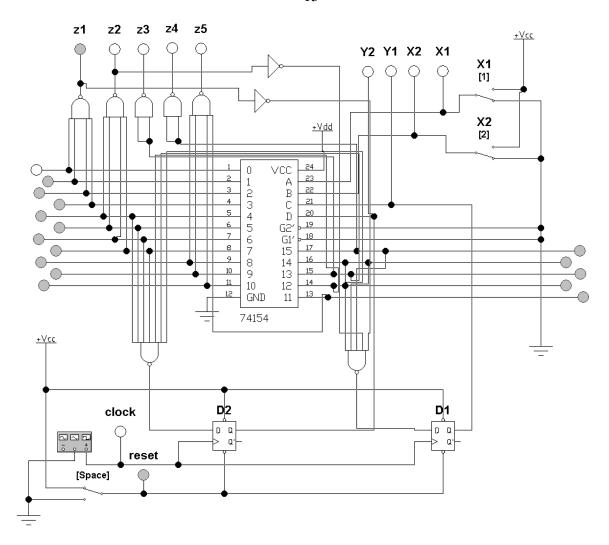

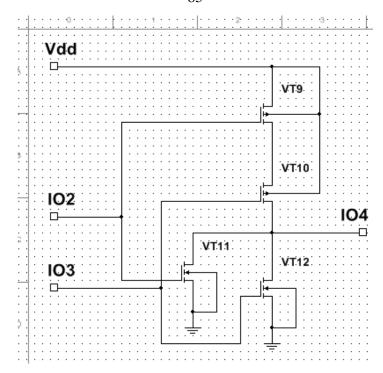

ПЛМ и ПМЛ реализуют системы логических функций в ДНФ [4,5,6]. Другой вариант реализации логики – использование оперативной (ОЗУ) или постоянной памяти (ПЗУ) для записи таблицы истинности функции. В этом случае реализуется совершенная дизъюнктивная нормальная форма – СДНФ [6-8]. Так, например, для реализации мажоритарной функции (функции переноса) на ИМС средней степени интеграции-мультиплексоре[7,8], входы данных, соответствующие наборам 3,5,6,7 логической функции, зависящей от переменных а,b,с подключаются к константе 0 (так как выход мультиплексора инверсный), а входы 0,1,2,4 – к константе 1 – рисунок 1.4.

Рисунок 1.4. Структура однобитного мультиплексора логической функции не более, чем 4-х переменных

В принципе рисунок 1.4 - это однобитное ПЗУ. Для реализации большего числа функций можно использовать несколько схем показанных на рисунке 1.4 и получим многобитное ПЗУ. В этом случае на каждую функцию необходим один мультиплексор. Для реализации многобитной памяти используют дешифратор (DC) и элементы 2-И-НЕ [7,8]. – рисунок 1.5.

В случае программирования элементов 2-И-НЕ получаем ОЗУ. Это так называемая «гибкая логика», так как пользователь имеет возможность сам определять необходимые ему функции.

Рисунок 1.5 Реализация семиразрядного четырехадресного ПЗУ на дешифраторе 74154

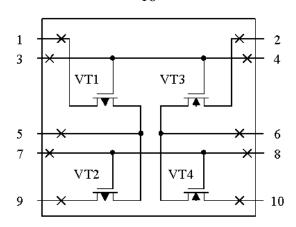

С 70-х годов XX развивалось и другое направление - базовые матричные кристаллы (вентильные матрицы- gate array, uncommitted logic array - ULA), у которых в заводских условиях программировались связи логических элементов, имеющиеся на заготовке [6]. Это были так называемые полузаказные БИС средней стоимости, в отличие от самых дорогих заказных (application-specific integrated circuits -ASICs), в которых вся архитектура создаётся «с нуля». Такие БМК, выпускает ТЦ МИЭТ (г.Зеленоград), для которых используется САПР «Ковчег» [9], библиотеки элементов, например, приведены в [10]. В БМК используют даже не сами логические элементы, а четырехтранзисторные ячейки (два транзистора р-проводимости, два п-проводимости) – рисунок 1.6.

Рисунок 1.6. Четырех транзисторная ячейка БМК

Из таких ячеек создаются типовые (библиотечные) элементы, а уже их можно использовать для синтеза цифровой аппаратуры. Примеры разработки новых элементов БМК представлены в диссертации Каменских А.Н. [11].

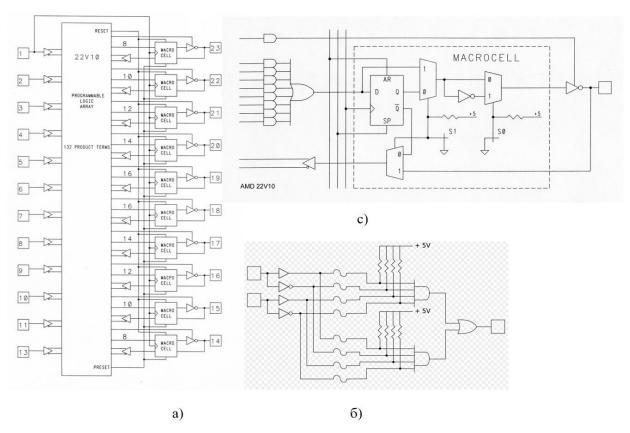

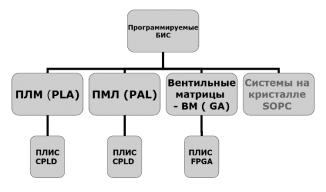

В конце 80-х годов XX века появились технологические возможности пользователю самостоятельно программировать связи элементов. Все эти принципы легли в основу более сложных ИМС программируемой логики - ПЛИС FPGA (ППВМ–программируемые пользователем вентильные матрицы) [6,12-16] и CPLD – (Complex Programmable Logic Device) [6]. Фактически логика CPLD изображена на рисунке 1.3.

Программируемая логика развивалась и во многом обеспечивала прогресс микропроцессорной техники, разработку однокристальных микроЭВМ, которые сейчас называются микроконтроллерами, обусловила и прогресс сигнальных процессоров. В XXI веке интегральная технология позволила разрабатывать целые программируемые системы на кристалле[6]. Классификация БИС [17] основных программируемых цифровых представлена на рисунке 1.7.

Рисунок 1.7. Классификация основных программируемых цифровых БИС

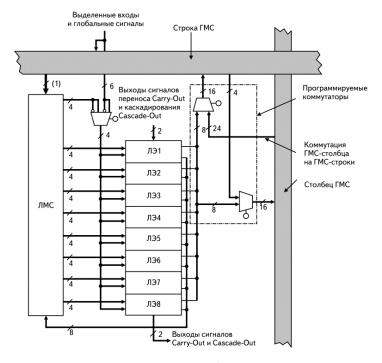

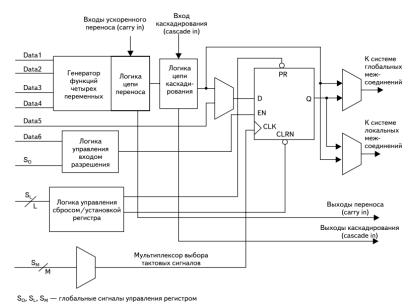

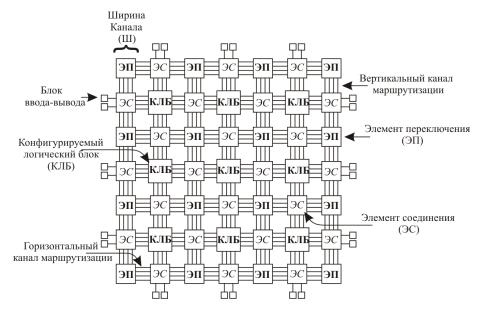

Архитектура конфигурируемого логического блока (КЛБ) ПЛИС FPGA [18-20] изображена на рисунке 1.8.

Рисунок 1.8. Архитектура типового конфигурируемого логического блока (КЛБ) ПЛИС FPGA

КЛБ содержит 8 логических элементов, которые, в свою очередь содержат следующие основные блоки: генератор функций четырех переменных — так называемый LUT (Look Up Table) и элемент памяти — D-триггер — рисунок 1.9.

Рисунок 1.9. Архитектура типового ЛЭ КЛБ

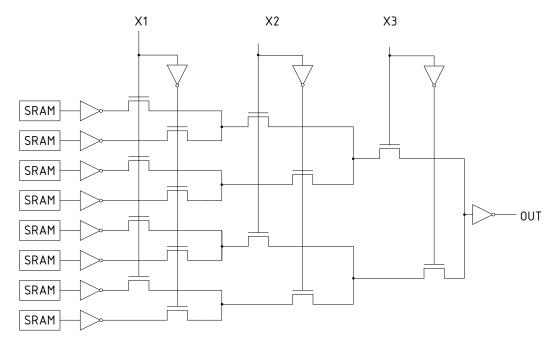

Генератор функций четырех переменных строится на основе двух генераторов функций трех переменных, LUT - на три переменных (3-LUT) имеет вид [18-20], показанный на рисунке 1.10:

Рисунок 1.10. Генератор функций трех переменных - LUT на три переменные (3-LUT)

Настройка логической функции  $z_{OUT}(x_3x_2x_1)$  определяется загрузкой конфигурационной оперативной памяти SRAM (a,b,c,d,e,f,g,h):

$$z_{OUT}(x_3x_2x_1) = \bar{ax_3x_2x_1} \vee \bar{bx_3x_2x_1} \vee \bar{cx_3x_2x_1} \vee \bar{cx_3x_2x_1} \vee \bar{dx_3x_2x_1} \vee \bar{ex_3x_2x_1} \vee fx_3\bar{x_2x_1} \vee fx_3\bar{x_2x_1} \vee gx_3x_2\bar{x_1} \vee hx_3x_2x_1.$$

(1.1)

Загружая необходимую настройку в ячейки SRAM, LUT реализует одну логическую функцию. Для реализации другой функции от этих же входных переменных необходимо либо загрузить новую настройку в ячейки памяти, либо задействовать дополнительный ЛЭ.

Более детальная структура генератора функций трех переменных - LUT на три переменные (3-LUT) с учётом D-триггера содержит двойные инверторы – буферы по входам переменных и восстановители по выходам LUT – рисунок 1.11.

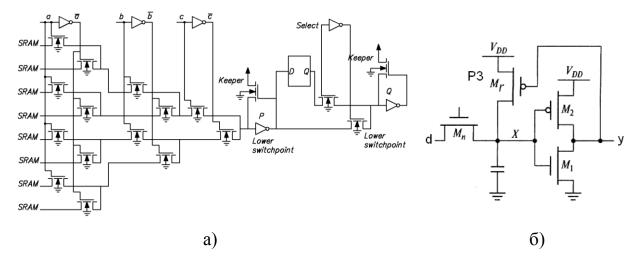

Архитектура маршрутизации ПЛИС (FPGA Routing Architecture) включает программируемые коммутаторы связей (Programmable Routing

Interconnect, локальные и глобальные матрицы связей) ЛЭ[18]. Такой коммутатор имеет вид показанный на рисунке 1.12.

Рисунок 1.11. 3-LUT: а) 3-LUT с двойными инверторами и триггером; б) восстановитель - буфер с запоминанием уровня

Рисунок 1.12. Программируемый коммутатор связей ПЛИС

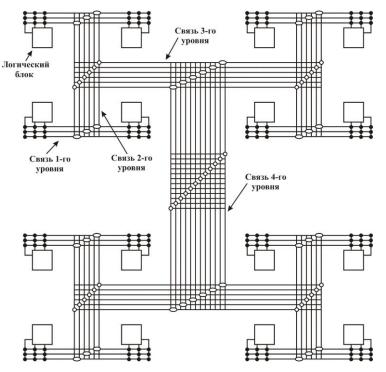

По типу архитектуры связей ПЛИС делятся на островные (island-style, mesh-based FPGA) и иерархические [19,20]. Пример островной ПЛИС (Altera Cyclone, Stratix) изображён на рисунке 1.13.

В островной ПЛИС все КЛБ «равны», в иерархических ПЛИС установлена иерархия связей, «ближние» КЛБ соединяются проще, чем «дальние» - рисунок 1.14.

Рисунок 1.13. Пример островной ПЛИС

Рисунок 1.14. Пример иерархической ПЛИС (Flex10K, APEX фирмы Altera (Intel))

По типу конфигурации памяти ПЛИС различают SRAM - based, Flash - based, Antifuse – based [19,20]. SRAM – based основаны на ячейках SRAM при этом после выключения питания программа, записанная в ячейки, стирается и существует необходимость при следующем включении питания заново записывать прошивку в ПЛИС. Для хранения конфигурации на ПЛИС устанавливают блок ПЗУ (Flash или другой энергонезависимой (Nonvolatile)

памяти), с которого осуществляется загрузка. Такая технология весьма уязвима при воздействии радиации [19,20].

Flash-based дороже SRAM-based, так как совмещение технологии (MOS) МОП и Flash весьма сложно, к тому же общее возможное число циклов перезаписи Flash значительно меньше, чем у SRAM –based.

Antifuse - based программируются однократно, как БМК, но зато она менее подвержена радиации.

## 1.2. Анализ адаптивных многоразрядных логических элементов FPGA

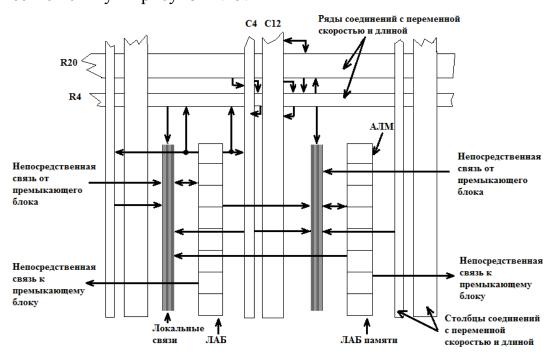

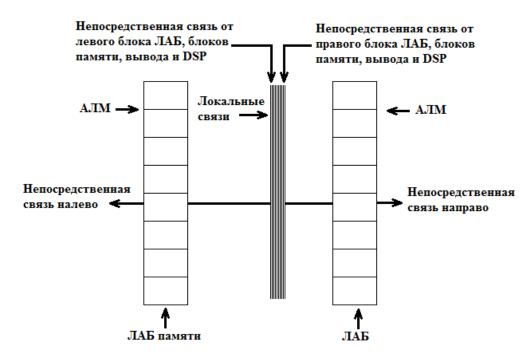

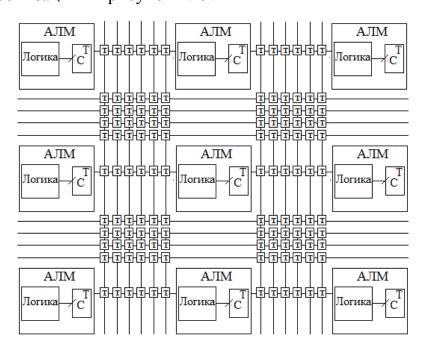

Если первые ПЛИС содержали сначала сотни ЛЭ, потом их уже были тысячи, десятки тысяч, сотни тысяч, то сейчас современные ПЛИС имеют миллионы ЛЭ, при этом общее количество транзисторов — несколько миллиардов [21-23]. Это уже не просто «гибкая логика», появилось понятие «Гиперфлекс» (The Intel HyperFlex FPGA Architecture). В ПЛИС реализуются уже конвейерные вычисления, «Гиперфлекс коммутация», «Гиперрегисты», «Гипероптимизация». Архитектура ПЛИС (например, Stratix III Altera (Intel)) включает целые «лаборатории» логики - блоки LAB (logic array block), они состоят из адаптивных логических модулей ALM (adaptive logic modules) в количестве 10 штук — рисунок 1.15:

Рисунок 1.15. Архитектура ПЛИС Stratix III

Имеются «лаборатории памяти» - Memory LAB (MLAB) - LAB, с возможной реконфигурацией в ОЗУ - рисунок 1.16:

| MLAB                                      |     | LAB               |

|-------------------------------------------|-----|-------------------|

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LAB Control Block                         |     | LAB Control Block |

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LUT-based-16 x 2<br>Simple dual port SRAM | (1) | ALM               |

| LUThered 40 C                             | (1) |                   |

Рисунок 1.16. Состав MLAB и LAB

Непосредственная связь через ALM реализуется следующим образом – рисунок 1.17:

Рисунок 1.17. АЛМ может «пропускать» сигнал через себя -direct link connection

Это позволяет создать эффективную трассировочную архитектуру ЛЭ - MultiTrack – рисунок 1.18.

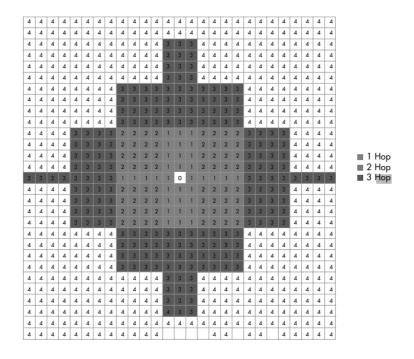

Рисунок 1.18. Трассировочная архитектура MultiTrack компании Altera (Intel), для элементарного шага используется термин hop (шаг).

В одной из последних разработок ПЛИС Intel Stratix 10 используется технология «Триггеры повсюду» [22], что обеспечивает конвейеризацию вычисления логических функций при соответствующей «гиперсинхронизации» – рисунок 1.19.

Рисунок 1.19 Технология «Триггеры повсюду»

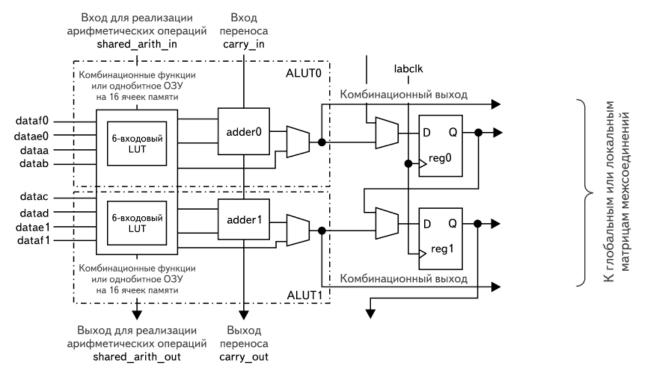

Рисунок 1.20. АЛМ ПЛИС Stratix III

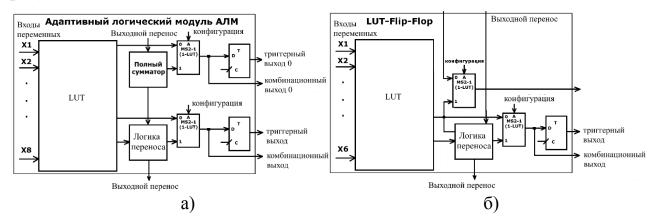

Архитектура АЛМ Stratix III [21,22] имеет вид – рисунок 1.20. Устройства, подобные АЛМ включаются и в ПЛИС фирмы Xilinx [23] - рисунок 1.21.

Рисунок 1.21. АЛМ: a) фирмы Altera (Intel): б) фирмы Xilinx

Хотя число входов АЛМ лежит в диапазоне 6-8 переменных, но детальный анализ показывает, что имеется фактически только 8 блоков 3-LUT (рисунок 1.22), то есть могут реализовать любые функции только 6 переменных.

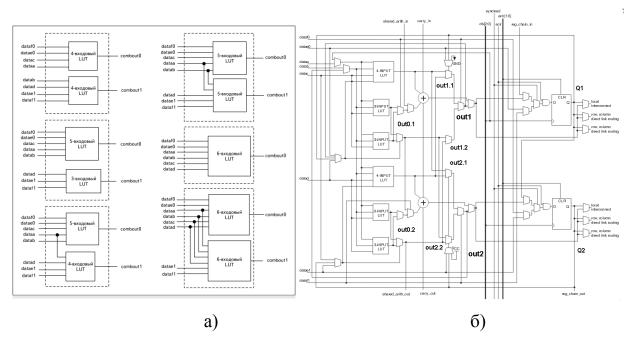

Рисунок 1.22. Архитектура АЛМ: а) упрощенная структура; б) детализация АЛМ

Реализация любых функций 7,8 переменных, то есть реализуются только некоторые функции, такие как:

$$\begin{array}{lll} 4LUT_{1.1} = [a \lor (clk)]; \\ 4LUT_{1.2} = [b \lor (out2)]; \\ 4LUT_{1.3} = c; \\ 4LUT_{1.4} = [e0 \lor (out1) \lor Q1 \lor d]. \\ \end{array} \\ 3LUT_{1.2} = 3LUT_{2.2} = 4LUT_{1.2}; \\ 3LUT_{1.3} = 3LUT_{2.3} = 4LUT_{1.3}. \\ 4LUT_{2.1} = 4LUT_{1.1} = [a \lor (clk)]; \\ 4LUT_{1.2} = 4LUT_{1.1} = [b \lor (out2)]; \\ 3LUT_{3.1} = 3LUT_{4.1} = 4LUT_{2.1}; \\ 3LUT_{3.2} = 3LUT_{4.2} = 4LUT_{2.2}; \\ 3LUT_{3.3} = 3LUT_{4.2} = 4LUT_{2.2}; \\ 3LUT_{3.3} = 3LUT_{4.3} = 4LUT_{2.3}. \\ \end{array} \\ \begin{array}{lll} 3LUT_{3.1} = 3LUT_{4.1} = 4LUT_{2.1}; \\ 3LUT_{3.2} = 3LUT_{4.2} = 4LUT_{2.2}; \\ 3LUT_{3.3} = 3LUT_{4.2} = 4LUT_{2.2}; \\ 3LUT_{3.3} = 3LUT_{4.3} = 4LUT_{2.3}. \\ \end{array}$$

# 1.3. Анализ научно-методического аппарата оптимизации логики ПЛИС

Анализ научно-технических источников показывает, что «оптимизация» программируемой логики заключается в основном в «правильном» размещении проекта в ПЛИС [24]. Эти возможности имеются в САПР: Quartus II (Altera (Intel)), ISE Suite, Vivaldo Design Suite (Xilinx), Libero IDE, Libero SoC (Microsemi). Выделяются ключевые параметры: потребляемая мощность, размер проекта и его быстродействие. Например, для уменьшения размера проекта в САПР Xilinx: Project -> Design Goals & Strategies, Area Reduction [25].

В САПР Quartus II фирмы Altera (Intel) можно минимизировать память автомата (State Machine) – установить вместо унитарного кодирования (Onehot) минимальное – (Minimal Bits), имеются опции анализа энергопотребления power analysis.

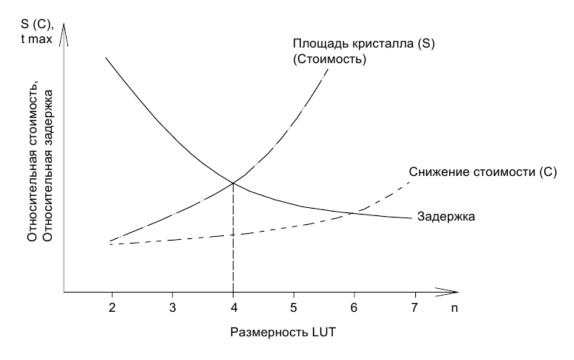

Работ, посвященных оптимизации при проектировании самой ПЛИС немного. В [26] описываются ALM и исследуется требуемая для них размерность логического элемента (генератора логических функций) LUT FPGA. Наиболее предпочтительным по задержке с учетом площади кристалла в качестве базового устанавливается 4-LUT [21,26] – рисунок 1.23.

Рисунок 1.23. Оптимизация разрядности LUT

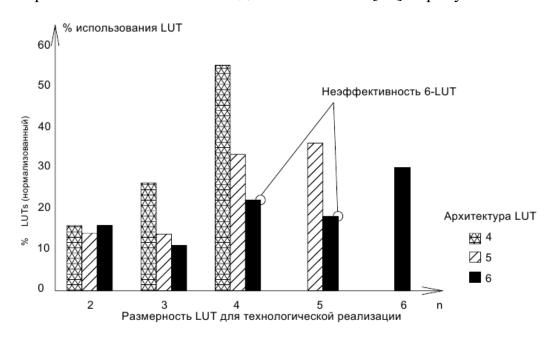

Причём процент использования LUT разной разрядности показывает целесообразность использования адаптивных LUT [26] – рисунок 1.24.

Рисунок 1.24. Распределение потребности в LUT по результатам синтеза

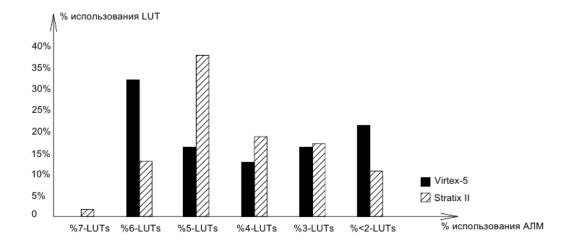

Такое распределение различается у разных производителей, использующих разные САПР [26] – рисунок 1.25.

Рисунок 1.25. Распределение потребности в LUT

Кроме того, выполняется сравнительный анализ гибкости логики различных производителей, очевидно в рекламных целях [26] – рисунки 1.26, 1.27.

| АЛМ       | 1 Stratix III | LUT Vietov F | Минимальное число |

|-----------|---------------|--------------|-------------------|

| Выход 1   | Выход 2       | LUT Virtex-5 | общих входов АЛМ  |

| 5-BX. LUT | 5-Bx. LUT     | 5            | 2                 |

| 5-вх. LUT | 4-BX. LUT     | 4            | 1                 |

| 5-BX. LUT | 3-BX. LUT     | 2            |                   |

| 4-BX. LUT | 4-Bx. LUT     | 3            |                   |

| 4-вх. LUT | 2 py IIIT     | 2            | 0                 |

| 3-BX. LUT | 3-Bx. LUT     | 1            |                   |

Рисунок 1.26. Сравнение гибкости логических элементов FPGA Stratix III и Virtex-5

| Число | Число достиж         | Число достижимых LAB/CLB |             | ижимых ЛЭ | Отношение числа ЛЭ        |  |

|-------|----------------------|--------------------------|-------------|-----------|---------------------------|--|

| шагов | Stratix III Virtex-5 |                          | Stratix III | Virtex-5  | Stratix III к ЛЭ Virtex-5 |  |

| 1     | 34                   | 12                       | 850         | 132       | 6,4                       |  |

| 2     | 96                   | 96                       | 2400        | 1056      | 2,3                       |  |

| 3     | 160                  | 180                      | 4000        | 1980      | 2,0                       |  |

| Bcero | 290                  | 288                      | 7250        | 3168      | 2,3                       |  |

Рисунок 1.27. Сравнение возможностей межсоединений FPGA Stratix III и Virtex-5

Так, АЛМ компании Altera (Интел) способен реализовать две независимые 4-входовые функции (без общих входов), тогда как LUT Virtex-5 требует использования трех общих входов [21].

Имеются работы исследователей из университета Торонто по созданию комбинированной ПЛИС FPGA-CPLD в плане использования ПМЛ (PAL), что, как утверждается, уменьшает площадь кристалла вдвое [27,28] – рисунок 1.28.

| ВМ      | 4-LUT<br>(area) | HFA<br>(area) | PALBs | 4-LUTs | Area<br>gain |

|---------|-----------------|---------------|-------|--------|--------------|

| 5xp1    | 78              | 28            | 4     | 12     | 2.8          |

| 9sym    | 172             | 69            | 11    | 25     | 2.5          |

| count   | 55              | 39            | 8     | 7      | 1.4          |

| C499    | 74              | 74            | 0     | 74     | 1            |

| 9symml  | 159             | 58            | 9     | 22     | 2.7          |

| misex1  | 21              | 16            | 3     | 4      | 1.3          |

| s298    | 1970            | 271           | 62    | 23     | 7.3          |

| z4ml    | 18              | 10            | 1     | 6      | 1.8          |

| vg2     | 69              | 32            | 4     | 16     | 2.2          |

| alu2    | 213             | 105           | 14    | 49     | 2            |

| Average | <u> </u>        | •             |       |        | 2.5          |

| Total:  | 2829            | 702           | 116   | 238    | 4            |

Рисунок 1.28. Оценка комбинированного подхода ПЛИС FPGA-CPLD - Hybrid FPGA Architecture (HFA)

Здесь количество конъюнкций (Product terms), так и входов исследуемых функций оценивается от 1 до 50. Оценивается работа ПЛИС FPGA на частоте 10 до 50 МГц, в то же время CPLD - 100 МГц. Используется случайный синтез схем (Benchmark Circuit – BenchMark - BM) и три статистических параметра: 1) среднее число входов, 2) среднее число конъюнкций (Pterms), 3) отношение количества входов к числу Pterms для каждого комбинационного узла. На рисунке 1.29 приведены значения и дисперсия этих параметров [27,28].

| Параметр<br>случайного<br>синтеза | Входы<br>(μ, σ) | Среднее<br>число<br>конъюнкц<br>ий<br>(µ, σ) | Входы /<br>Среднее<br>число<br>конъюнкц<br>ий<br>(µ, σ) | Среднее число конъюнкций (отфильтрова но) (µ, σ) | Входы / Среднее число конъюнкций (отфильтрован о) (µ, σ) |

|-----------------------------------|-----------------|----------------------------------------------|---------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------|

| K=6                               | 12.5, 6.56      | 9.32, 7.29                                   | 1.55, 1.02                                              | 6.64, 7.48                                       | 1.81, 1.32                                               |

| K=5                               | 11.57, 6.48     | 8.47, 7.08                                   | 1.61, 1.01                                              | 6.25, 7                                          | 1.77, 1.21                                               |

| K=4                               | 10.04, 6.32     | 7.23, 6.62                                   | 1.68, 1.03                                              | 5.53, 6.3                                        | 1.7, 1.07                                                |

| K=3                               | 8.59, 6.09      | 6.02, 6.17                                   | 1.78, 1.01                                              | 4.89, 5.62                                       | 1.62, 0.94                                               |

| K=2                               | 6.35, 5.45      | 4.36, 5.21                                   | 1.83, 0.94                                              | 3.77, 4.58                                       | 1.5, 0.76                                                |

| K=1                               | 4.54, 4.69      | 3.12, 4.26                                   | 1.74, 0.79                                              | 2.96, 3.65                                       | 1.29, 0.66                                               |

| K=0                               | 4.46, 4.66      | 3.07, 4.22                                   | 1.72, 0.79                                              | 2.91, 3.62                                       | 1.29, 0.66                                               |

Рисунок 1.29. Оценка параметров комбинационных схем методом случайного синтеза

Оценка энергопотребления и задержки единичного LUT дана, например, в [29] в связи со сравнением технологии MOS LUT с технологией CNTFET LUT (Carbon nanotube field-effect transistor) – рисунок 1.30.

| Vdd  | CMOS LUT<br>power(nW) | CNFET LUT<br>power(nW) |

|------|-----------------------|------------------------|

| 0.2  | 10.4                  | 0.5                    |

| 0.25 | 17                    | 0.75                   |

| 0.3  | 27.7                  | 0.69                   |

| 0.35 | 43.5                  | 1.04                   |

| 0.4  | 68.6                  | 1.34                   |

| Vdd  | CMOS LUT<br>delay(ns) | CNFET LUT<br>delay(ns) |

|------|-----------------------|------------------------|

| 0.2  | 201                   | 2.02                   |

| 0.25 | 92                    | 0.9                    |

| 0.3  | 51.1                  | 0.54                   |

| 0.35 | 30.5                  | 0.19                   |

| 0.4  | 20                    | 0.086                  |

a) 6)

Рисунок 1.30. Оценка MOS LUT при сравнении с технологией CNTFET LUT: а) потребляемая мощность; б) задержка

### 1.4. Постановка задачи исследования

Анализ объекта исследования [15-23] позволил установить востребованную тенденцию усложнения логических элементов ПЛИС и создания адаптивных логических модулей с увеличением числа переменных реализуемых логических функций на основе варьирования ЛЭ 3-LUT,4-LUT.

Анализ предмета исследования [30-45] показал, что дальнейшее увеличение числа переменных с целью повышения быстродействия LUT наталкивается на экспоненциальный рост сложности СДНФ, при этом подход реализации систем функций в ДНФ рассматривается только в контексте CPLD [23-29]. Совершенствование логики ПЛИС в РФ особенно актуально в связи с известными проблемами импортозамещения электронной компонентной базы [46-50]. Поэтому предлагается исследовать возможность модификации существующего адаптивного логического модуля — АЛМ в направлении реализации систем функций с возможной реализацией их в ДНФ.

Формальная постановка задачи следующая:

**Дано:** архитектура существующих ЛЭ и адаптивного логического модуля – АЛМ на их основе, множество элементов АЛМ:  $\overset{e}{\underset{i=1}{\cup}} \Psi_i$ , их количество:

$\sum_{i=1}^{e} \!\! \left| \Psi_i \right|$  , значения сложности существующих логических элементов FPGA и

СРLD L -  $\sum_{i=1}^{e} \sum_{\xi=1}^{|\Psi_{\xi}|} L(n,m,v,k,r)_{i\xi}$  , энергопотребления (потребляемой мощности)

$E-\sum_{i=1}^{e}\sum_{\mu=1}^{|\Psi_{\mu}|}E(n,m,v,k,r)_{i\mu}$  и максимальной задержки  $\max au_{\Psi_{i}}$  относительно максимального количества п переменных, т функций, у конъюнкций в реализуемых логических функциях, а также k декомпозиции дерева транзисторов, г ограничения Мида-Конвей на число последовательно включенных передающих транзисторов (Pass Transistors).

Требуется: 1. Усовершенствовать методы реализации существующих АЛМ путём комплексирования подходов к реализации логики в FPGA и CPLD, и создания гибридного АЛМ - АЛМ\*. Выбрать оптимальный набор логических элементов для реализации систем логических функций в АЛМ\*, для чего:

- 2. Получить для АЛМ\*:  $\bigcup_{j=1}^{q} \Psi_{i}^{*}$  множество новых элементов на основе усовершенствованных методов реализации систем логических функций.

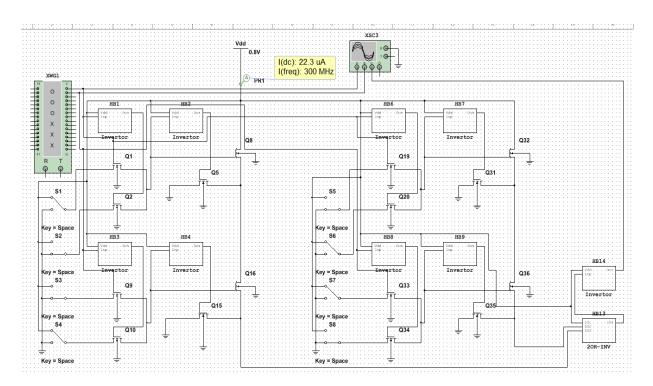

- 3. Для сравнения их между собой и с существующими элементами с целью выбора наиболее предпочтительных вариантов  $\bigcup_{j=1}^q \Psi_i^*$  \* выполнить моделирование в среде Multisim и Microwind с оценкой площади топологии S, энергопотребления E и максимальной задержки  $\max \tau_{\Psi_i}$ .

- 4. Относительно полученных вариантов  $\bigcup_{j=1}^{q} \Psi_{i}^{*}$  \* осуществить оптимизацию (минимизацию) по количеству транзисторов и площади S на основе получения их оценок сложности  $L_{s}^{*}(n,m,v,k,r)_{jy}$  и модифицирования венгерского метода (алгоритма) с целью получения оптимального набора (вектора) элементов  $z_{1}z_{2}....z_{\pi}$ :

$$\{z_1 z_2 .... z_{\pi}\}(n, m, v, k, r); z_{\lambda} = \sum_{\sigma=1}^{\nu} \psi_{\sigma}; \psi_{\sigma} \in \Psi_i^*; \nu \le j; \sum_{\kappa=1}^{\pi} z = \sum_{i=1}^{e} |\Psi_i|$$

(1.3)

для заданного набора параметров n, m, v, k, r:

$$L_{s(z_1 z_2 \dots z_n)}(n, m, v, k, r) \rightarrow \min.$$

(1.4)

5. С использованием полученных наборов  $\{z_1z_2....z_\pi\}(n,m,v,k,r)$  определить множество Парето, учитывающее полученные в результате моделирования оценки площади топологии, энергопотребления и задержки и их аппроксимацию для реальных значений параметров систем логических функций.

В результате получить требуемое количество новых элементов в одном АЛМ\*:  $\sum_{j=1}^{q} |\Psi_{j}^{*}|$  \* так, чтобы с меньшими затратами в количестве транзисторов и площади топологии реализовать заданные системы логических функций

$$\sum_{i=1}^{q} \sum_{r=1}^{|\Psi^*_{\gamma}|} L_s^*(n, m, v, k, r)_{j\gamma} << \sum_{i=1}^{e} \sum_{\xi=1}^{|\Psi_{\xi}|} L_s(n, m, v, k, r)_{i\xi};$$

(1.5)

при этом не ухудшая энергопотребление и задержку:

$$\sum_{j=1}^{q} \sum_{\gamma=1}^{|\Psi^*_{\gamma}|} E(n, m, v, k, r)_{j\gamma} \leq \sum_{i=1}^{e} \sum_{\xi=1}^{|\Psi_{\xi}|} E(n, m, v, k, r)_{i\xi};$$

$$\forall \tau_{\Psi^*_{i}} \forall \tau_{\Psi_{i}} (\max \tau_{\Psi^*_{i}} \leq \max \tau_{\Psi_{i}}).$$

$$(1.6)$$

#### 1.5. Выводы по главе 1

В главе представлены следующие основные результаты:

1. Выполнен анализ существующих БИС программируемой логики, который показал, что в настоящее время используются ПЛИС с логическими элементами, имеющими число переменных n=4,5,6. Дальнейшее увеличение числа переменных с целью повышения быстродействия LUT затруднительно в связи с экспоненциальным ростом сложности. Принцип программирования существующих ЛЭ ориентирован на раздельную реализацию логических функции в СДНФ, что делает невозможным реализацию систем функций или одновременное выполнение нескольких функций на одном ЛЭ относительно одних входных переменных. Для реализации систем функций приходиться

задействовать дополнительные ЛЭ, что ведет к дополнительным затратам площади кристалла.

- 2. Выполнен анализ адаптивных многоразрядных ЛЭ FPGA. В адаптивных логических модулях имеется возможность изменения размерности логического элемента до 7,8, но при этом реализуются не все возможные функции. Имеется большое количество публикаций посвященных комбинированию технологий различных типов ПЛИС, но нет исследований, посвященных реализации в FPGA систем логических функций от большого числа переменных, в том числе в ДНФ, с выбором оптимальных параметров для реализации типовых проектов. Реализации систем функций в ДНФ рассматривается только в контексте СРLD.

- 3. Выполнен анализ научно-методического аппарата оптимизации логики ПЛИС, который позволил выявить ключевые параметры такие, как энергопотребление, сложность, задержка. Существующие методы оптимизации программируемой логики в основном направлены на оптимальное размещение проекта в ПЛИС, не затрагивая самой структуры ПЛИС и ЛЭ.

- 4. Выполненный анализ показывает актуальность проведения исследований в области создания методов и средств реализации систем логических функций ПЛИС FPGA, так как особенности комплексирования подходов FPGA и CPLD не решены.

# Глава 2. Разработка усовершенствованных методов реализации в FPGA систем логических функций

# 2.1. Усовершенствованный метод реализации в FPGA систем логических функций, заданных в СДНФ

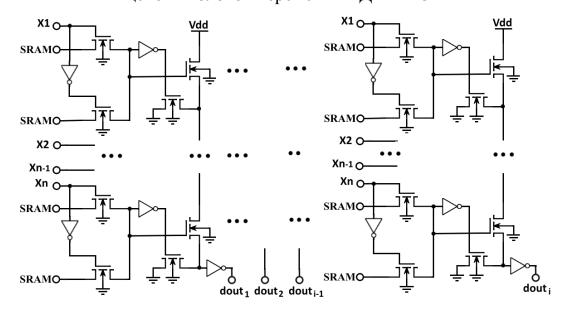

Для реализации системы из m логических функций в существующих ПЛИС FPGA используются m деревьев передающих транзисторов [51,52], которые могут быть выражены следующим образом:

$$z_{out} = \bigvee_{i=1}^{2^{n}} \left( \bigotimes_{j=1}^{n} x_{j}^{\sigma(i-1,j)} \cdot d_{i} \right), \tag{2.1}$$

где  $\sigma(i,j)$  - показатель инверсирования переменной в соответствующей ветви дерева передающих транзисторов, его значение противоположно значению j-го разряда в двоичной записи числа  $i, d_i \in \{0,1\}$  — настройка, значение i-й конфигурационной ячейки SRAM.

Выражение (2.1) реализует п-уровневое дерево передающих транзисторов. Представим его следующим образом:

$$x_{n} \leftarrow \frac{\bar{x}_{n-1} \leftarrow \bar{x}_{n-2} \leftarrow \bar{x}_{1} \cdot d_{0}}{x_{n-2} \leftarrow \bar{x}_{1} \cdot d_{0}} \\

x_{n-1} \leftarrow \bar{x}_{n-2} \leftarrow \bar{x}_{1} \cdot d_{1}$$

$$z_{out} (x_{n} x_{n-1} \dots x_{2} x_{1}) = \vee \bullet \qquad - \sum_{\substack{x_{n-1} \leftarrow \bar{x}_{n-2} \leftarrow \\ x_{n-1} \leftarrow \bar{x}_{n-2} \leftarrow \\ x_{n-2} \leftarrow \bar{x}_{1} \cdot d_{2} = -2}}, \qquad (2.1)$$

где ∨•-корень дерева, монтажное ИЛИ (wired OR).

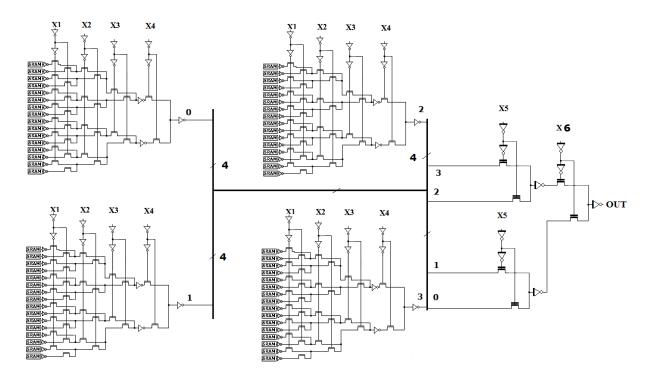

Предлагается реализация систем логических функций в СДНФ на основе DC LUT (DC-дешифратор, обратное дерево) [53-61]:

$$d_{out.i} = \mathop{\&}_{i=1}^{n} (x_j^{\sigma(i-1,j)}); i = 1,2^n,$$

(2.2)

где  $d_{out.i}$  - выход i-ой ветви дерева «наоборот», соответствующий истинности i-ой конъюнкции из  $2^n$  конъюнкций n переменных.

$$x_{n} \xrightarrow{\overline{x_{n-1}}} \xrightarrow{\overline{x_{n-2}}} \xrightarrow{\overline{x_{1}}} \xrightarrow{x_{1}} \xrightarrow{d_{out} 0} \\

x_{n} \xrightarrow{\overline{x_{n-2}}} \xrightarrow{\overline{x_{n-2}}} \\

x_{n-1} \xrightarrow{\overline{x_{n-2}}} \xrightarrow{\overline{x_{n-2}}} \\

x_{n-1} \xrightarrow{\overline{x_{n-2}}} \xrightarrow{\overline{x_{n-2}}} \\

x_{n-1} \xrightarrow{\overline{x_{n-2}}} \xrightarrow{\overline{x_{1}}} \xrightarrow{d_{out} 2^{n} - 2} \\

x_{n-2} \xrightarrow{x_{n-2}} \xrightarrow{x_{1} \xrightarrow{d_{out} 2^{n} - 2}} \xrightarrow{d_{out} 2^{n} - 2} (2.3)$$

где  $d_{in} \in 0,1$  определяет активный уровень при реализации соответствующей цепочки в обратном дереве.

Программирование значений т логических функций z осуществляется следующим образом:

$$z_{l} = \bigvee_{i=1}^{2^{n}} (d_{out,i} \cdot h_{l,i}); l = 1, m,$$

(2.4)

где h — настройка вхождения конституент i в данную функцию из m функций системы.

Рассмотрим подробно простейший LUT на одну переменную X (1-LUT) логическую функцию которого, можно выразить следующим образом:

$$\overline{z}_{out} = d_0 \cdot \overline{x} \vee d_1 \cdot \overline{x}. \tag{2.5}$$

Причём двойная инверсия по входу Х необходима для усиления сигнала, поступающего с матриц локальных и/или глобальных коммутаций. В дальнейшем будем указывать только один инвертор для получения сигнала не X. На выходе LUT устанавливается инвертор (буфер) для этих же целей, поэтому выходной сигнал (функция) инверсный. На входе настройки также имеются инверторы, а настройка (конфигурационные биты) также инверсна. Поэтому, получим:

$$z_{out} = d_0 \cdot x \vee d_1 \cdot x. \tag{2.6}$$

В дереве передающих транзисторов, реализующих (2.4) в зависимости от сигнала X на входе инвертора функции, сигналы всегда ортогональны, то есть со входов настройки всегда подаётся либо 0, либо 1 и нет ситуации, когда оба передающих транзистора по X и не X не активированы. Выполним реверс (2.4) для дешифрации входного набора:

$$\overline{d}_{i} = \underset{j=1}{\overset{n}{\&}} x_{j}^{\sigma(i-1,j)} \cdot \overline{z}_{out}; i = 1, 2^{n},$$

(2.7)

Введём входной сигнал d вместо z, получим:

$$\overline{d}_{out.i} = \mathop{\&}_{j=1}^{n} x_{j}^{\sigma(i-1,j)} \cdot \overline{d}_{in}; i = 1, 2^{n},$$

(2.8)

Но при реализации (2.6) в виде дерева передающих транзисторов нарушается условие ортогональности сигналов, так как в случае не активации одного из передающих транзисторов вход одного из инверторов получается «оборванным». Ортогональность обеспечивается  $(\bar{d}_{\it in}=1)$  в случае:

$$d_{out.i} = & (x_j^{\sigma(i-1,j)} \lor x_j^{\sigma(i-1,j)}); i = 1, 2^n.$$

(2.9)

Причём, в отличие от обеспечения ортогональности в известном LUT, где сигналы со всех ветвей дерева «собираются» на одном выходе, что привело бы к выражению обеспечения ортогональности по выходу всей цепочки:

$$d_{out,i} = \&(x_j^{\sigma(i-1,j)}) \vee \&(x_j^{\overline{\sigma}(i-1,j)}); i = 1,2^n,$$

(2.10)

Выражение (2.7) описывает обеспечение ортогональности по каждой переменной в каждой ветви дерева.

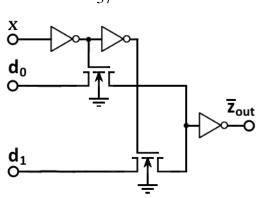

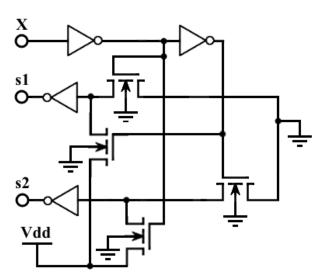

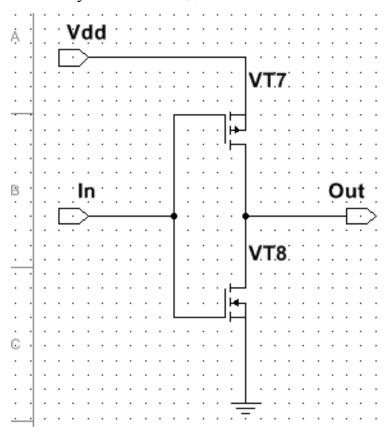

Выражение (2.5) представляет собой мультиплексор 2-1 и может быть реализовано в виде элементарного дерева с управляемыми переменной X ветвями - рисунок 2.1:

Рисунок 2.1. Элементарный LUT на одну переменную (1-LUT), настроенный на вычисление функции «не X»

Элементарный DC LUT - на одну переменную (1- DC LUT) получается путём передачи сигнала в элементарном 1- LUT в другом направлении — получаем дешифратор (DC)- рисунок 2.2:

Рисунок 2.2. Элементарный DC LUT - на одну переменную (1- DC LUT) Для рисунка 2.2 получим:

$$\overline{d}_{out.0}(x) = \overline{x};$$

$$\overline{d}_{out.1}(x) = x.$$

(2.11)

Если исключить инвертор на входе, получим- рисунок 2.3:

Рисунок 2.3. Элементарный 1-DC 1LUT - на одну переменную без входного инвертора

Тогда ноль передаётся либо на выход 0 (набор 0, X=0), либо на выход 1 (набор 1, X=1). Как окажется в дальнейшем, удобней активная единица на выходе, поэтому вводим инверторы- рисунок 2.4

Рисунок 2.4. Элементарный 1-DC LUT - на одну переменную с выходными инверторами, активная единица

Выражению (2.9) обеспечения ортогональности при n=1 соответствует схема на рисунке 2.5:

Рисунок 2.5. Элементарный дешифратор без инверторов на выходах и с обеспечением ортогональности сигналов на выходах s1, s2

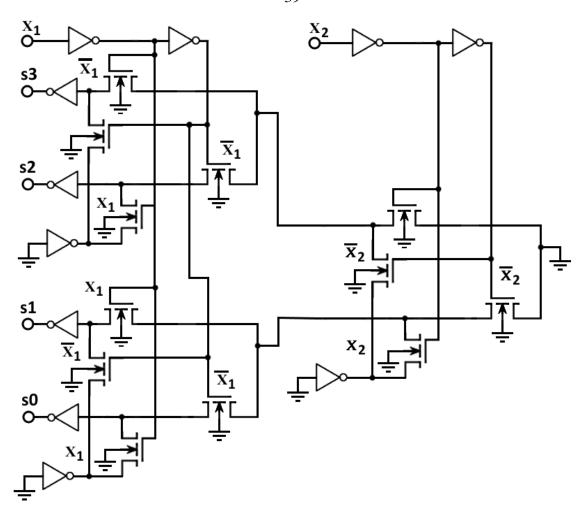

Рассмотрим предлагаемую реализацию DC LUT [56] от большего числа переменных и особенности отказоустойчивой их реализации с учётом ограничений Мида-Конвей на число транзисторов в последовательной цепочке [62].

С учётом схемы на рисунке 2.5 дешифратор 2- DC LUT будет реализован следующим образом [56] – рисунок 2.6:

Рисунок 2.6. Дешифратор на две переменные с обеспечением ортогональности сигналов по выходам 0,1,2,3

Здесь, в отличие от LUT, используется локальная ортогональность — в каждом элементарном дешифраторе. Оба дополнительных транзистора активированы, но на вход инвертора по выходу 3 поступает логическая единица только через  $x_1$  поскольку  $x_1$  закрыт.

На наборе 01 на вход инвертора по выходу 3 поступает логическая - единица через  $x_1$  поскольку  $x_1$  закрыт, а через  $x_2$  идёт ноль, но не доходит.

На наборе 10 на вход инвертора по выходу 3 поступает логическая единица через  $x_2$  и  $x_1$  поскольку  $x_1$  открыт, а  $x_2$  закрыт. Для «ортогонализации» по одной переменной можно использовать один инвертор, в отличие от того, что представлено на рисунке 2.7:

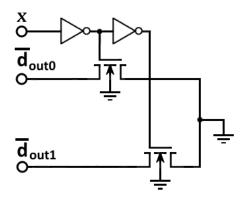

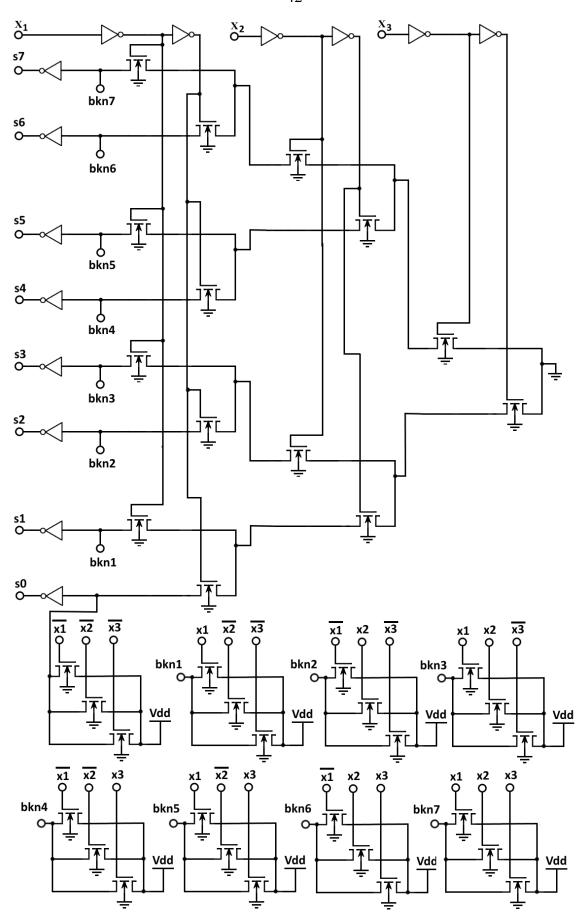

Рисунок 2.7. Дешифратор на три переменные с обеспечением ортогональности сигналов по каждому передающему транзистору Если отказаться от инверторов по цепям ортогональности, получим схему на рисунке 2.8:

Рисунок 2.8. Дешифратор на три переменные с обеспечением ортогональности сигналов по выходам 0,1,2,3,4,5,6,7 по каждому транзистору с коммутацией шин «Ноль вольт» и «Vdd»

Дешифратор на три переменные с обеспечением ортогональности сигналов на выходах 0,1,2,3,4,5,6,7 изображён на рисунок 2.9:

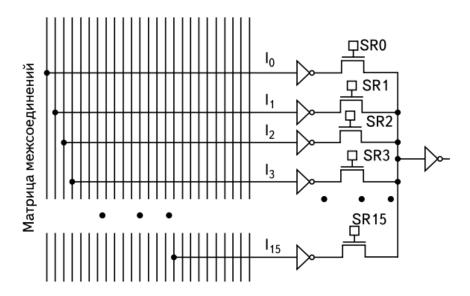

Предлагается блок дизъюнкций конституент логической функции - рисунок 2.10:

Рисунок 2.9. Дешифратор на три переменные с обеспечением ортогональности сигналов на выходах S 0,1,2,3,4,5,6,7.

Рисунок 2.10. Схема блока дизъюнкций конституент логической функции

Активные единицы с выхода DC LUT открывают один из транзисторов блока на рисунке 2.10, а настройка H — инверсная должна быть записана? в соответствующих ячейках ОЗУ (SRAM). Таким образом обеспечивается ортогональность и путь прохождения сигнала по сравнению с LUT увеличивается на два транзистора в блоке рисунок 2.10 - один передающий, другой в выходном инверторе.

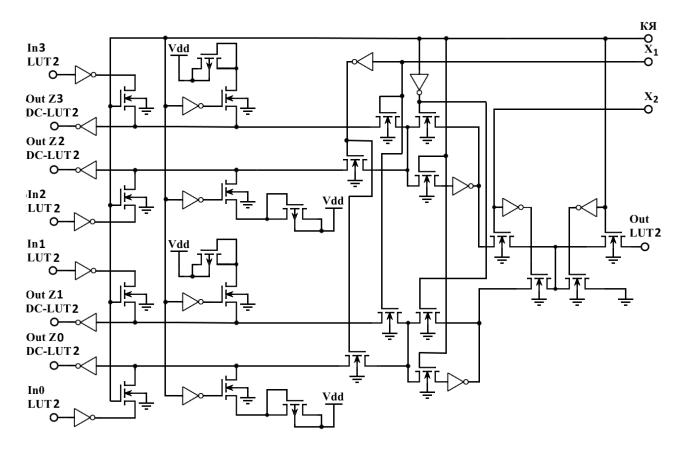

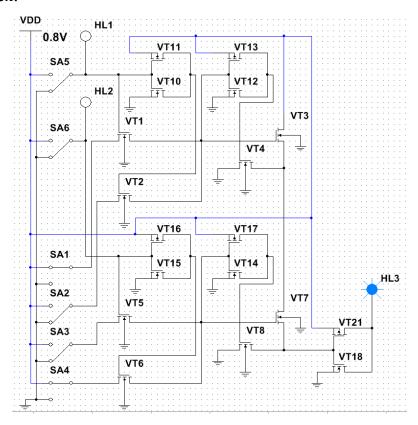

#### 2.2. Разработка адаптивного логического элемента

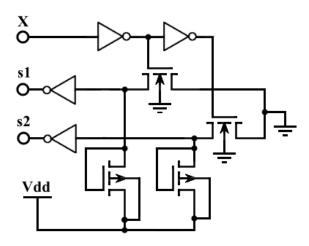

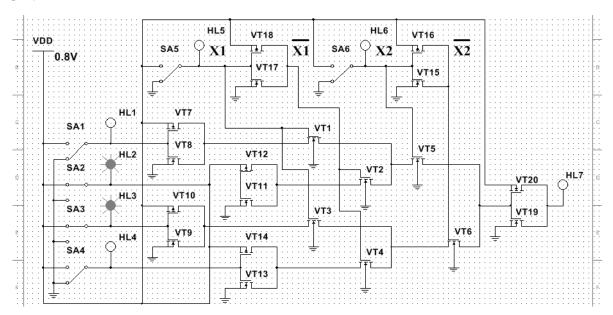

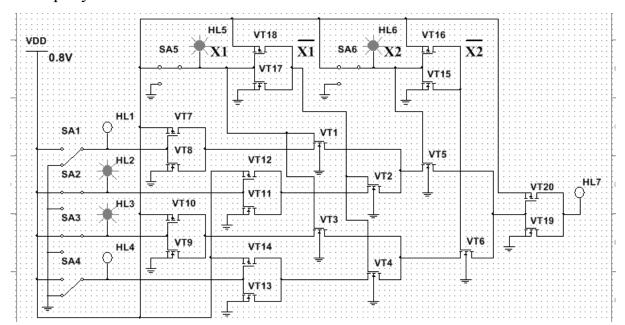

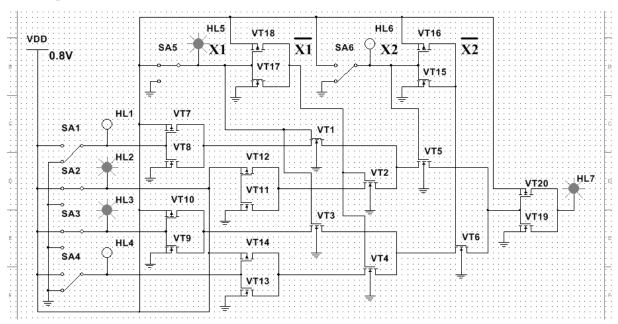

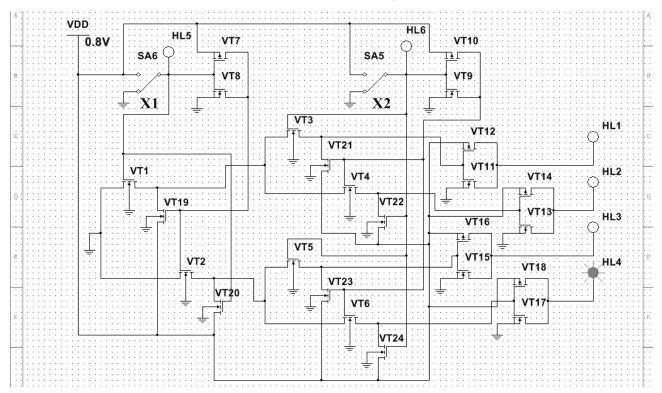

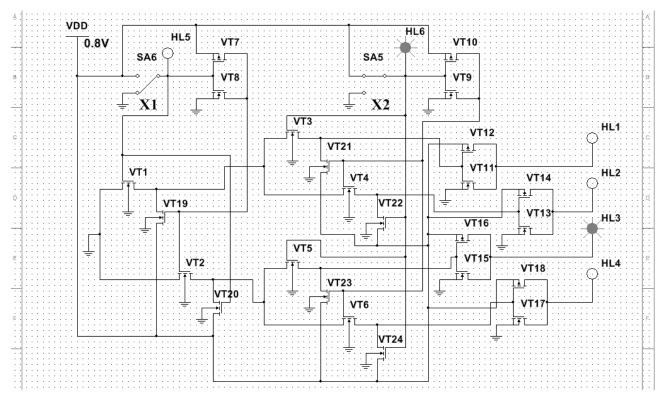

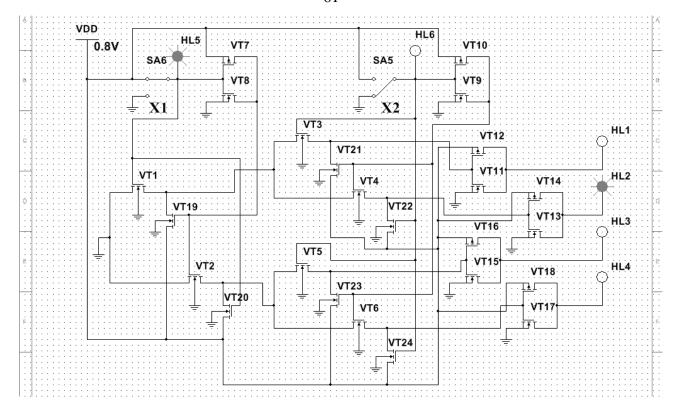

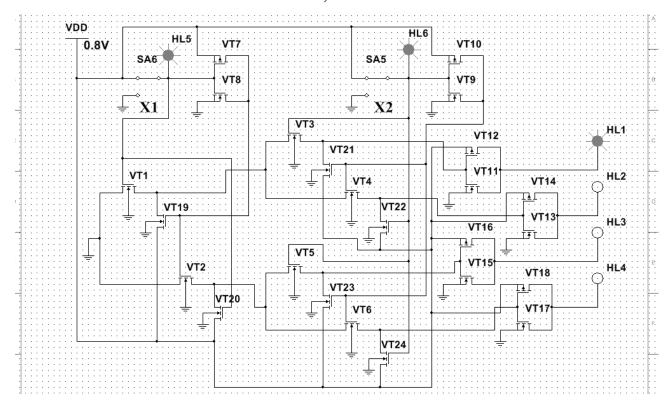

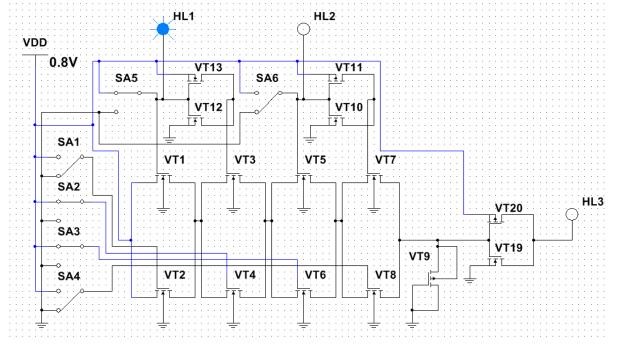

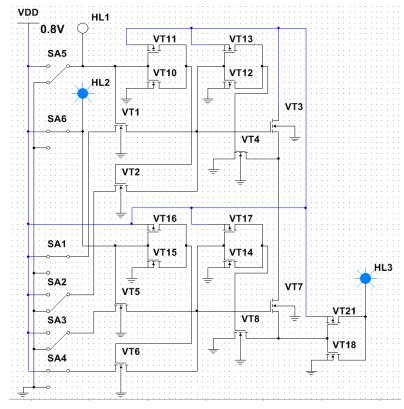

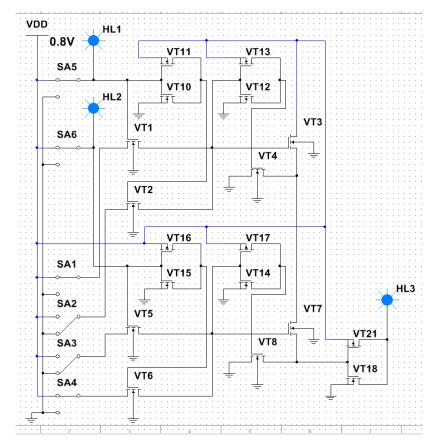

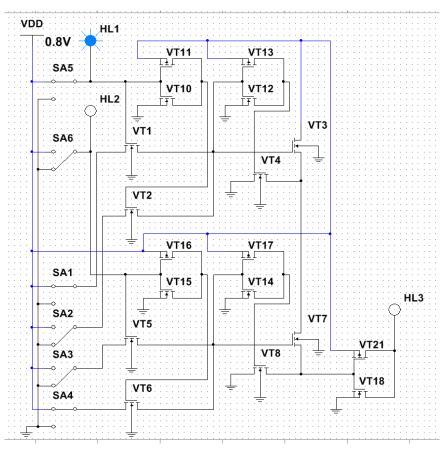

Вариант DC LUT (для n=1) с  $d_{in}=0$  и активной логической единицей на двух выходах без транзисторов ортогональности, с резисторами по выходам изображён на рисунке 2.11.

Рисунок 2.11 Элементарный DC LUT с восстановителями сигнала по выходам цепочки передающих транзисторов

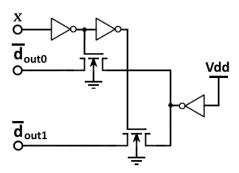

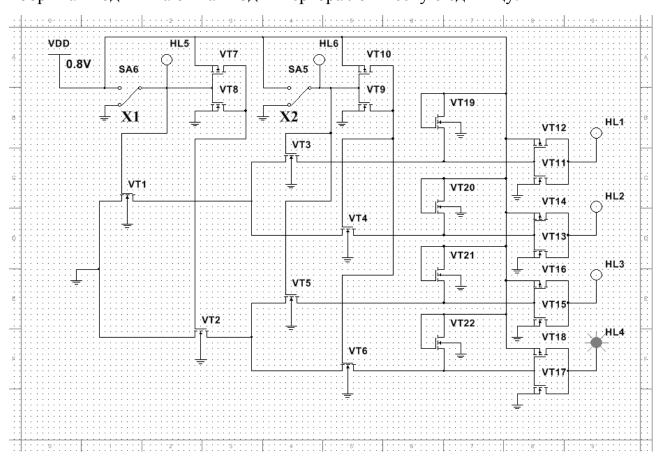

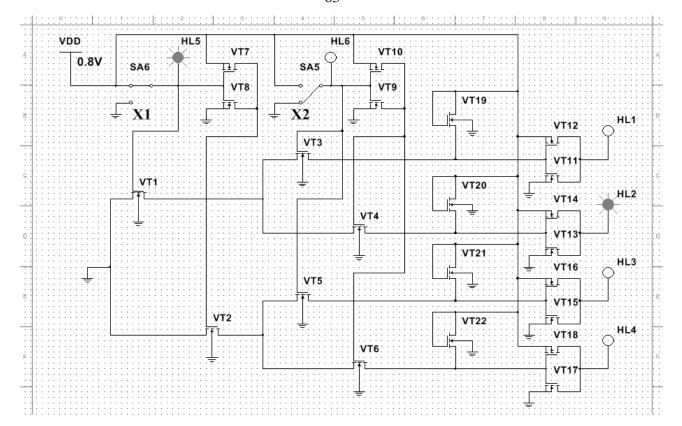

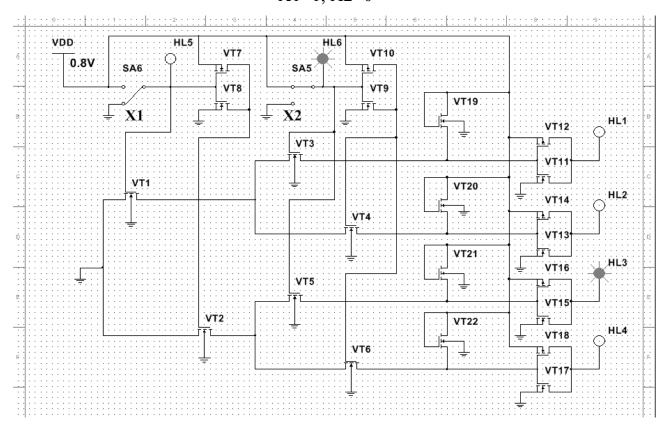

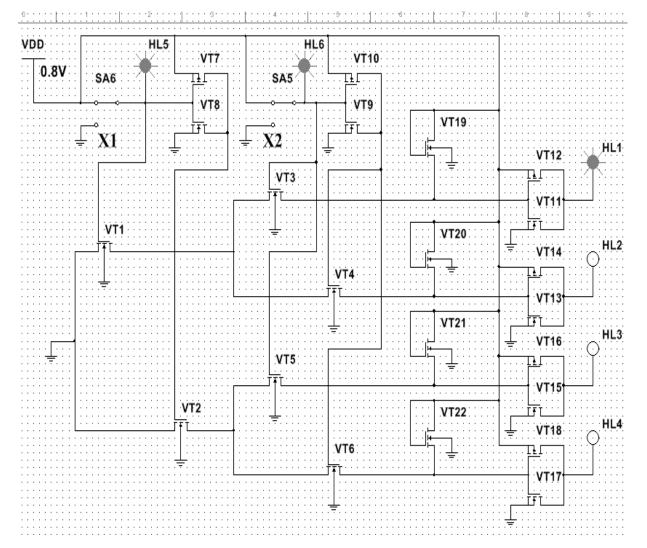

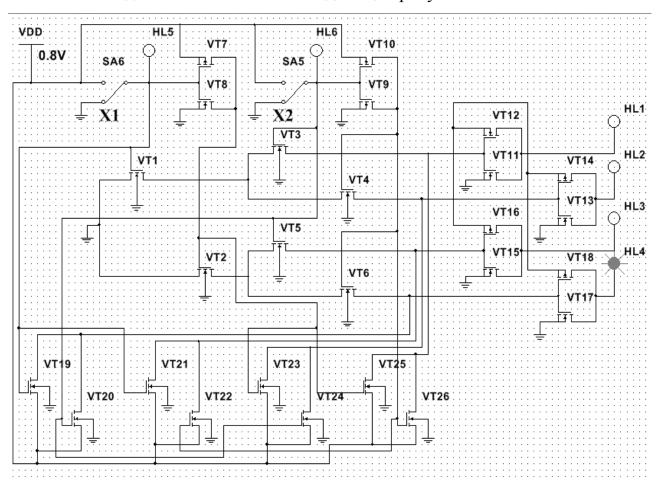

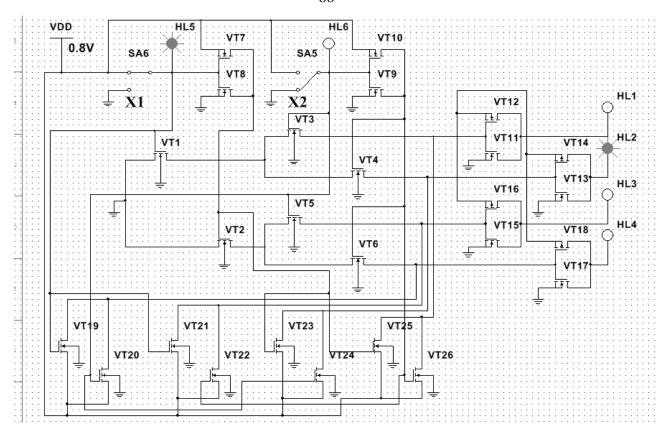

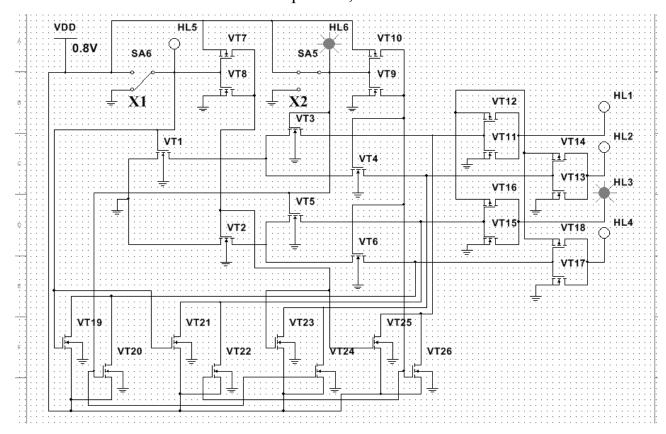

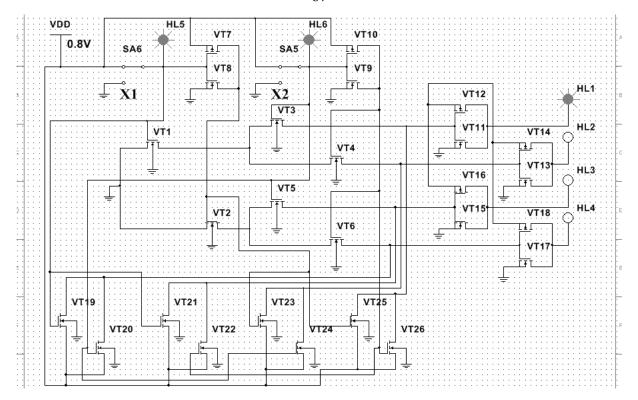

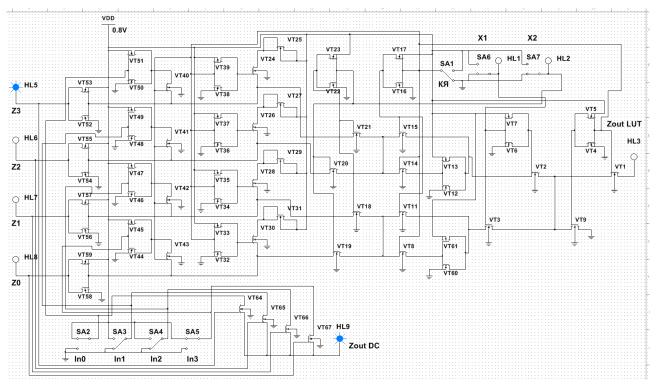

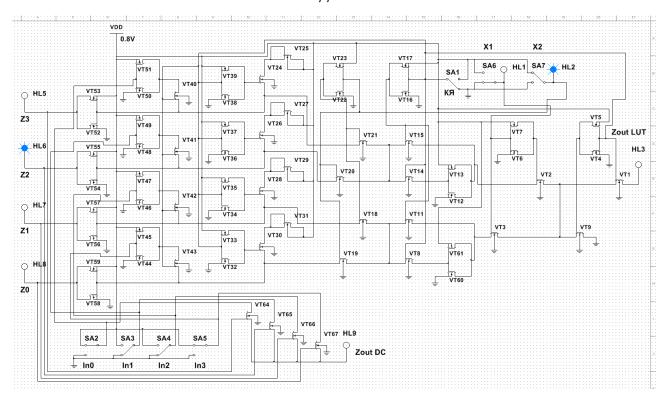

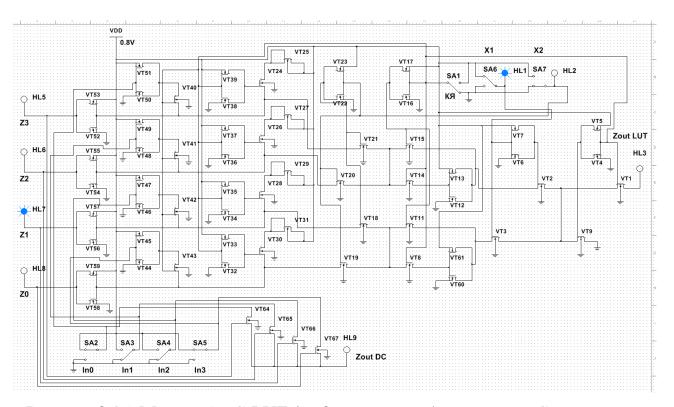

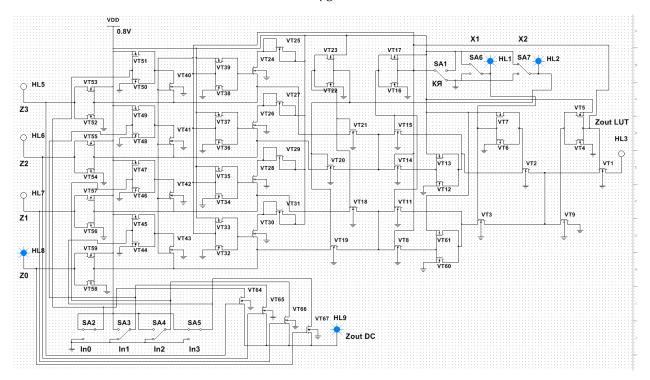

На основе схемы на рисунке 2.11 построим адаптивный элемент [63]. Такой предлагаемый элемент может в зависимости от настройки реализовать либо LUT, либо DC LUT. Настройка дерева на реализацию дешифратора осуществляется конфигурационной константой s:

$$\begin{array}{c} - \bar{x}_{n-2} - \bar{x}_{1} \cdot (\bar{s} \cdot d_{2n-1} \vee s \cdot [=z_{0}]) \\ x_{n} - \bar{x}_{n-2} \dots x_{2} x_{1} \cdot (\bar{s} \cdot d_{2n-1+1} \vee s \cdot [=z_{1}]) \\ x_{n} - \bar{x}_{n-2} \dots x_{2n-1} x_{n-2} \\ - \bar{x}_{n-2} \dots x_{2n-1} x_{n-2} \\ - \bar{x}_{n-1} x_{n-2} \\ x_{n-1} x_{n-2} \dots x_{2n-1-1} \vee s \cdot [=z_{2n-2}]) \\ x_{n-1} x_{n-2} \dots x_{2n-1-1} \vee s \cdot [=z_{2n-1}]). \end{array}$$

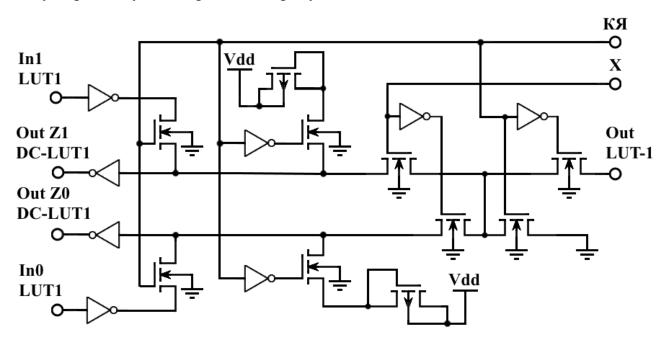

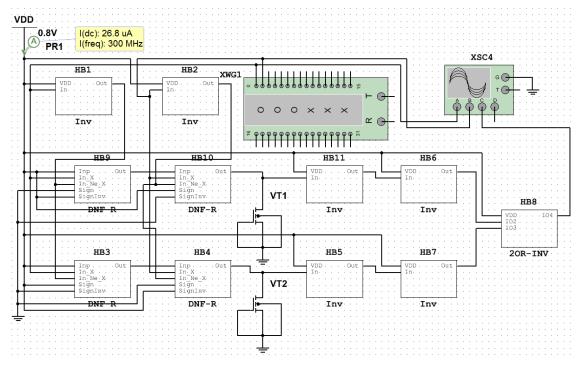

Реализация дизъюнкций (функций) осуществляется подключением выходов (2.12) к блокам, реализующим выражения (2.4). Схема ADC LUT на одну переменную изображена на рисунке 2.12.

Рисунок 2.12. Схема ADC 1-LUT (на одну переменную), информация из КЯконфигурационной ячейки

Рисунок 2.13. Схема ADC 2-LUT (на две переменных), информация из КЯконфигурационной ячейки

Таким образом, дополнительные коммутации возникают в «точках сочленения» дерева, если выполняется декомпозиция. Если её нет (на рисунке 2.13, её не будет, если исключить транзисторы, соединяющие поддеревья по х1 с поддеревом по х2), то дополнительные коммутации не нужны, остаются коммутации по входу и по выходам дерева. Это возможно до n=3. Эти результаты следует учесть при исследовании оценок сложности адаптации LUT для последующей оценки технико-экономической эффективности. Конкретная реализация коммутаций возможна на основе известных подходов к построению коммутаторов локальных матриц связей. То есть используются штатные коммутаторы, дополнительные инверторы и транзисторы. Кроме того, полученные сигналы значений конъюнкций могут быть использованы для настройки входов других LUT для реализации более сложных конъюнкций. Иначе, их можно подключать ко входам переменных других

LUT, например, для реализации дизъюнкций, в противном случае необходима реализация дополнительных блоков ИЛИ.

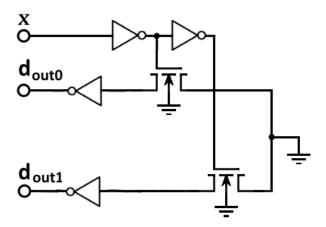

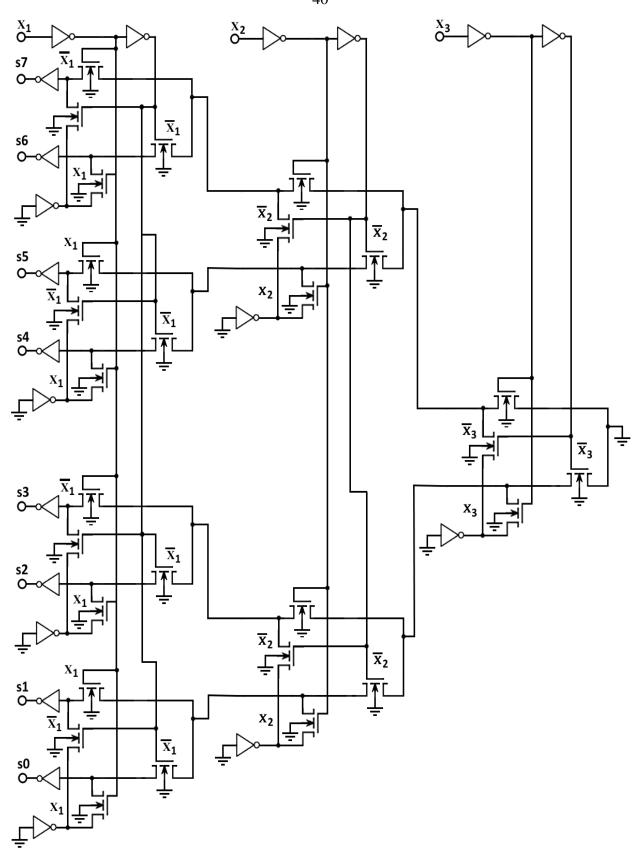

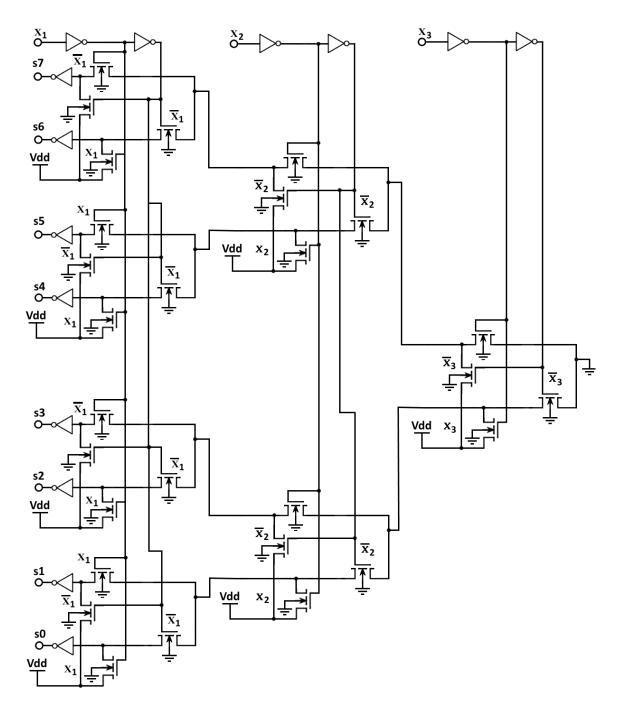

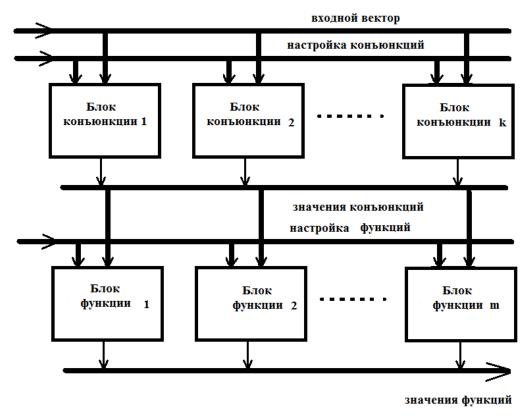

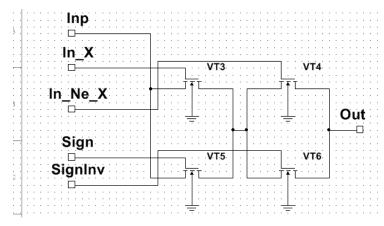

# 2.3. Усовершенствованный метод реализации в FPGA систем логических функций, заданных в ДНФ

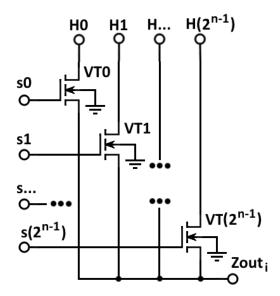

Рассмотрим реализацию вычисления логических функций в ДНФ на основе программируемых логических матриц (ПЛМ) и в ПЛИС типа CPLD (Complex Programmable Logic Device) [16, 64]. Программирование по i-ой переменной j-ой конъюнкции, зависящей от одной, переменной, с учётом её возможного инверсного значения, может быть представлено следующим образом:

$$y_i(x_n...x_2x_1) = (x_i \lor s_{i,i})(\bar{x}_i \lor \bar{s}_{i,i})$$

(2.13)

Для j-ой конъюнкции от n переменных, получим:

$$y_{j} = \underset{i=1}{\overset{n}{\&}} (x_{i} \vee s_{j,i}) (\bar{x}_{i} \vee \bar{s}_{j,i}), j = 1,k$$

(2.14)

Причём, для настройки s выполняются следующие условия:  $s_{j,i}\bar{s}_{j,i}=0; s_{j,i}\sqrt{s}_{j,i}=1$  для существенной переменной j-ой конъюнкции,  $s_{j,i}\bar{s}_{j,i}=1$  для не существенной переменной.

Программирование дизъюнкций (значений функций) может быть описано выражением аналогичным (2.13). Тогда матрица И (AND array) может быть представлена следующим образом:

$$y_{1}(x_{n}x_{n-1}...x_{2}x_{1}) = \frac{x_{n}}{s_{1,n}} \cdot \frac{\overline{x}_{n}}{\overline{s}_{1,n}} \bullet \frac{x_{n-1}}{s_{1,n-1}} \cdot \frac{\overline{x}_{n-1}}{\overline{s}_{1,n-1}} \bullet .... \frac{x_{2}}{s_{1,2}} \cdot \frac{\overline{x}_{2}}{\overline{s}_{1,2}} \bullet \frac{x_{1}}{s_{1,1}} \cdot \frac{\overline{x}_{1}}{\overline{s}_{1,1}}$$

$$y_{2}(x_{n}x_{n-1}...x_{2}x_{1}) = \frac{x_{n}}{s_{2,n}} \cdot \frac{\overline{x}_{n}}{\overline{s}_{2,n}} \bullet \frac{x_{n-1}}{s_{2,n-1}} \cdot \frac{\overline{x}_{n-1}}{\overline{s}_{2,n-1}} \bullet .... \frac{x_{2}}{s_{2,2}} \cdot \frac{\overline{x}_{2}}{\overline{s}_{2,2}} \bullet \frac{x_{1}}{s_{2,1}} \cdot \frac{\overline{x}_{1}}{\overline{s}_{2,1}}$$

$$y_{j}(x_{n}x_{n-1}...x_{2}x_{1}) = \frac{x_{n}}{s_{j,n}} \cdot \frac{\overline{x}_{n}}{\overline{s}_{j,n}} \bullet \frac{x_{n-1}}{s_{j,n-1}} \cdot \frac{\overline{x}_{n-1}}{\overline{s}_{j,n-1}} \bullet .... \frac{x_{2}}{s_{j,2}} \cdot \frac{\overline{x}_{2}}{\overline{s}_{j,2}} \bullet \frac{x_{1}}{s_{j,1}} \cdot \frac{\overline{x}_{1}}{\overline{s}_{j,1}}$$

$$y_{k}(x_{n}x_{n-1}...x_{2}x_{1}) = \frac{x_{n}}{s_{k,n}} \cdot \frac{\overline{x}_{n}}{\overline{s}_{k,n}} \bullet \frac{x_{n-1}}{s_{k,n-1}} \cdot \frac{\overline{x}_{n-1}}{\overline{s}_{k,n-1}} \bullet .... \frac{x_{2}}{s_{k,2}} \cdot \frac{\overline{x}_{2}}{\overline{s}_{k,2}} \bullet \frac{x_{1}}{s_{k,1}} \cdot \frac{\overline{x}_{1}}{\overline{s}_{k,1}},$$

$$(2.15)$$

где ·-последовательное соединений по данной переменной; •последовательное соединений по разным переменным; —-параллельное соединение переменной и настройки.

Матрица ИЛИ (OR array) может быть описана следующим образом:

$$f_{1}(x_{n}x_{n-1}...x_{2}x_{1}) = y_{1}(x_{n}x_{n-1}...x_{2}x_{1})q_{1.1} \lor y_{2}(x_{n}x_{n-1}...x_{2}x_{1})q_{1.2} \lor .... \lor y_{k}(x_{n}x_{n-1}...x_{2}x_{1})q_{1.k}$$

$$f_{2}(x_{n}x_{n-1}...x_{2}x_{1}) = y_{1}(x_{n}x_{n-1}...x_{2}x_{1})q_{2.1} \lor y_{2}(x_{n}x_{n-1}...x_{2}x_{1})q_{2.2} \lor .... \lor y_{k}(x_{n}x_{n-1}...x_{2}x_{1})q_{2.k}$$

$$\vdots$$

$$f_{\mu}(x_{n}x_{n-1}...x_{2}x_{1}) = y_{1}(x_{n}x_{n-1}...x_{2}x_{1})q_{\mu,1} \lor y_{2}(x_{n}x_{n-1}...x_{2}x_{1})q_{\mu,2} \lor .... \lor y_{k}(x_{n}x_{n-1}...x_{2}x_{1})q_{\mu,k}$$

$$\vdots$$

$$f_{m}(x_{n}x_{n-1}...x_{2}x_{1}) = y_{1}(x_{n}x_{n-1}...x_{2}x_{1})q_{m,1} \lor y_{2}(x_{n}x_{n-1}...x_{2}x_{1})q_{m,2} \lor .... \lor y_{k}(x_{n}x_{n-1}...x_{2}x_{1})q_{m,k},$$

$$(2.16)$$

где  $q_{\mu,j}$ ;  $\mu = \overline{1,m}$  -настройка вхождения конъюнкций в m функций.

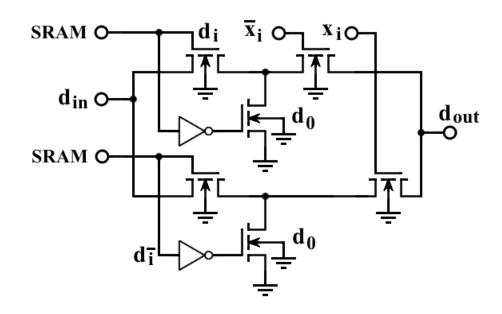

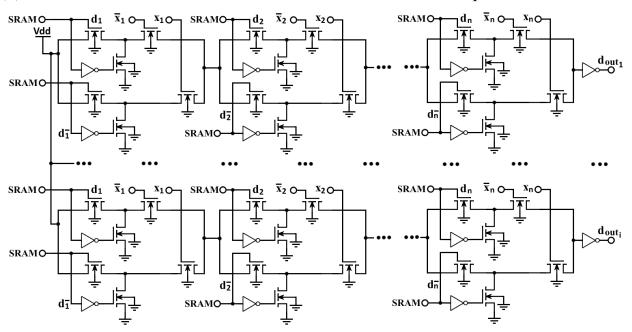

В качестве альтернативы ПЛМ CPLD (рисунок 2.14), где ортогональность по переменным не обеспечивается, а используется «подтягивающий» резистор, предлагается программирование с обеспечением ортогональности на основе выражения:

$$s_{i} = (d_{SRAM,i} \ d_{in} \lor \overline{d}_{SRAM,i} \ d_{0}) \ x_{i} \lor (d_{SRAM,i} \ d_{in} \lor \overline{d}_{SRAM,i} \ d_{0}) \ \overline{x}_{i}; i=n. \quad (2.17)$$

В выражении (2.17)  $d_{SRAM.i}$ ,  $d_{SRAM.i}$ , - настройка вхождения і-ой переменной из п переменных в ј-ую конъюнкцию системы из т функций;  $d_{in}$  -входная константа, которая должна формироваться при «правильном» значении переменной, либо её несущественности;  $d_0$  -признак того, что заданная переменная имеет «неправильное» значение. Этот признак передаётся дальше, он участвует в формировании значения конъюнкции.

Суть в том, что в случае несущественности переменной, значение выражения (2.17) было бы эквивалентно значению выражения при правильном, заданном значении переменной. То есть, если  $d_{SRAM.i} = 1; d_{SRAM.i} = 0$ , переменная существенна и должна быть равна 1 (без инверсии), при

$d_{SRAM.i} = 0; d_{SRAM.i} = 1,$  переменная существенна и должна быть равна 0 (с инверсией), при  $d_{SRAM.i} = 1; d_{SRAM.i} = 1$ , переменная не существенна. Значения  $d_{SRAM.i} = 0; \overline{d}_{SRAM.i} = 0$ , запрещены. Рассмотрим пример. Пусть і-я переменная должна быть 1. Настройка для этого случая приведена в Таблице 2.1:

Таблица 2.1. Задание значения 1 для і-ой переменной

| $d_{SRAM.i}$ | d <sub>SRAM.i</sub> | d <sub>in</sub> | $\mathbf{d}_0$ | X i | —<br>X i | Si |

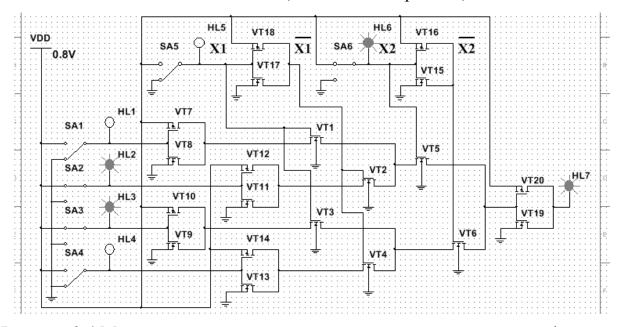

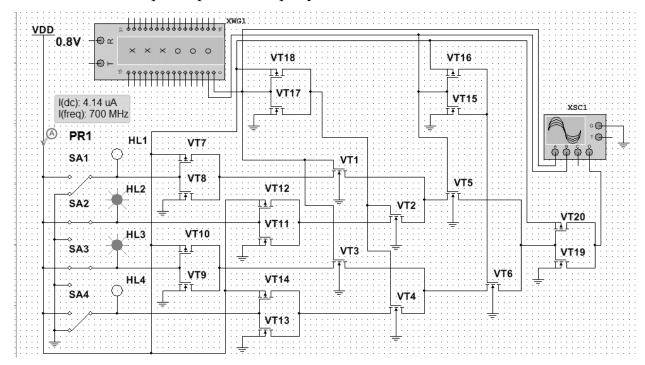

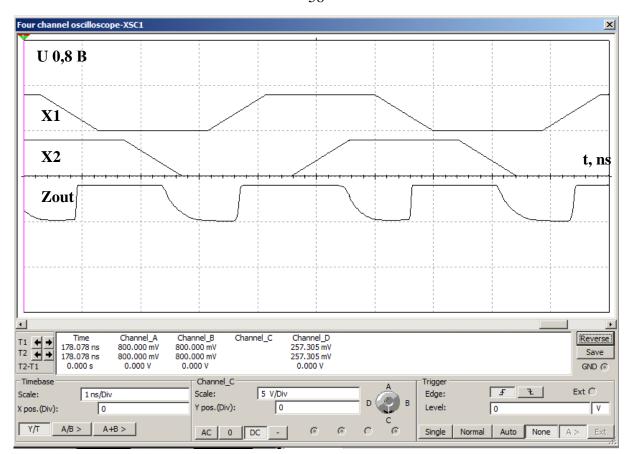

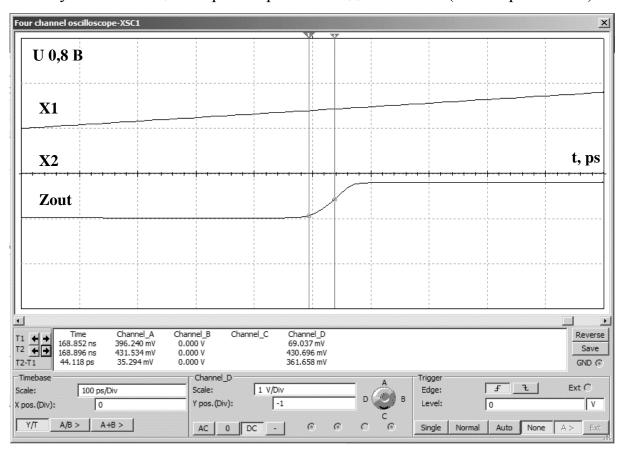

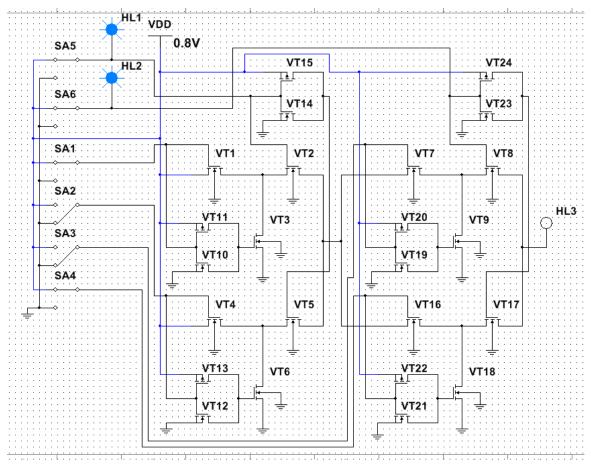

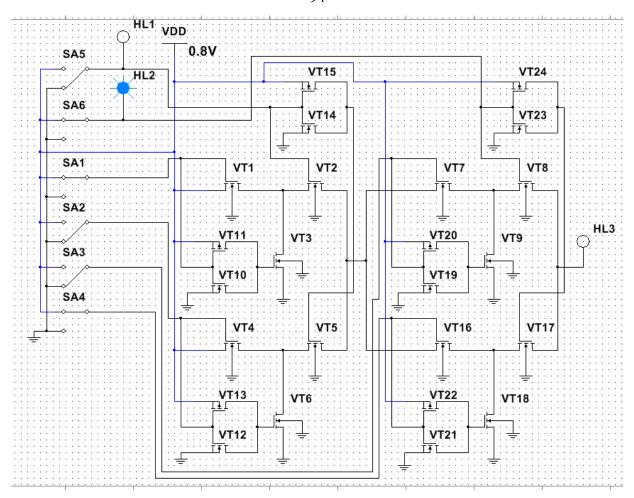

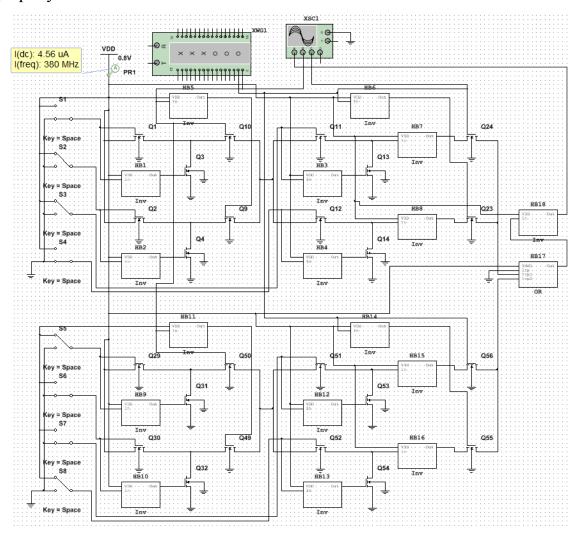

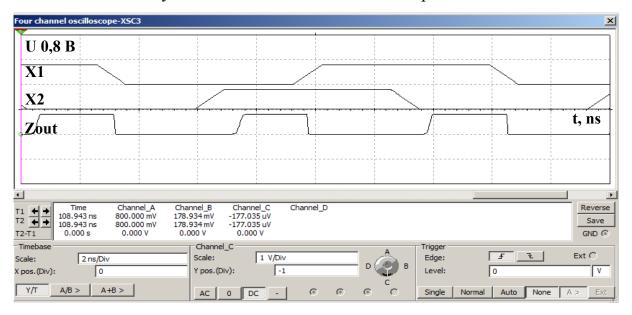

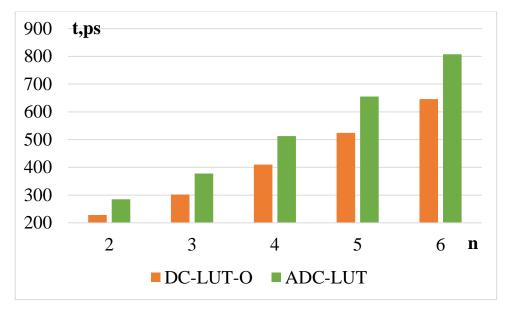

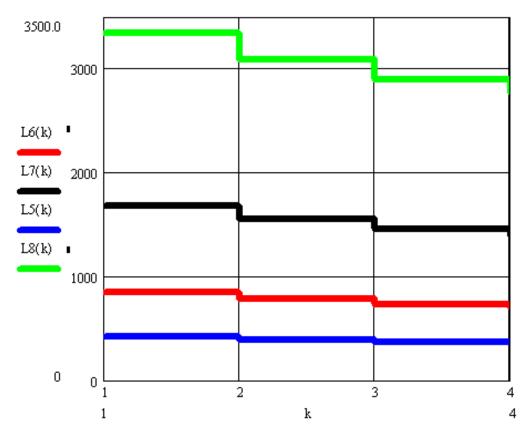

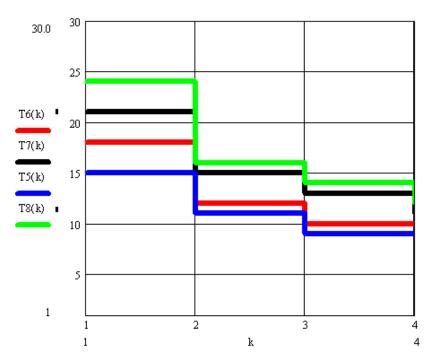

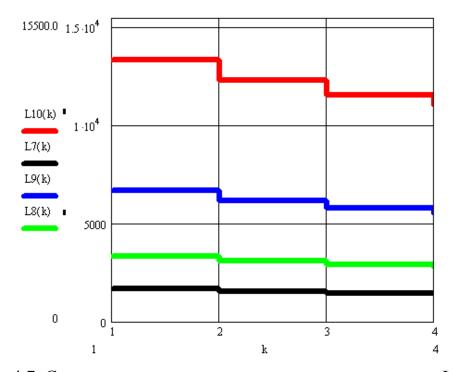

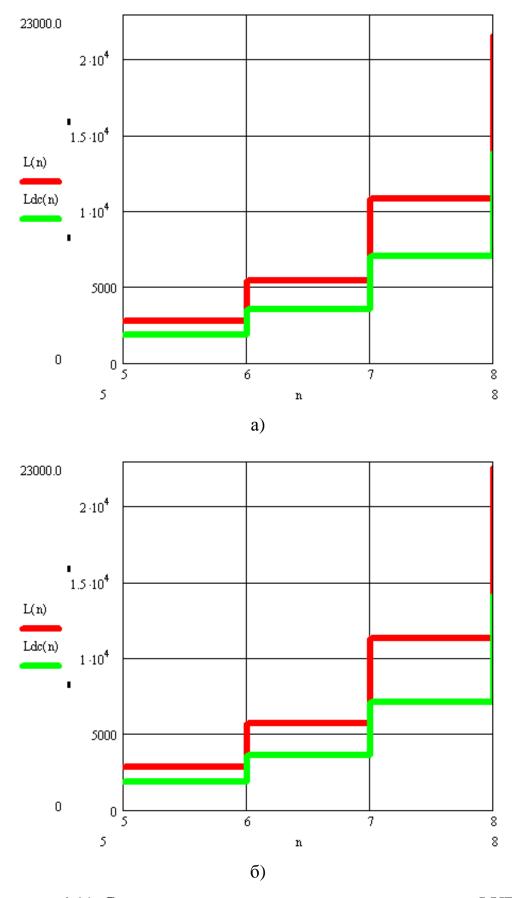

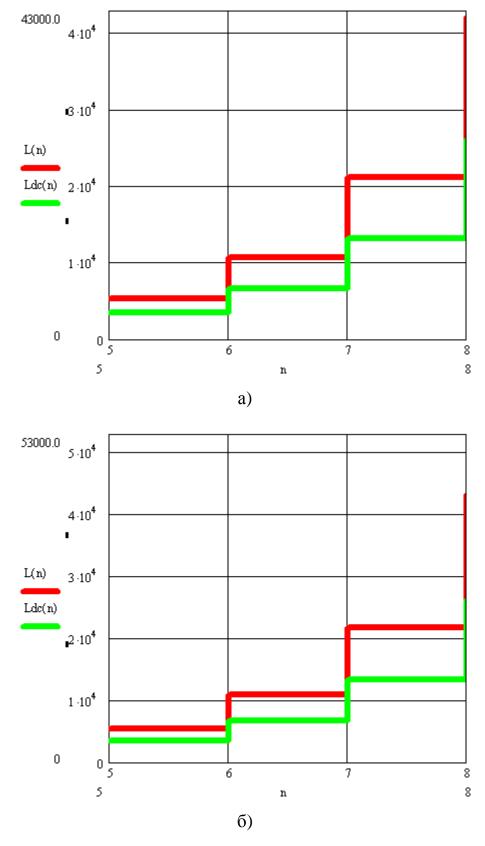

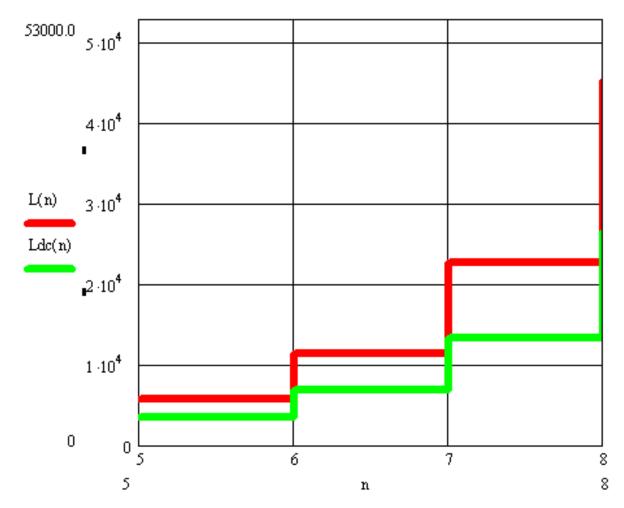

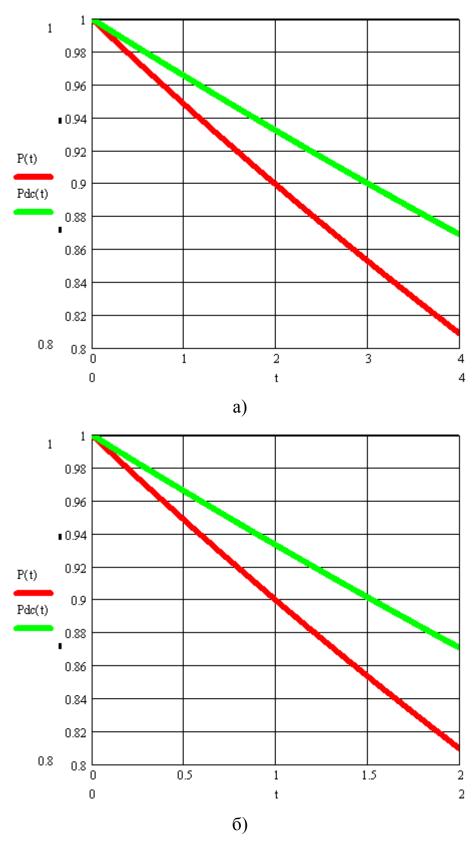

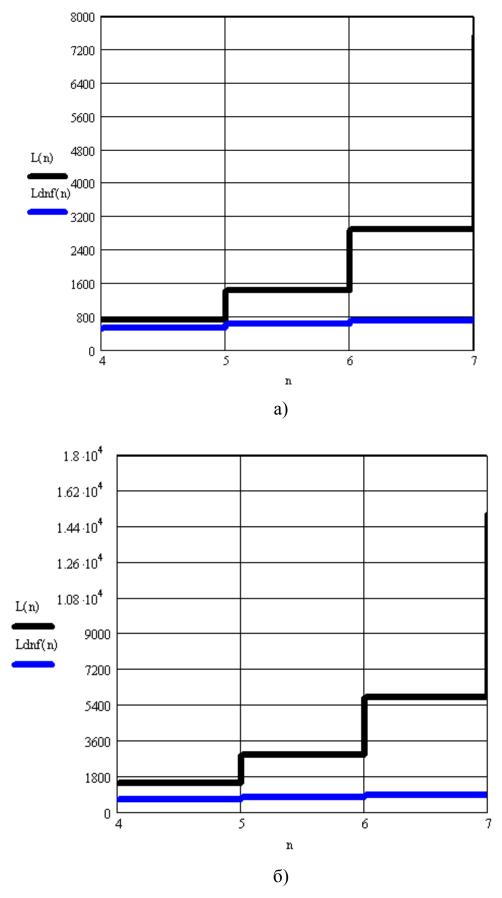

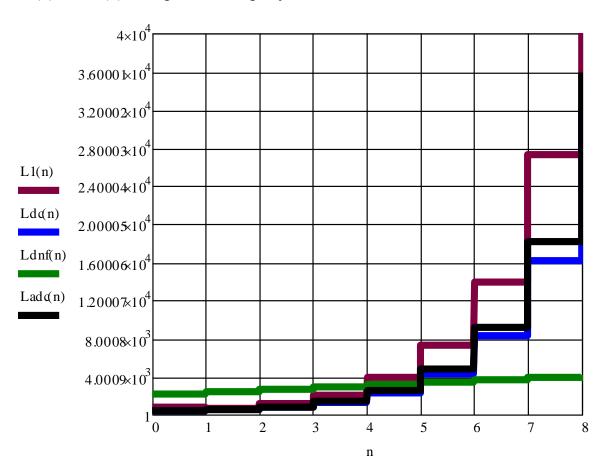

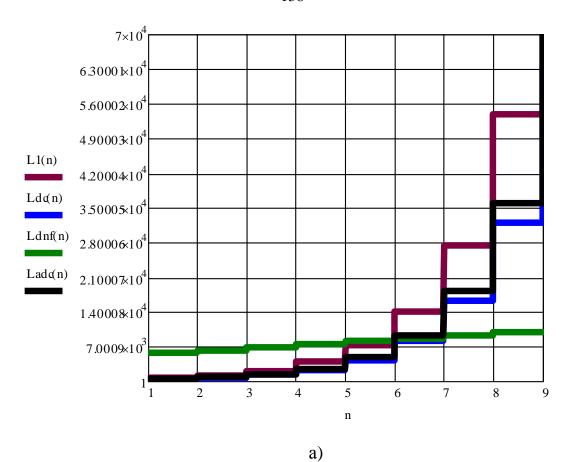

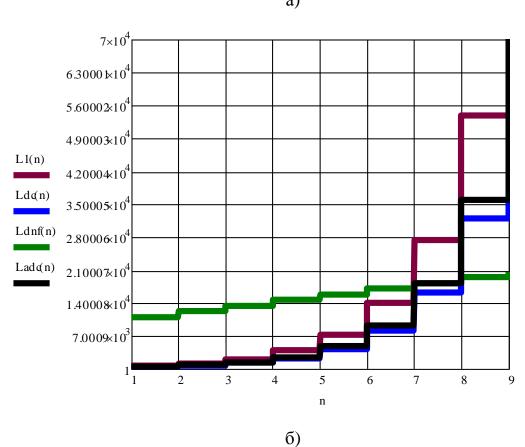

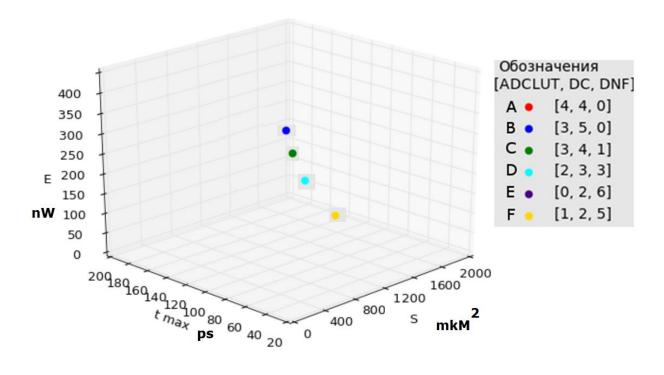

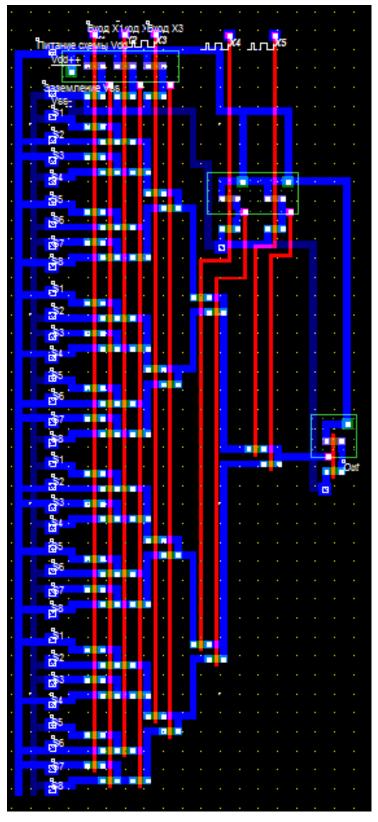

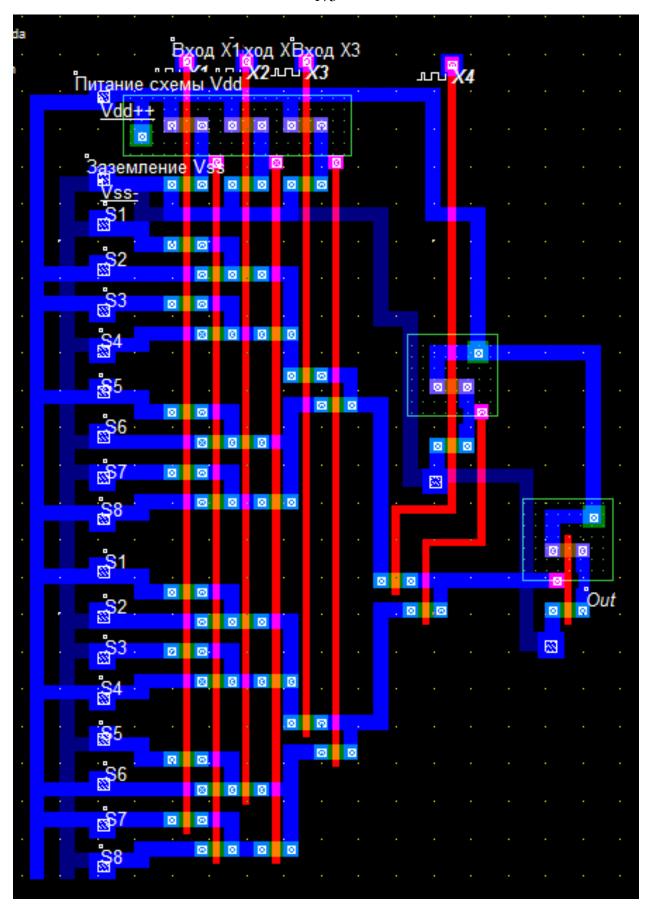

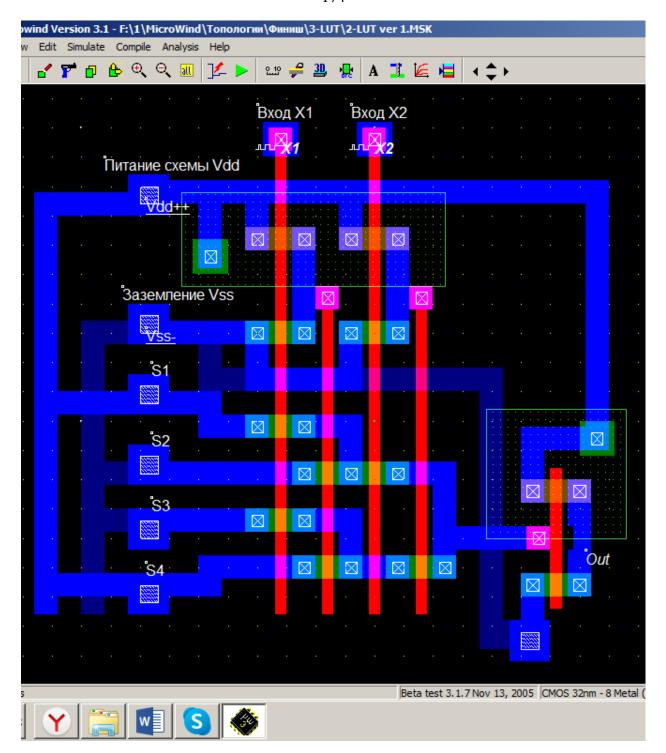

|--------------|---------------------|-----------------|----------------|-----|----------|----|